我们经常遇到的问题就是:我应该怎么加载我定义的class,是用import的方式还是include的方式?

为了解答这个问题,首先应该对systemverilog的类型机制有更多的了解,特别是强弱类型转换机制(strong and weak typing)。

在编程语言中,相反于在不同类型之间的显式转换,我们称隐式或者临时的转换为弱类型转换。举个栗子,对于verilog的bit向量,或者integral类型,适当地增加或者减小数值的位宽就是一种弱类型转换。如果你将一个7bit的数据和一个8bit的数据相加,verilog会在7bit数据的最高位前面填充1bit的0,并且返回一个8bit的结果。相反,如果使用的是VHDL,你必须显式地声明7bit数前的1bit填充,或者将8bit的数截断,因为你需要保证你的表达式的两个数位宽相等。

除开极少数的例外,在systemverilog里面其它的类型转换都遵守强类型转换的规则。强类型转换指的是在不同类型之间的显式转换或者强制类型转换。理解systemverilog中的等价类型是理解使用import还是include的关键。

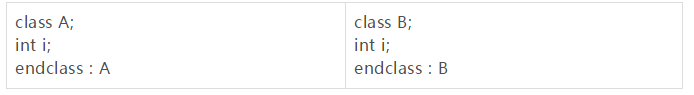

除开继承,systemverilog仅使用类型的名称来判断class是否是等价的。再举个栗子,假设我定义class A和class B如下:

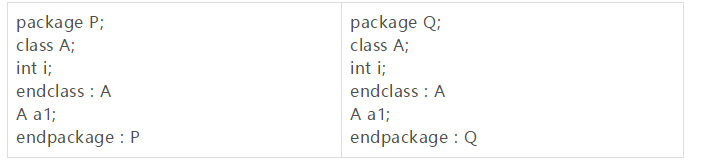

尽管它们的内容结构完全一样,systemverilog还是会认为这两个class不是等价的,因为它们的class name不一样。class name不仅仅只是只是A和B,它还包含了类定义时声明的作用范围。当你在package内定义了一个class,这个package的名字将会作为前缀添加在class name前面。

现在我们有了关于class A的两个定义,一个叫P::A,另一个叫Q::A。因此变量P::a1和Q::a1是不同的类型。我们使用include语句重写上面的栗子,得到的结果仍然是一样的——两个不同的类定义。

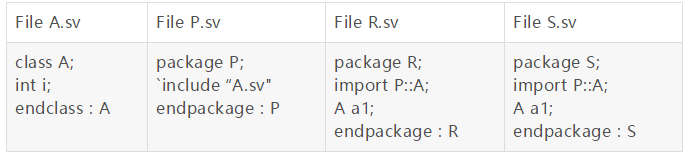

在package里面,采用include的方式添加了class A的定义,但是这样你得到的仍然是class A的两种定义。include只是文本的一种快捷复制粘贴方式而已。而采用import方式不会重复复制文本,它会扩大定义的作用范围。

class A在package P里面声明(有且仅有package P声明了),因此变量R::a1和S::a1是同一种类型,都是P::A的类型。事实上class A通过include的方式添加到package里面,这件事情只发生了一次,一旦include进去的文本被展开,就和File A.sv没有什么关系了。

当你编译时提示你类型不兼容时,尽管它们看起来似乎是一样的。那么你就需要确认类型作用的范围。在module内定义的class会把module例化名称作为类型的前缀。所以相同的module例化多份,结果是会创建多个不同的class name,且全部不兼容。

作者:kevindas

原文链接:https://mp.weixin.qq.com/s/0eakHViTFQVEychQ_ozYcg

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏