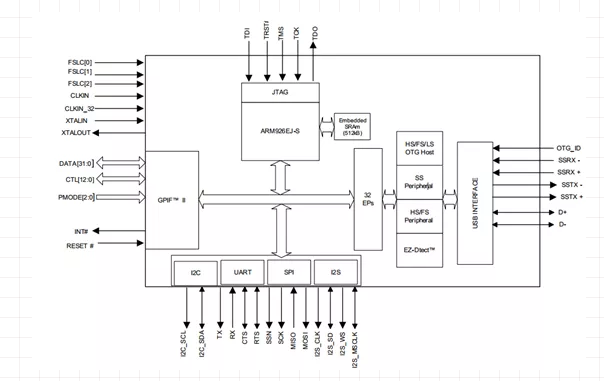

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写控制即可,同时该芯片还具有ARM核+I2S、I2C、SPI、UART等接口,大大增加了该芯片的使用范围。

芯片介绍

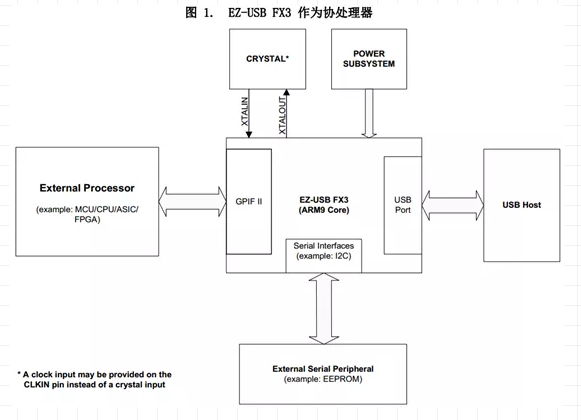

下面是整个芯片的框图:

主要包括以下几个部分:

1、通用可编程接口 (GPIF II)

可编程的 100-MHz GPIF II 接口能连接多种类型外部器件

8/16/32 位数据总线

多达 16 种可配置的控制信号

2、32 位 CPU

运行频率为 200 MHz 的 ARM926EJ 内核

512 KB 嵌入式 SRAM

3、外设

频率为 1 MHz 的 I2C 主控制器

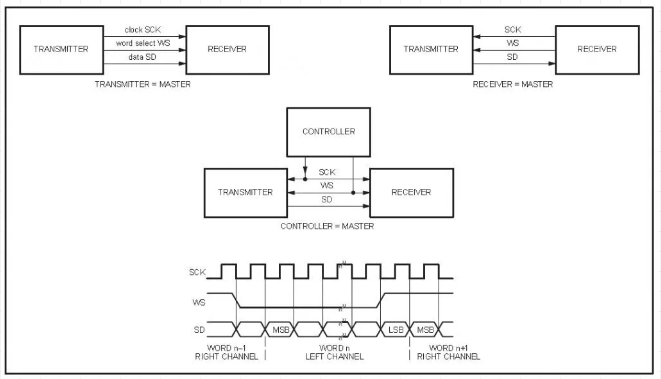

采样频率为 32 kHz、44.1 kHz、48 kHz 的 I2S 主控(仅发射器)

支持高达 4 Mbps 的 UART

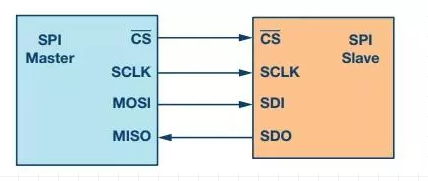

33 MHz 的 SPI 主控

UART 和 SPI 的工作电压为 1.8 至 3.3 V

I2C 工作电压为 1.2 V

4、多种时钟输入频率可供选择

19.2、26、38.4 和 52 MHz,支持 19.2 MHz 晶振输入

5、应用

FX3主要应用场景和他的内部结构有关,因为内置ARM核,应用范围十分广泛,在数字视频摄录机、数字照相机、打印机、扫描仪、视频采集卡、测试和测量设备、监控摄像机、个人导航设备、医疗成像设备、视频 IP 电话、便携式媒体播放器等多个场景都有应用。

正是因为内嵌ARM核,所以可以作为主处理器或者协处理器使用。

1、 作为协处理器-主要

这个主要是利用USB PHY的特点,通过GPIF接口向内部写入数据,通过USB接口输出。

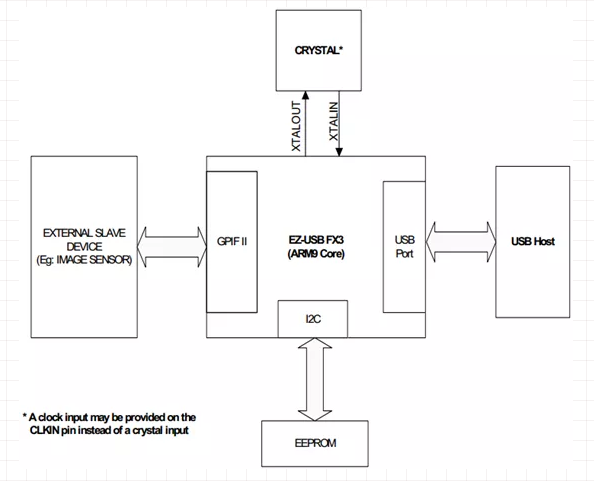

2、作为主处理器

这种就是利用ARM内核功能+USB,功能类似STM32F103,但是USB功能升级了。

硬件设计

讲硬件设计主要是为了方便FPGA工程师排故使用,下面分几个方面进行介绍,排故思路也是按照下面的顺序走。

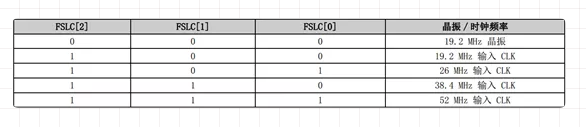

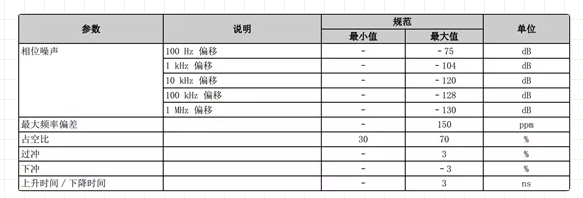

1、 时钟

我们知道FX3有19.2、26、38.4 和 52 MH,有晶体输入和有源晶振输入两种,这些组合怎么让内部PLL(锁相环)知道是那种时钟输入呢?那就是FSLC[0..2]这几个引脚进行配置,下表展示了FSLC[0..2]不同的设置代表的不同输入时钟,具体如下:

这里容易出问题的地方在于设置选项和时钟频率不匹配。

当然,FX3对于晶振/晶体是有要求的,但是比较宽松,常规的型号基本都可以满足。

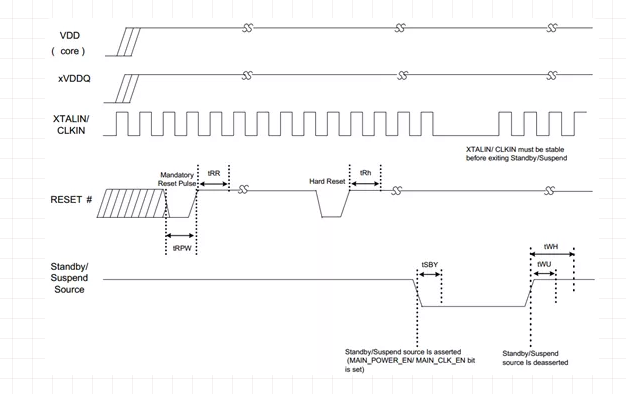

复位:

通过激活 EZ-USB FX3 上的 Reset# 引脚来初始化硬复位。复位序列和时序的具体要求详见下图。

常规的使用就是RC复位即可,想控制FX3,把Reset# 引脚拉到FPGA即可(注意电平匹配)。

时序图就是大部分芯片推荐的时序图,无非就是电源、时钟先上,然后进行复位。

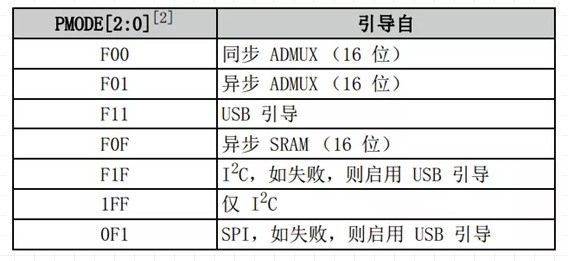

引导选向

这是最重要的一部分。

FX3 为了灵活使用,加载程序时可从多个源加载引导二进制文件(编译出来的),可通过 PMODE 引脚配置来选择。EZ-USB FX3 有下列引导选项:

- 从 USB 引导

- 从 I2C 引导

- 从 SPI (支持的 SPI 器件为 M25P16 (16 Mbit)、M25P80 (8 Mbit) 和 M25P40 (4 Mbit))或同类器件引导

- 从 GPIF II 异步 ADMUX 模式引导

- 从 GPIF II 同步 ADMUX 模式引导

- 从 GPIF II 异步 SRAM 模式引导

注2:F代表的是悬空。

这里面常用的就是F11(USB引导)用来调试和下载固件;I2C引导:用来从EEPROM启动;SPI引导,用来从SPI FLASH启动。

注意一下,对于SPI FLASH支持的型号(支持的 SPI 器件为 M25P16 (16 Mbit)、M25P80 (8 Mbit) 和 M25P40 (4 Mbit)),当然也支持同类型的器件。对于SPI FLASH很多相同的封装,引脚兼容,所以很容易造成混乱。

这里说明一下,大部分PHY芯片从外部器件引导器件时,都会首先读取外部器件的FLASH的ID,然后才启动,如果不是他数据手册里推荐的型号,很大概率是启动不了的,如果出现问题首先记得先核实以下FLASH的型号。这么做的好处当然是…貌似没什么好处。

我这里建议的是使用SPI FLASH,价格会便宜点。模式我设计的思路是使用0F1(SPI,如失败,则启用 USB 引导),然后FALSH的CS引脚加开关接地,需要烧写固件时将CS拉低,FX3启动检测不到FLASH后会自动启动USB boot,上电完毕后可以将CS放开,就可以烧写固件了。

原文:OpenFPGA

作者:碎碎思

相关文章推荐