0、官网

第一个还是官网,各种权威SPEC可以下载,当然有能力的可以参与协议制定与发布。

https://hdmiforum.org/

HDMI 论坛的成立是为了促进更广泛的行业参与下一代 HDMI 规范的开发,并支持可互操作的 HDMI 产品生态系统。HDMI 规范在单个数字接口中结合了未压缩的高清视频、多通道音频和数据,以通过单根电缆提供水晶般清晰的数字质量。该组织汇集了世界领先的消费电子产品、个人电脑、移动设备、电缆和组件制造商。作为一家非营利、互惠互利的特许公司,HDMI 论坛的使命是:

- 创建和开发新版本的 HDMI 规范和合规性测试规范,结合新的和改进的功能

- 鼓励和促进其规范在全球范围内的采用和广泛使用

- 支持完全可互操作的支持 HDMI 的产品生态系统

- 根据其规范提供开放且非歧视的许可计划

1、FPGA实现HDMI通信介绍

https://github.com/suisuisi/FPGAandImage

通过上面的介绍,可以了解到目前实现HDMI显示方案主要由 IO 模拟方式(LVDS)及外挂HDMI PHY(RGB/LCD转HDMI)两种方式,下面介绍的开源项目会在标题后重点注明哪种方式,其中第二种方式会注明芯片型号。

2、Avnet官方IP(外挂PHY,不同板子不同PHY)

Avnet 安富利集团,财富500强公司,是全球最大的电子元件、计算机产品和嵌入技术分销商之一。

https://github.com/Avnet/hdl/tree/master/IP

3、digilent官方IP(模拟,带VHDL IP)

http://www.digilent.com.cn/community/573.html

上一篇文章是介绍HDMI的实现方式,同时帖子末尾有附件下载,附件中很多IP,和本篇文章有关的是下面的两个IP。

使用方式同第一节使用一样。

PS:这种模拟的方式简单理解就是我用FPGA模拟了一个ASIC(外挂PHY)。

4、fpga4fun-->HDMI(模拟 权威 细致)

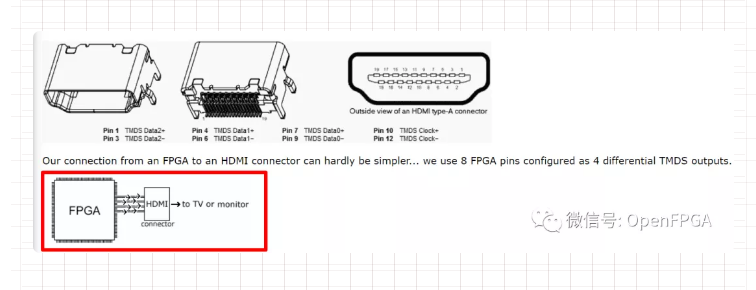

https://www.fpga4fun.com/HDMI.html

各种时序介绍的很细致,具体的实现也有源码解析,后面还有两个小实例。

介绍了上面几种基本满足80%的使用需求,下面的可以不用浪费时间看了,本着尽心的原则,还是花费点时间整理一下其他开源的项目。

5、netv_fpga_hdmi_overlay(模拟,内有IP)

https://github.com/bnewbold/netv_fpga_hdmi_overlay

http://www.kosagi.com/netv_hardware/

这个项目时从<netv_fpga>(http://www.kosagi.com/netv_ha...)中提取出来的项目,包含构建 FPGA 固件所需的所有 verilog 和脚本。

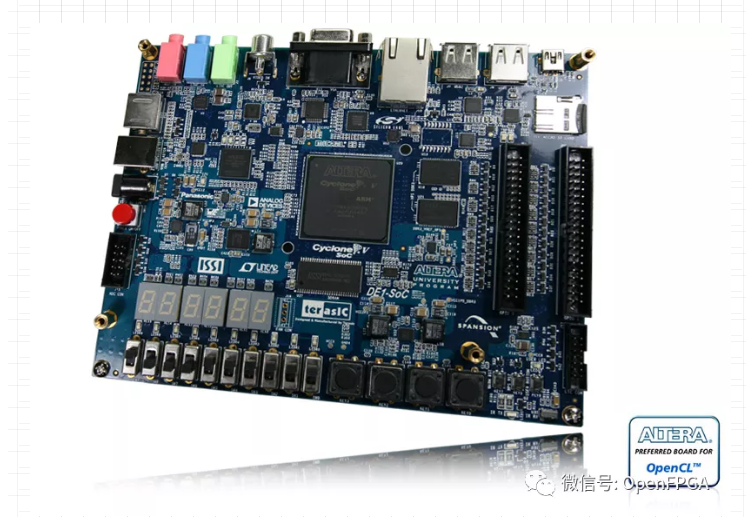

6、de10nano_vgaHdmi_chip (外挂 ADV7513)

https://github.com/nhasbun/de10nano_vgaHdmi_chip

介绍

这是对来自 Analog Devices的ADV7513芯片的测试,它从普通VGA 模块开始轻松兼容HDMI 1.4输出非常有用。

它在包含芯片的de10 nano板上进行了测试。包含Quartus Prime 17项目,轻松部署第一个工作视频信号。该项目包括:

- Verilog HDL 文件

- SDC TimeQuest 文件或时序分析

- Quartus 项目文件(完成引脚分配等)

- ./src/下包含一个文件夹,其中包含在Active HDL 9.1上完成的模拟,用于 vga 模块和同步信号的功能验证。

I2C 控制器

芯片需要在每次启动时通过 i2c 进行配置才能正常工作。该工程包含了需要配置的寄存器的值。

对于使用ADV7513不了解怎么配置寄存器的可以看下。

7、Artix-7-HDMI-processing(模拟)

https://github.com/hamsternz/Artix-7-HDMI-processing

用于接收 HDMI 输入,然后提取视频数据, 视频 Inforframe 和音频样本,然后使用它来显示音频分贝表 在屏幕的顶角。目前为简单起见,输出仅为 DVID。

特征

支持HDMI格式:-720p@50

- 720p@60,

- 1080i(有错误)

- 1080p@50

- 1080p@60 和别的....

色彩空间/格式:

- RGB 444

- YCbCr 444

- YCbCr 422

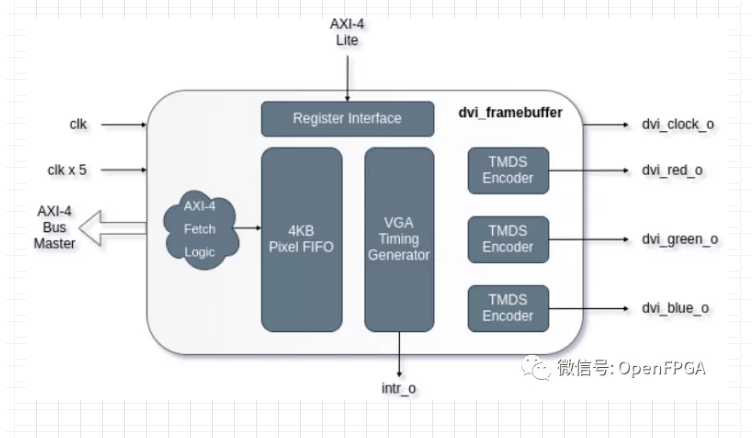

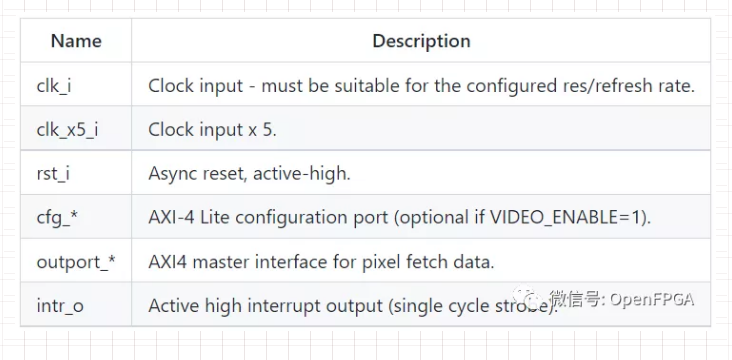

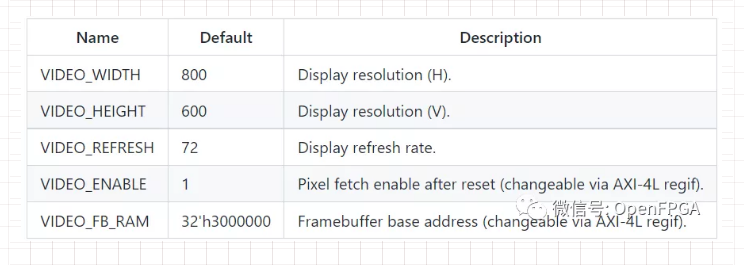

8、core_dvi_framebuffer(模拟)

https://github.com/ultraembedded/core_dvi_framebuffer

这个项目对于使用FPGA SOC的板卡还是很用帮助的,使用了AXI-4总线封装了整个IP。

该项目基于上一项目进行封装。

特征:

- HDMI / DVI TMDS 输出。

- RGB565 输入格式。

- 支持突发的 AXI-4 总线主控。

- 4KB 像素数据预取 FIFO(映射到 Xilinx FPGA 中的 BlockRAM)。

- AXI-4 Lite 寄存器接口,具有可编程帧缓冲区获取地址、启用、中断控制。

- 帧中断输出开始。

- 可配置的显示分辨率(640x480、800x600、1280x720、1920x1080)。

- 与 Linux 'simple-framebuffer' 驱动程序一起使用。

接口:

参数:

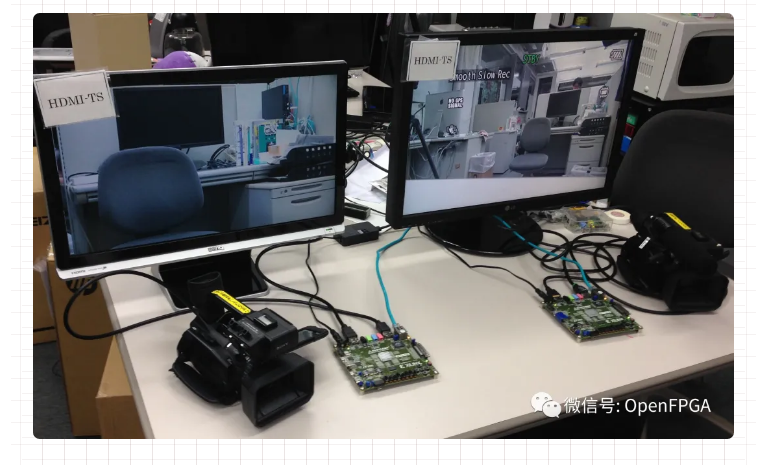

9、hdmi-ts(模拟)

https://github.com/aomtoku/hdmi-ts

介绍

HDMI-TS(HDMI 传输系统)是基于 IP(互联网协议)的低延迟 HDMI 视频通信系统。远程位置之间的复杂交互需要低延迟,例如协同工作、远程控制等。为此,开发了硬件同步视频处理方法,RV-SYNC(远程虚拟同步)。远程主机的延迟相当于没有。

目录结构

- /cores/ 核心库,包含 Verilog 源代码、测试平台和文档。

- /boards/ 支持的 FPGA 板的顶级设计文件、约束文件和 Makefile。

- /software件/软件。

10、HDMI-data-streams-Spartan-6(模拟+Driver)

https://github.com/Nancy-Chauhan/HDMI-data-streams-Spartan-6

通过 Spartan 6 FPGA 将高清多媒体接口 (HDMI) 数据流传输到 HDMI/DVI 显示器

板子的介绍:

http://www.digilent.com.cn/products/product-atlys-spartan-6-fpga-trainer-board.html

项目的详细介绍:

https://nancy-chauhan.medium.com/transmission-of-hdmi-data-streams-to-hdmi-dvi-monitors-via-spartan-6-fpga-295ea28587

11、Analog-To-Digital (外挂 ADV 7180)

https://github.com/mattsybeldon/Analog-To-Digital

介绍

板子使用平台:

这是一个个人 FPGA 项目,使用 ADC 来获取模拟视频并输出为数字。这样做的主要好处是可以绕过电视中的去隔行器,这可能是运行旧模拟设备(游戏机)时输入延迟的最大来源。

(曾经)为 Nintendo Gamecube 玩 Super Smash Bros. Melee 。该游戏于 2001 年发布,Gamecube 只有模拟输出。大多数 Gamecubes 仅输出 480i(除非您想在分量电缆上花费 100+)。最终发生的情况是,信号在任何现代显示器上都被去隔行。根据 Smashboards 的说法,这通常是输入延迟方面的瓶颈。例如,如果你有一个 Wii 和运行组件到同一个显示器 (480p),输入延迟情况会显着改善。由于所有这一切,Smashers 以囤积 CRT 电视以最小化输入延迟而臭名昭著。

该项目处理硬件上的去隔行。信号可以使用 VGA 或 HDMI 输出,这两种方式都可以在现代电视上找到。该项目使用 VGA,因为那是 DE-1 上有VGA。

12、nexys3_hdmi(外挂 未知)

https://github.com/G33KatWork/nexys3_hdmi

这个没什么介绍的,项目介绍很少,没什么参考价值。

13、FPGA-HDMI (模拟)

https://github.com/bonjourdrs/FPGA-HDMI

该项目也是digilent官方办卡(基于K7)自带的项目,无需过多介绍,下面的网址是官方的介绍,硬件也是可以参考的。

http://www.digilent.com.cn/products/product-genesys-2-kintex-7-fpga-development-board.html

同理基于这个板卡的示例如下(自带代码):

http://www.digilent.com.cn/project/details/92.html

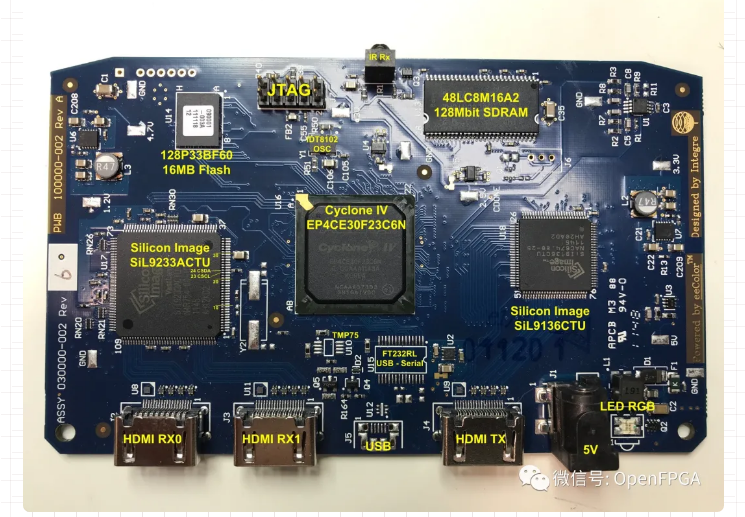

14、color3(外挂 SiI9136 HDMI TX和SiI9233 RX)

https://github.com/tomverbeure/color3

简介

该项目配置了SiI9136 HDMI TX和SiI9233 RX芯片,并成功地将视频从RX转发到TX端口,同时对其进行了一些图像处理。

该板上的芯片几乎可以将任何已知的 HDMI 格式进行并行和反向。8bit、10bit、12bit彩色、YUV等

除此之外,这些芯片还可以在 HDMI 音频和 I2S 之间进行转换。然而,HDMI 接收器的 I2S 输出直接连接到 HDMI 发送器的 I2S 输入,因此 FPGA 不能处理音频。

该项目的最新进展:

https://hackaday.com/2013/05/08/hdmi-color-processing-board-used-as-an-fpga-dev-board-to-mine-bitcoins/

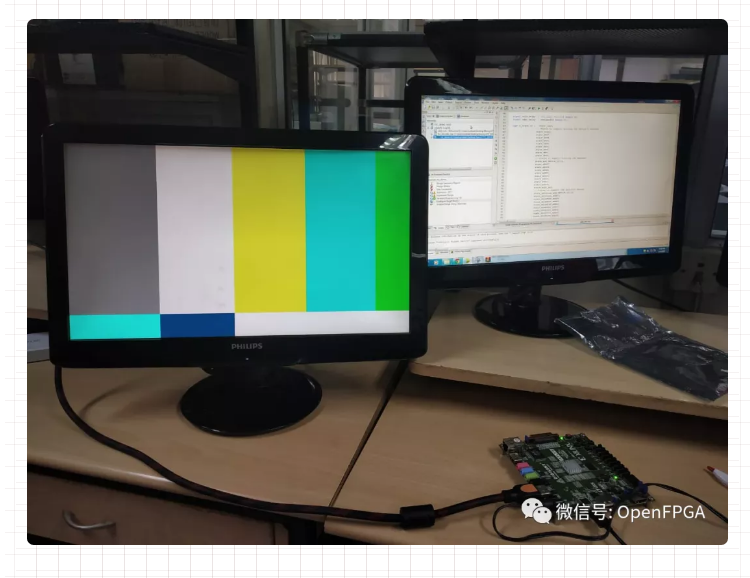

15、SimpleVOut(模拟)

https://github.com/cliffordwolf/SimpleVOut

类似:core_dvi_framebuffer(模拟)

SimpleVOut——用于创建 VGA/DVI/HDMI/OpenLDI 信号的简单 FPGA 内核。

SimpleVOut (SVO) 是一组简单的 FPGA 内核,用于创建各种格式视频信号。内核使用 AXI 流进行连接。大多数配置(分辨率、帧率、颜色深度等)都可以进行配置。有关这些参数的详细信息,请参阅 svo_defines.vh。

该目录包含:

svosrc

这是实际的 SVO 源代码。如果你使用 SVO 只需复制这个目录到你的项目中。

vivado_ip

SVO 的示例 Vivado IP 封装器 (simplehdmi)。该 IP 提供了一个视频 DMA 和一个简单的终端覆盖并创建 DVI/HDMI 信号。

zybo_vl

将 SVO 用于 Zybo 板 (Xilinx Vivado) 的示例设计。这个示例是用 Verilog HDL 编写的。

zybo_bd

使用来自 vivado_ip的 IP 的 Vivado 模块设计示例。

svosrc目录包含以下用于输出视频的核心

不同格式的流(有关用法示例,请参见 zybo_vl/system.v):

- svo_enc.v 视频“编码器”。其他框架将此组件称为视频 计时发生器。这个核心的输出可以直接馈入 到 DAC 以创建 VGA 信号。

- svo_openldi.v 这需要 svo_enc-output 并创建一个 OpenLDI(又名 LVDS) 视频信号。

- svo_tmds.v 这需要 svo_enc-output 并创建一个 DVI/HDMI 视频信号。

以下内核可用于创建视频流:

svo_tcard.v

该内核生成静态测试卡。

svo_pong.v

一个小乒乓球游戏。

svo_term.v

一个文本终端。仅存储最后 N 个(默认值 = 2048)个字符并在字符内存不足时滚动。适合显示调试信息(例如早期启动消息)。

svo_vdma.v

视频 DMA 控制器。有一个只读的 AXI4 主接口访问视频内存。

如果你的HDMI接口不知道干什么,可以试一试这个项目,被作者玩出了花。

总结

以上就是今天推荐的项目,这里建议前几个项目和后面几个项目可以入坑,其他看自己需求。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐