日前,国家发改委等四部门联合发布《全国一体化大数据中心协同创新体系算力枢纽实施方案》,提出在京津冀、长三角、粤港澳大湾区、成渝以及贵州、内蒙古、甘肃、宁夏建设全国算力网络国家枢纽节点,启动实施“东数西算”工程,构建国家算力网络体系。

算力,成为整个数字信息社会发展的关键。通过“东数西算”能缓解一些问题,但没有根本解决问题:当前要想提升算力,更多的是靠“摊大饼”的方式构建更加规模庞大并且低能耗的现代化数据中心。

这是算力提升的Scale out(增大规模),那么,我们如何能够做到算力的Scale up(提升单个计算节点的性能)?或者说,我们如何显著(数量级)的提高单个处理器的性能?

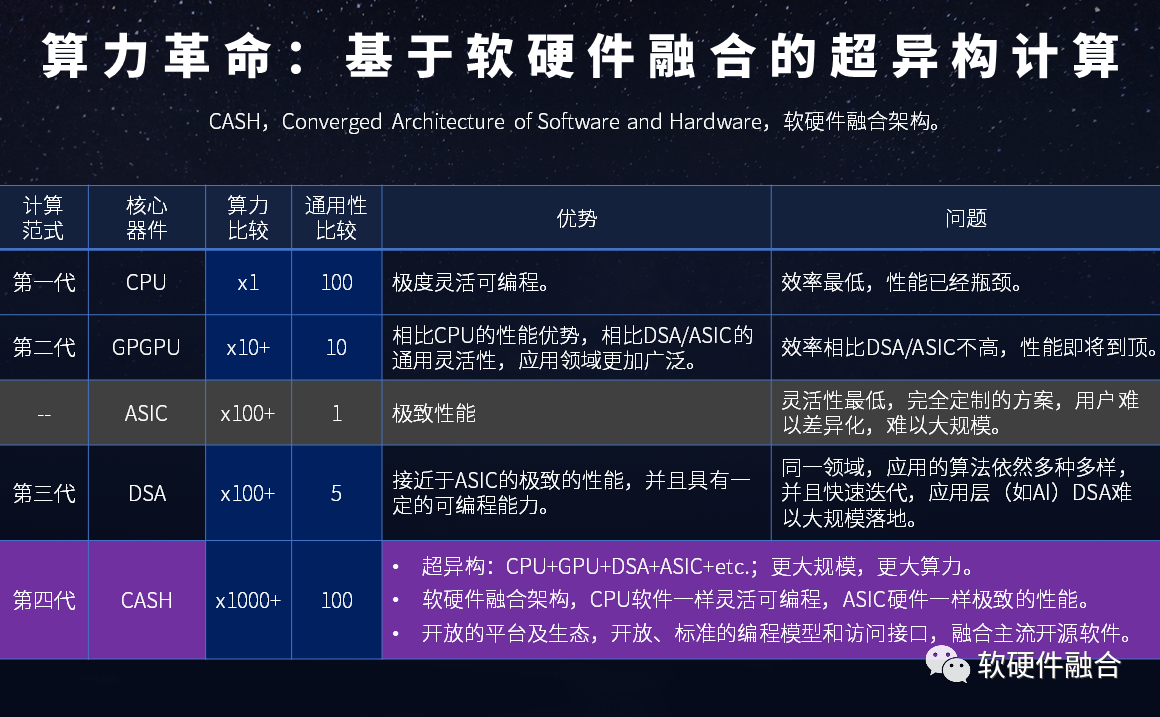

当前,算力成为制约信息技术更加蓬勃发展的最核心问题:

- CPU灵活性好,但效率最低,并且已经性能瓶颈;

- GPU具有一定的灵活性,但效率相比DSA仍有差距,并且在可见的未来很快会面临和CPU一样的性能瓶颈问题。

- DSA在极致性能的情况下,提供了一些灵活性。但面对的领域(Domain)应用多种多样并且快速变化,一直没能实现DSA芯片的大规模落地。

我们需要构建新一代的创新计算范式,相比当前,要把算力至少再提升1-2个数量级,并且能够提供非常好的易用编程能力,来持续应对未来10年的更加复杂系统的算力需求爆炸的挑战。

注:本文想法还比较粗糙,抛砖引玉,期待更多的讨论,未来会优化更新。

1 第一代:CPU

1.1 指令集软硬件解耦,CPU性能狂飙,软件蓬勃发展

指令集,是软硬件的媒介。CPU是最灵活的,原因在于运行于CPU指令都是最基本的加减乘除外加一些访存及控制类指令,就像积木块一样,我们可以随意组合出我们想要的各种形态的功能,形成非常复杂并且功能强大的程序,或者称为软件。

CPU最大的价值在于提供并规范了标准化的指令集,使得软件和硬件从此解耦:

- 硬件工程师不需要关心场景,只关注于通过各种“无所不用其极”的方式,快速的提升CPU的性能。

- 而软件工程师,则完全不用考虑硬件的细节,只关注于程序本身。然后有了高级编程语言/编译器、操作系统以及各种系统框架/库的支持,构建起一个庞大的软件生态超级帝国。

通过标准化指令集,达到软硬件解耦,并且互相向前兼容(软件向前兼容之前的硬件,硬件向前兼容之前的软件)。这样,CPU的硬件设计者,可以不用考虑上层的业务到底是什么,也即不关心通过指令组合出的程序到底是干什么用的。只需要关心,我设计的CPU性能如何的好,可以实现更高的IPC(Instructions per Cycle)和更高的频率。

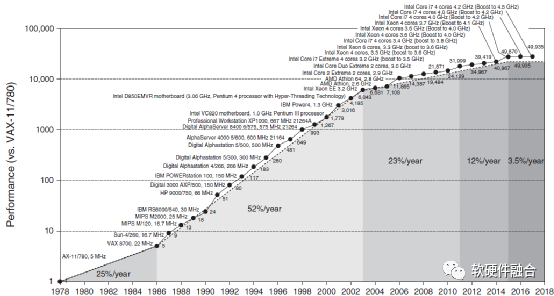

图1 历年CPU性能提升对比

从图1中,可以看到,在差不多40年的时间里,CPU的整体性能提升接近50000倍。一方面,这有赖于处理器架构的翻天覆地变化,也有赖于半导体工艺的进步。另一方面,更有赖于通过标准化的指令集,使得CPU平台的硬件实现和软件编程完全解耦,没有了对方的掣肘,软件和硬件均可以完全的放飞自我。

一方面是CPU性能狂飙,另一方面,则是软件逐渐发展成了一个超级的生态帝国。从各种数以百万级使用者的高级编程语言,到广泛使用在云计算数据中心、PC机、手机等终端的智能操作系统,再到各种专业的数据库、中间件,以及云计算基础的虚拟化、容器等。上述这些软件都是基础的支撑软件,是软件的“冰山一角”,而更多的则是各种用户级的应用软件,系统级和应用的软件,共同组成了基于CPU的软件超级生态。

1.2 摩尔定律失效,CPU性能瓶颈,制约软件的发展

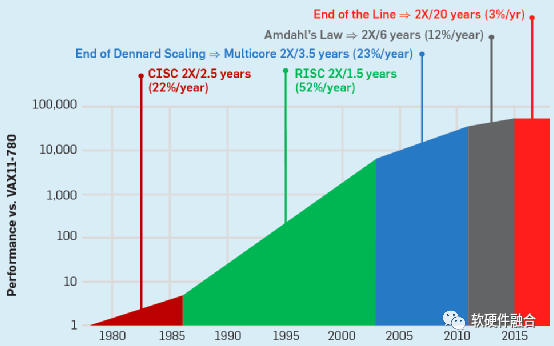

图2 CPU性能提升的五个阶段

图2和上一节的图1是一致的,图2主要是明确展示了五个发展阶段:

- CISC阶段。在上世纪80年代,以Intel和AMD的x86架构为典型代表的CISC架构CPU开启了CPU性能快速提升的时代,CPU性能每年提升约25%(图中22%数据有误),大约3年性能可以翻倍。

- RISC阶段。随后,CISC系统越来越复杂,有很多设计资源花在了不经常使用的指令实现上。随后,RISC证明了“越精简,越高效”。随着RISC架构的CPU开始流行,性能提升进一步加快,每年可以达到52%,性能翻倍只需要18个月。

- 多核阶段。单核CPU的性能提升越来越困难,开始通过集成更多CPU核并行的方式来进一步提升性能。这一时期,每年性能提升可以到23%,性能翻倍需要3.5年。

- 多核整体性能递减阶段。随着CPU核集成的数量越来越多,阿姆达尔定律证明了处理器数量的增加带来的收益会逐渐递减。这一时期,CPU性能提升每年只有12%,性能翻倍需要6年。

- 性能提升瓶颈阶段。不管是从架构/微架构设计、工艺、多核并行等各种手段都用尽的时候,CPU整体的性能提升达到了一个瓶颈。如图,从2015年之后,CPU性能每年提升只有3%,要想性能翻倍,需要20年。

2 第二代:GPU

2.1 GPGPU,通用的并行计算平台

GPU,Graphics Processing Units,图形处理单元。顾名思义,GPU是主要用于做图形图形处理的专用加速器。GPU内部处理是由很多并行的计算单元支持,如果只是用来做图形图像处理,有点“暴殄天物”,其应用范围太过狭窄。

因此把GPU内部的计算单元进行通用化重新设计,GPU变成了GPGPU。到2012年,GPU已经发展成为高度并行的众核系统,GPGPU有强大的并行处理能力和可编程流水线,既可以处理图形数据,也可以处理非图形数据。特别是在面对SIMD类指令,数据处理的运算量远大于数据调度和传输的运算量时,GPGPU在性能上大大超越了传统的CPU应用程序。现在大家所称呼的GPU通常都指的是GPGPU。

图3 NVIDIA图灵GPU架构

2018年,NVIDIA发布了最新一代的GPU架构——图灵架构。基于图灵架构的GPU提供PCIe 3.0来连接CPU主机接口,提供千兆的线程引擎来管理所有的工作。另外,图灵架构支持通过两路x8的NVLink接口实现多GPU之间的数据一致性访问。

如图3,图灵架构GPU的核心处理引擎由如下部分组成:6个图形处理簇(GPC);每个GPC有6个纹理处理簇(TPC),共计36个TPC;每个TPC有2个流式多核处理器(SM),总共72个SM。每个SM由64个CUDA核、8个Tensor核、1个RT核、4个纹理单元,总计有4608个CUDA核、576个Tensor核、72个RT核、288个纹理单元。

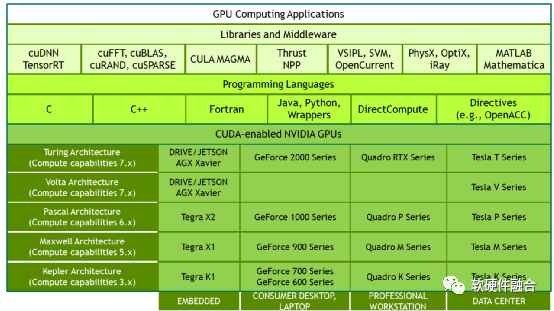

2.2 CUDA,NVIDIA GPU成功的关键

图4 CUDA框架

2006年NVIDIA推出了CUDA,这是一个通用的并行计算平台和编程模型,利用NVIDIA GPU中的并行计算引擎,以一种比CPU更高效的方式解决许多复杂的计算问题。CUDA提供了开发者使用C++作为高级编程语言的软件环境。也支持其他语言、应用程序编程接口或基于指令的方法,如FORTRAN、DirectCompute、OpenACC。

CUDA是NVIDIA成功的关键,它极大的降低了用户基于GPU并行编程的门槛,在此基础上,还针对不同场景构建了功能强大的开发库和中间件,逐步建立了GPU+CUDA的强大生态。

3 第三代:DSA

3.1 DSA兴起

2017年三月,图灵奖获得者David Patterson和John Hennessy在其“体系结构的黄金年代”主题演讲中,提出了DSA架构。CPU的性能提升走向终结,需要针对特定场景有针对性的定制加速,而DSA则是切实可行的解决方案。DSA是在定制ASIC的基础上回调,使其具有一定的软件可编程灵活性。

按照指令的“复杂度”,DSA可以归属到ASIC一类。跟CPU、GPU、FPGA以及传统ASIC相比,DSA具有如下一些特点:

- 跟GPU、FPGA类似,通常的DSA不是图灵完备的。是面向系统中的计算密集型任务的计算加速,而不是运行整个系统。因此DSA平台的架构是“CPU+DSA”。

- DSA有简单的指令集,可以编程,因此是处理器;DSA是针对特定领域定制设计,因此是特殊的一种ASIC。DSA可以看做是通常意义上的ASIC向通用处理的一种回调,增加了ASIC的灵活性。

- DSA应用领域的规模足够大的话,可以去定制IC芯片,这样可以覆盖IC芯片高昂的前期成本;如果规模较小,选择FPGA实现DSA设计则是一个更好的选择。

- 架构和逻辑设计需要了解具体的领域和相关算法,而不是仅仅关注架构和设计本身。

- 基于CPU+DSA的异构编程是个非常大的挑战。

3.2 AI领域DSA案例:谷歌TPU

DSA架构的第一个经典案例是谷歌的TPU。TPU(Tensor Processing Unit,张量处理单元)是Google定制开发的ASIC芯片,用于加速机器学习工作负载。谷歌在2013年进行的一项预测分析显示,人们每天使用语音识别DNN进行语音搜索三分钟,这将使数据中心的计算需求增加一倍,而使用传统的CPU成本非常昂贵。因此,谷歌启动了一个高优先级项目,即TPU项目,以快速生成用于推理的自研ASIC。目标是将GPU的性价比提高10倍。

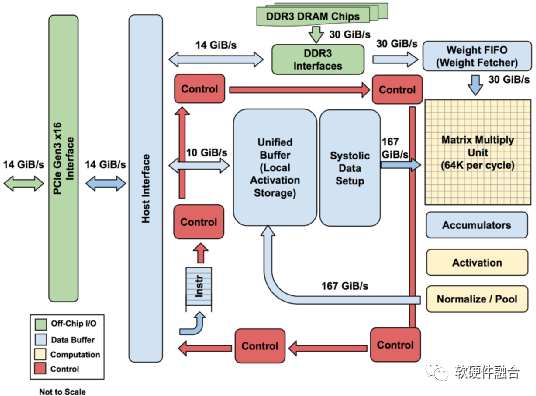

图5 谷歌TPU 1.0结构框图

如图5,显示了TPU的结构框图。TPU指令通过PCIe Gen3 x16总线从Host发送到TPU的指令缓冲区。内部模块通过256字节宽的总线连接在一起。开始在右上角,矩阵乘法单元是TPU的核心,它包含256x256 MAC,可以对有符号或无符号整数执行8位乘加,16位乘积收集在矩阵单元下方的4 MB 32位累加器中。4 MB可容纳4096个256元素的32位累加器。矩阵单元每个时钟周期产生一个256个元素的部分和。

TPU指令设计为CISC(复杂指令集计算机)类型,包括一个重复域。这些CISC类型指令的CPI(Cycles per Instruction,每条指令的平均时钟周期)通常为10到20。总共大约有十二条指令,主要的五个指令是:

- Read_Host_Memory。将数据从CPU内存读取到统一缓冲区(UB)中。

- Read_Weights。将权重从权重存储器读取到权重FIFO中,作为矩阵单元的输入。

- MatrixMultiply / Convolve。让矩阵单元执行矩阵乘法或执行从统一缓存区到累加器的卷积。矩阵运算采用大小可变的B256输入,然后将其乘以256x256恒定的权重输入,然后生成B256输出,需要B个流水线周期才能完成。

- Activate。根据ReLU,Sigmoid等选项,执行人工神经元的非线性功能。它的输入是累加器,其输出是统一缓冲区。当连接到非线性函数逻辑时,还可以使用芯片上的专用硬件执行卷积所需的池化操作。

- Write_Host_Memory 将数据从统一缓冲区写入CPU内存。

其他指令包括备用Host内存读写、组配置、两个版本的同步、中断主机、调试标签、空指令NOP和停顿Halt。

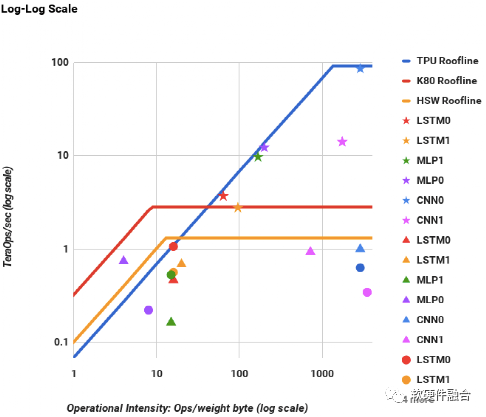

(★代表TPU,▲代表K80 GPU,●代表Haswell CPU)

图6 CPU、GPU和TPU的Roofline组合图

如图6,对于HPC来说,Y轴是每秒浮点运算的性能,X轴是操作强度,用访问的每个DRAM字节的浮点操作来衡量。峰值计算速率就是Roofline的“平坦”部分,内存带宽是每秒字节数,因此变成了Roofline的“倾斜”部分。从图6中,我们可以看到,所有TPU星星均位于CPU和GPU的Roofline之上。从Roofline的平坦部分可以看出,TPU的处理速度比GPU和CPU要快15-30倍。

图7 CPU、GPU和TPU的性能功耗比

如图7,其中的TPU’是使用了GDDR5存储的改进型。可以看到,相比CPU性能提升196倍,相比GPU性能提升68倍。谷歌随后又开发了TPU 2.0、3.0版本。TPU 1.0的性能峰值达到了92Tops,而TPU2.0性能峰值达到180Tflops,TPU3.0更是达到了420Tflops。并且,从TPU 2.0开始,TPU不再是作为一个加速卡应用于通用服务器,而是定制的TPU集群,这样会更大限度的发挥TPU的加速价值。

3.3 网络领域DSA案例:Intel Tofino

SDN蓬勃发展,从控制面可编程的Openflow到数据面可编程的P4语言,以及出现了Intel PISA架构的Tofino芯片。站在体系结构的视角,Tofino是网络领域最典型的DSA,其实现的可编程流水线既能够达到ASIC级别的性能,又能够通过P4对整个包处理数据面进行编程。

Intel基于PISA架构,设计了面向数据中心的、支持P4数据面编程的ASIC交换芯片。其目标是使对网络的编程与和CPU编程一样简单。当网络是完全可编程的(即控制平面和数据平面都在最终用户的控制之下)时,网络行业将享有与软件一样飞速的发展。

在Intel看来,虽然已经存在NPU和FPGA,可以修改网络协议和编辑数据包,并为那些知道如何编写微代码或RTL的人员提供适度的可编程性,但是它们跟ASIC的性能不在一个数量级。因此,NPU和FPGA只能在性能不敏感的地方找到用武之地。Intel为网络行业提供两全其美的解决方案:可编程性数据平面协议,并且达到行业最高速度。Intel不仅开发了全球第一个比传统ASIC还要更快的可编程交换机芯片,而且还使得网络编程变得容易并且通用。

Intel与Google、Microsoft、Princeton及Stanford合作,开发了用于编程网络的开源网络编程语言P4。程序员可以基于P4编程一次来描述网络行为,然后编译程序以在各种不同的平台上运行。P4为网络设备制造商和网络所有者提供了差异化的手段,可以使产品或整个网络比竞争对手更好。

这与当前的情况形成了鲜明对比,如果用户想向网络添加新功能,则必须与芯片供应商共享该功能,并看到它也出现在竞争对手的网络中,从而打败了差异化的目的。设备制造商也不愿意添加新功能。添加新功能需要花费几年的时间,然后竞争优势却很短暂。这导致一些公司倾向于开发特有的固定功能ASIC,以保持领先地位。

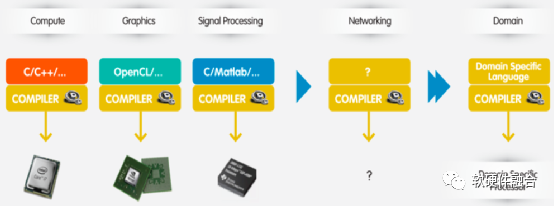

图8 像CPU编译器一样的网络编译器

如图8所示,可编程性长期存在于计算、图形、数字信号处理以及特定领域处理器中,从而使蓬勃发展的开发人员社区能够快速创新并编写以最终用户为中心的解决方案。Intel的PISA架构可以像DSP、GPU以及TPU那样,它将完全控制权交给网络所有者。

为此,Intel首先确定了一个小规模的原语指令集来处理数据包,总共约11条指令。以及非常统一的可编程流水线(PISA架构),来快速连续地处理数据包头。程序使用领域特定语言P4编写,然后由Intel Capilano编译器进行编译,并经过优化以在PISA架构的设备上全线速运行。Intel的目标是使网络更加敏捷、灵活、模块化且成本更低。

Intel认为,网络系统正朝着由三层构成的方向发展:在底部是一个P4可编程的Tofino交换机,在上面是一个基于Linux的操作系统,运行专有的控制平面应用程序。Intel为整个行业提供最快的、最高可编程性、经过P4优化的交换机硬件。

4 第四代:CASH超异构

4.1 芯片从2D到3D到4D,单个芯片所能容纳的晶体管数量越来越多

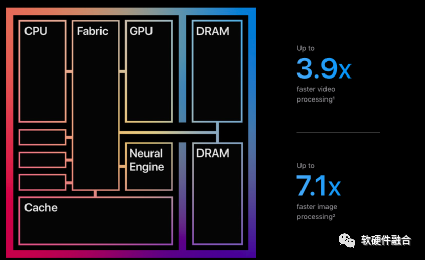

图9 苹果公司M1芯片说明

如图9所示,苹果公司自研的ARM CPU M1基于TSMC 5nm工艺,具有160亿个晶体管,如此巨大规模的设计,使得M1集成了8核CPU和8核GPU,并且每个处理器都可以非常奢侈的使用内部Register、Buffer或Cache资源(这些是晶体管消耗大户)。

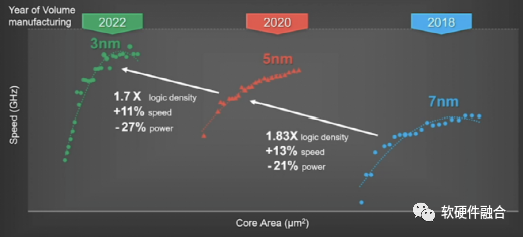

图10 TSMC 新工艺Roadmap

如图10所示,TSMC 5nm刚刚量产,其3nm工艺已经在路上,2nm、1nm也都在未来几年的路线图中。并且,TSMC已经开始在攻关0.1nm工艺,半导体工艺即将进入亚纳米(埃米)时代。

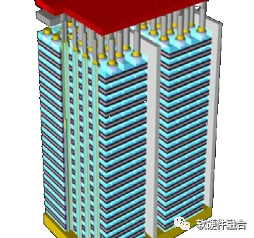

图11 3D存储封装

如图11,在存储领域,近些年来还兴起了3D封装技术,使得集成电路从二维进入三维。

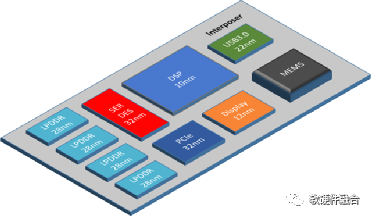

图12 Chiplet示意图

如图12,芯粒(chiplet)机制,把多个芯片裸DIE集成到一起,从3D到4D,都进一步增强了单位面积的晶体管集成度。

工艺持续进步、3D堆叠以及Chiplet多Die互联,使得芯片从2D->3D->4D。这些技术的进步,意味着在芯片这个尺度,可以容纳更多的晶体管,也意味着芯片的规模越来越大。

4.2 从异构到超异构,从SOC到Multi-SOC,设计规模越来越庞大

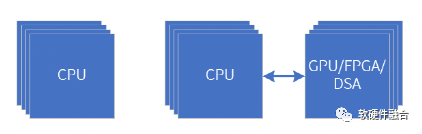

(a) CPU同构并行 (b) CPU + xPU异构并行

图13 同构并行和异构并行计算架构

当前,并行计算的主流架构如图13所示:

- 图13(a)为CPU同构并行。常见的多核CPU和多CPU socket互联即是同构并行计算。CPU由于其灵活通用性好,是最常见的并行计算架构。但由于单个CPU核的性能已经到达瓶颈,并且单颗芯片所能容纳的CPU核数也逐渐到头。CPU同构并行已经没有多少性能挖潜的空间。

- 图13(b)为CPU+xPU的异构加速并行架构。一般情况下,GPU、FPGA及DSA加速器都是作为CPU的协处理加速器的形态存在,不是图灵完备的。因此,这些加速器都需要CPU的控制,CPU+xPU成为了典型架构。

异构并行计算架构的情况说明:

- 如果CPU不参与计算,这时负责GPU等加速器的控制和任务和数据协同,则不需要性能特别强大的CPU。整个异构计算的计算性能基本由加速器决定。

- GPU作为加速器。GPU具有一定的灵活性,但效率相比DSA仍有差距,并且在可见的未来也会很快面临和CPU一样的性能瓶颈问题。

- FPGA作为加速器,受限于其编程难度和设计规模约束,通常作为FaaS平台,充分利用FPGA硬件可编程的弹性。

- DSA作为加速器。DSA在极致性能的情况下,提供了一些灵活性。但面对的领域(Domain)应用多种多样并且快速变化,一直没能实现DSA芯片的大规模落地。

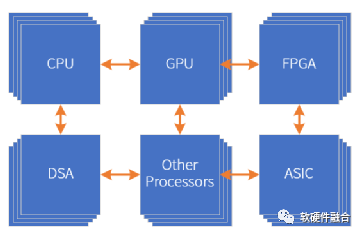

图14 多种处理引擎共存的超异构并行计算

随着芯片工艺所能支撑的设计规模越来越大,并且,CPU、GPU、FPGA、一些特定的算法引擎,都可以作为IP,被集成到更大的系统中。这样,构建一个更大规模的芯片设计成为了可能。在这里,我们提出“超异构”并行计算的概念,如图14,超异构指的是由CPU、GPU、FPGA、DSA、ASIC以及其他各种形态的处理器引擎共同组成的复杂芯片系统。

站在系统的角度,传统的SOC是单系统,而超异构系统则是多个系统整合到一个更加庞大的宏系统。传统SOC和超异构SOC的区别和联系:

- 设计规模的不同。MCU芯片是SOC,手机芯片是SOC,超异构架构芯片也是SOC。那么区别在哪里呢?但MCU级别SOC通常不跑操作系统或者跑RTOS级别的操作系统,进行一些简单的控制和处理。而手机SOC则需要运行大型操作系统,如安卓、IOS等,使得我们的手机越来越接近于一台电脑。而超异构架构,则不简单是运行操作系统和各种软件,而是聚焦提供既性能强劲并且软件能够灵活充分使用的庞大资源池;在底层软件的协助下,把硬件变成一个无差别的计算平台资源池,供软件随意的切分组合,把算力更灵活的提供给用户。

- 单系统和多系统。传统的SOC,更多的是有一个基于CPU的核心控制程序,来驱动CPU、GPU、外围其他模块以及接口数据IO等的工作。可以说,整个系统的运行是集中式管理和控制的。而超异构由于其规模和复杂度,则很难做到这一点,每个子系统其实就是一个传统SOC级别的系统,然后这些系统需要根据一些特定的协议进行交互。整个超异构的系统呈现出分布式系统的特点。

- 数据流驱动还是指令流驱动。传统SOC中,CPU是由指令流(程序)来驱动运行的,然后CPU作为一切的“主管”再驱动外围的GPU、其他加速模块、IO模块运行。而在超异构的多SOC系统中,由于系统复杂度的影响,指令流的设计模式很难“同步”不同系统间的控制交互。整个交互实际上是由数据交互产生的。并且,由于要处理的数据带宽的急剧增大,很多处理引擎都是数据流驱动的模式,而不是指令流驱动。表现在整个宏系统上,都可以理解为数据流在驱动整个系统运转。

超异构需要实现相比传统基于GPU或DSA的异构计算10倍甚至100倍以上的性能提升,并且需要实现整体接近于ASIC的极致的性能,还要确保整个系统的接近于CPU软件的通用可编程能力。

4.3 软硬件融合,超异构计算的必由之路

由于云计算的发展,数据中心已经发展到超大规模,每个超大规模数据中心拥有数以万计甚至十万计的服务器规模。超大规模数据中心的发展,是云计算逐渐走向软硬件融合的根本性驱动力量。

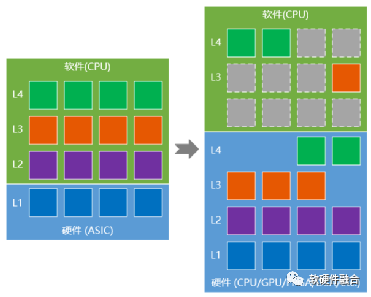

图15 软硬件融合和CPU系统不断卸载

云服务器上运行的各类软件可以看做是一个非常复杂的并且分层的系统, 由于CPU已经性能瓶颈,在宏观的数据中心规模的加持下, 以及IaaS层针对特定场景优化的一些服务,如图15所示,我们可以认为:软硬件融合的过程其实就是系统不断卸载的过程。

软硬件融合:

- 不改变系统层次结构和组件交互关系,但打破软硬件的界限,通过系统级的协同设计,达成整体最优。

- 传统分层很清晰,下层硬件上层软件;软硬件融合的分层分块,每个任务模块是软件还是硬件,或软硬件协同,都有可能。软件中有硬件,硬件中有软件,软硬件融合成一体。

- 宏观的看,越上层越灵活软件成分越多,越下层越固定硬件成分越多。庞大的规模以及特定场景服务,使得云计算底层Workload逐渐稳定并且逐步Offload到硬件(被动趋势)。

- 软硬件融合架构,使得“硬件”更加灵活,功能也更加强大,这样使得更多的层次功能向“硬件”加速转移(主动抢占)。

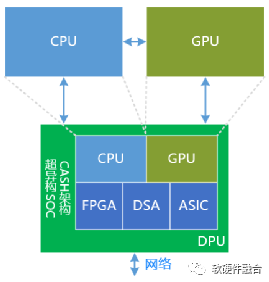

图16 基于CASH架构超异构实现的DPU

通常,我们把DPU当做是CPU的任务卸载加速,这个想法依然没有摆脱以CPU为中心架构设计的“桎梏”。

更本质的,如图16所示,基于CASH架构(CASH,Converged Architecture of Software and Hardware,软硬件融合架构)的DPU,是一个性能强劲的、功能完整的、超异构计算的算力平台。在这个平台里,包含了硬件加速部分去完成底层基础设施层的加速处理;也包含了,用于应用层处理的CPU和GPU,来完成应用层的处理。

独立的CPU和GPU可以看做是DPU的扩展,只有当集成的CPU/GPU不满足处理要求时,作为独立的计算平台,来增强整个系统的功能。

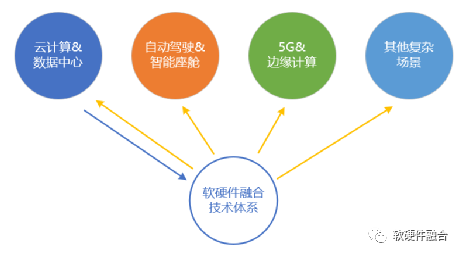

图17 软硬件融合技术是各种复杂计算场景的基础支撑

软硬件融合技术,是为了应对算力需求最高、系统规模最大、成本最敏感、灵活性要求最高的云计算数据中心场景的各种复杂挑战,而逐渐形成的技术理念和一整套技术体系。

基于软硬件融合的超异构混合计算,聚焦算力需求再上1-2个数量级的复杂场景。面向未来,自动驾驶、5G/6G核心网、边缘计算等场景,对算力的需求都会更加强劲,面对如此多的复杂系统场景,软硬件融合也有了更多的用武之地。

如图17,软硬件融合从云计算抽象出来,反过来指引包括云计算、自动驾驶等复杂系统场景的芯片及系统设计。

5 总结

软硬件融合的超异构计算需要达到如下一些标准:

- 性能。单位晶体管资源的性能水平接近于ASIC,整体性能需要达到GPGPU、DSA的10-100倍甚至以上。

- 通用灵活性。在保证性能极致的基础上,要确保其可编程能力达到接近于CPU软件的水平。并且给开发者提供友好的编程平台。

- 开放、开源。CPU有x86、ARM和RISC-v三大主流的架构平台,而DSA方面,完全是各家自己定义的各种互不兼容的架构。到了超异构时代,在软件定义的加持下,一定需要开放的标准化的架构定义,才能真正实现不同架构不同软件生态之间的“互联互通”。

各个平台的算力和通用性总结如下图18所示。

图18 CPU、GPU、DSA、CASH算力平台比较

(正文完)

作者:Chaobowx

来源:https://mp.weixin.qq.com/s/ynec17iGCLh1t_ZrZK9UwA

微信公众号:

相关文章推荐

更多软硬件技术干货请关注软硬件融合专栏。