通过前段时间的面试,我发现很多入门或者工作1~2年的人,对于module的理解还停留在一种语法的关键字,类似c中的main,我相信应该还有很多人的想法都是这样。经过这几天的思考,我发现造成目前这种情况并不是个人能力导致的,而是国内的环境导致的。

- 1、学习Verilog先学习一下C;

- 2、Verilog和C语法规则类似,之前学了C再学习Verilog很快;

- ......

上面的论调在论坛和各种XX群里是很常见的,同时国内早期的人们图书多半是从IEEE文档里把语法部分摘抄过来的,这就导致了很多人对Verilog这一硬件描述语言理解不深,今天我们就拿最最常见的module为例再深入讨论一下。

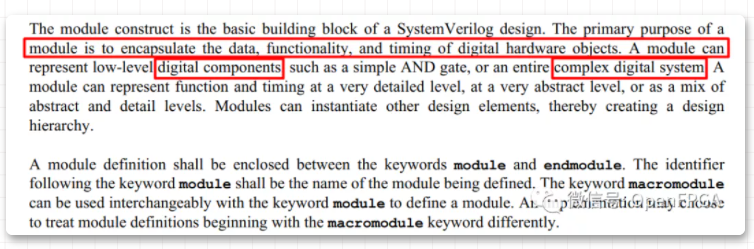

IEEE中对于module的描述

IEEE Standard 1800-2017 中对modules的定义

我们从中很清楚的知道module是对数字电路的数据、功能和时序的封装,说白了模块的实际意义是代表硬件电路上的逻辑实体。

建模的含义

建模的通俗理解:建立模型,展开就是主要是指从现实世界中抽象出我们的目标,在这一过程中,保留相关因素,剔除无关因素,从而直观地表示出问题。

建模的概念到SystemVerilog(下称“SV”),就更加侧重,SV强调的就是数字系统建模和验证。

而我们使用Verilog和SV的过程就是对数字系统进行建模,最直观的表现就是模块之间是并行执行的,每个模块都实现特定的功能。

模块的描述方式:数据流建模、行为建模、结构建模

我们知道Verilog模型可以是实际电路的Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

- 系统级(system):用高级语言结构(如case if...else...)实现设计模块的外部性能的模型(在设计时只需要知道输入输出的真值表,就可以写出相关的描述)。

- 算法级(algorithm):用高级语言结构实现设计算法的模型(写出逻辑表达式)。

- RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

- 门级(gate-level):描述逻辑门(与或非)以及逻辑门之间的连接的模型。

- 开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

接下来我们在来看下几种模块的描述方式(建模):数据流建模、行为建模、结构建模,更细分的话个人觉得状态机建模也是其中一类,但是这些不是我们讨论的范围就不展开讨论了。

- 数据流描述:采用assign连续赋值语句

- 行为描述:使用always语句或initial语句块中的过程赋值语句

- 结构化描述:实例化已有的功能模块或原语

下面以一个4位加法器(全加器)为例帮助大家去理解。

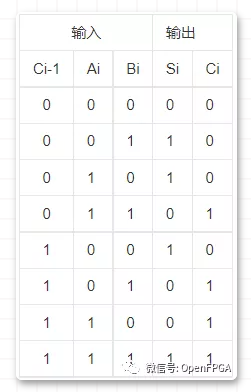

全加器的真值表如下(一位的):

全加器的真值表

数据流描述

module Full_Add_4b_1( A, B, Cin, Sum, Cout );

input[3:0] A;

input[3:0] B;

input Cin;

output[3:0] Sum;

output Cout;

assign {Cout, Sum} = A + B + Cin;

endmodule行为描述

module Full_Add_4b_2( A, B, Cin, Sum, Cout );

input[3:0] A;

input[3:0] B;

input Cin;

output[3:0] Sum; output Cout;

reg [3:0] Sum;

reg Cout;

always @(A or B or Cin)

begin

{Cout, Sum} <= A + B + Cin;

end

endmodule结构化描述

`include "Full_Add_4b_1.v"

module Full_Add_4b_3( A, B, Cin, Sum, Cout );

input[3:0] A;

input[3:0] B;

input Cin;

output[3:0] Sum;

output Cout;

//实例化全加器

Full_Add_4b_1 FA4b1( A, B, Cin, Sum, Cout );

endmodule上面就很容易理解了各种建模的区别,接下来再简单分析一下Verilog五种抽象级别和这三种建模方式的区别:从抽象级别的定义可知,这种抽象级别其实是指对同一个物理电路用Verilog不同层次(系统级、算法级、RTL级、门级、开关级)语言来描述的不同方式,比如现在需要一个4位全加器,那么可以通过最最底层的三极管、MOS管去搭建(这种方式是早期的一种实现方式,现在很少用了)、门电路搭建、RTL描述、算法级描述、系统级描述来实现。

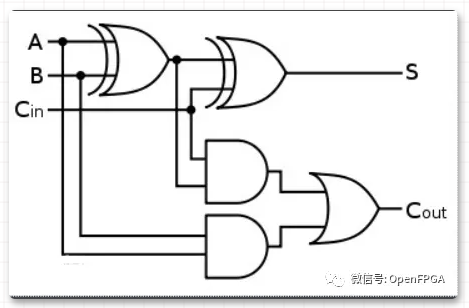

门电路搭建的一位全加器架构

门电路实现的触发器

module flop(data,clock,clear,q,qb);

input data,clock,clear;

output q,qb;

nand #10 nd1(a,data,clock,clear),

nd2(b,ndata,clock),

nd4(d,c,b,clear),

nd5(e,c,nclock),

nd6(f,d,nclock),

nd8(qb,q,f,clear);

nand #9 nd3(c,a,d),

nd7(q,e,qb);

not #10 iv1(ndata,data),

iv2(nclock,clock);

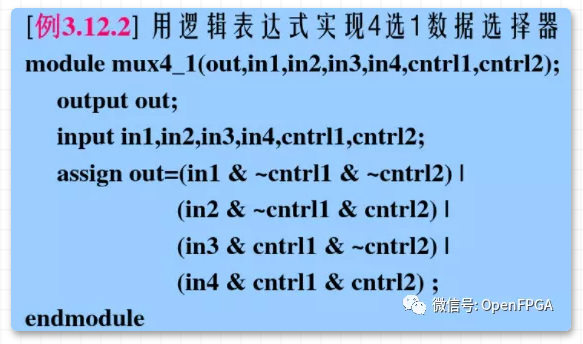

endmodule算法级描述-各种逻辑表达式

算法级描述举例

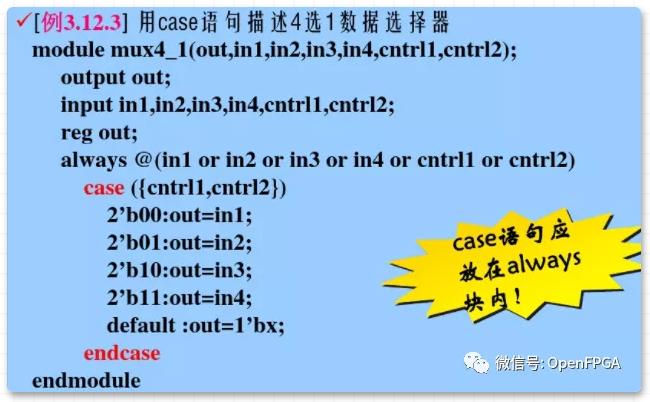

系统级描述-各种高级的语法结构,本例是case

系统级描述举例

综上,我们还可以将模块分为行为模块(只从行为功能的角度来描述某一电路模块)和结构模块(从电路结构的角度来描述该电路模块)这些就不深入展开了。

总结

上面说了很多不相关的话题,我们最后来个“点睛之笔”,总结一下:

1、每个.v文件都是以module开始......endmodule结束关键是Verilog侧重的是对数字电路的建模,所以他没有像C一样以main作为核心;

2、我们平时写一个程序的过程其实是利用Verilog的五种抽象级别的组合进行整个模块的建模过程;

3、理解这一过程很重要。

4、以上理解纯属个人见解,如有错误欢迎指正。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏。