0 官网

https://www.spi-inc.org/

https://www.2spi.com/

Software in the Public Interest (SPI) 是一家在纽约州注册的非营利性公司,其成立的目的是为开发开源软件和硬件的组织提供财政赞助。我们的使命是通过处理非技术性管理任务来帮助大量和重要的开源项目。

Software in the Public Interest 于 1997 年 6 月 16 日在纽约州成立的非营利组织。

1999 年,美国政府的国税局确定,根据国税法典第 501 (a) 条,SPI 符合第 509 (a) (1) 条规定的 501 (c) (3)(非营利组织)地位) 和 170 (b) (1) (A) (vi)。这意味着对 SPI 及其支持项目的所有捐赠都可以为美国的捐赠者免税。

1 opencores SPI

https://opencores.org/projects/spi_verilog_master_slave

https://opencores.org/projects/spi_master_slave

https://opencores.org/projects/simple_spi

上面的项目包括VHDL和Verilog项目,最大的 SPI 时钟 (sck) 频率为 112MHz,下面是一个测试数据:

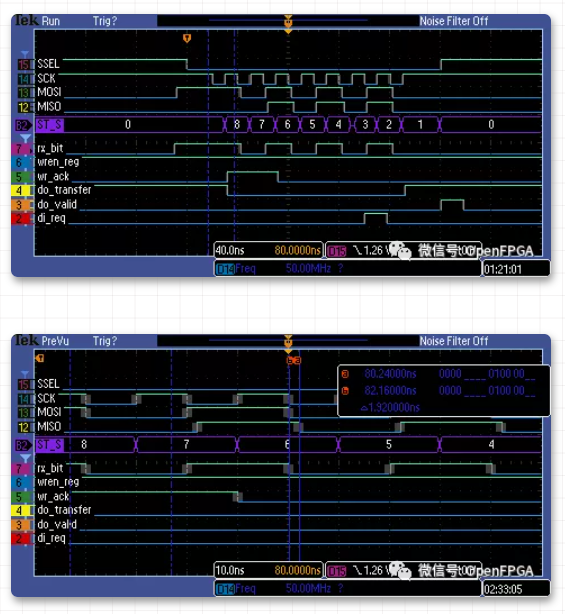

下面的示波器显示了SPI CPOL=1、CPHA=1 。调试信号显示读/写端口的从属内部状态和从属流控制信号。spi_master 和 spi_slave 内核在 FPGA 硬件中以 100MHz(50MHz spi 时钟)进行验证,SCK-to-MOSI 延迟为 0ns,SCK-to-MISO 延迟小于 2ns。在这个例子中,slave 与 wren_i 一起使用。并行输入数据在传输开始时从 di_i 采样,直到第一个 SPI SCK 边沿。对于连续传输,在状态 1 的每个下降沿再次对 di_i 处的数据进行采样。

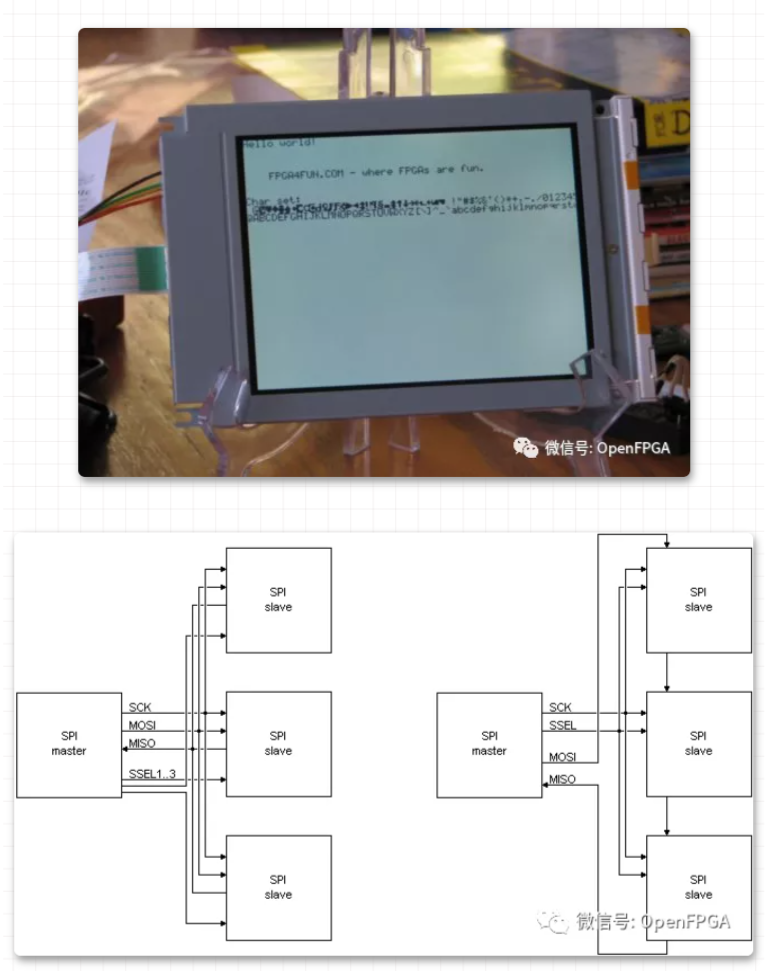

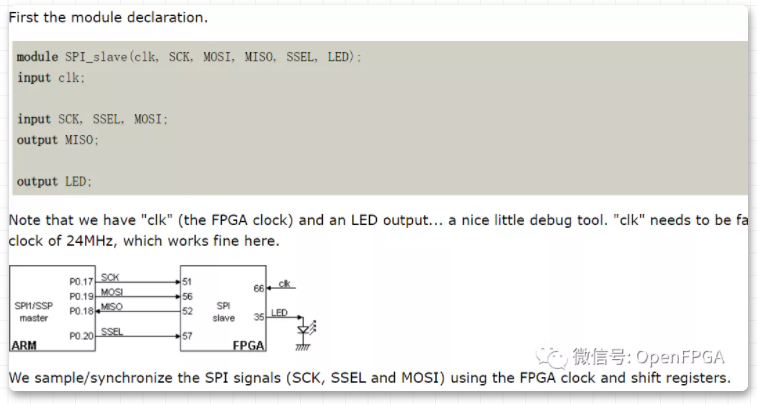

2 fpga4fun spi

https://www.fpga4fun.com/SPI.html

详细的设计过程

3 spi slave

https://github.com/nandland/spi-slave

https://github.com/mjlyons/vSPI

spi-slave

可以在 Atlys FPGA 开发套件(具有 100 MHz 系统时钟的 Spartan-6)上以 27.9 mbps 的速度可靠地传输数据。

4 drom SPI flash memory

https://github.com/drom/spi

特性:

- 8、16、32、64 位可配置

- 可配置的缓存、条目、关联性

- 单、双和四位 SPI

- 多芯片支持

- 可配置的时钟相位

- XIP 模式支持

- 双倍数据速率 (DDR) 选项

支持的IC

Spansion S25FL{004|008|016}K

Spansion S25FL{116|132|164}K {16|32|64} Mib / 108MHz

Spansion S25FL216K 16 Mib / 65MHz

Spansion S25FL{128|256}S {128|256} Mib / 133MHz

Micron N25Q128A

Micron N25Q256A

Windbond W25Q20EW

ON Semi LE25S81A

ESMT F25D64QA

AMIC A25LQ080

GeneralPlus GPR25L3203F

Macronix MX25L4006E5 sergachev spi_mem_programmer

https://github.com/sergachev/spi_mem_programmer

针对N25Q128内存。可以读取内存芯片 ID、启用 quad SPI 模式、禁用写保护、擦除扇区、进行批量擦除、编程页面和轮询状态寄存器。

PS:本项目使用了Vivado Xilinx原语,所以通用性不强

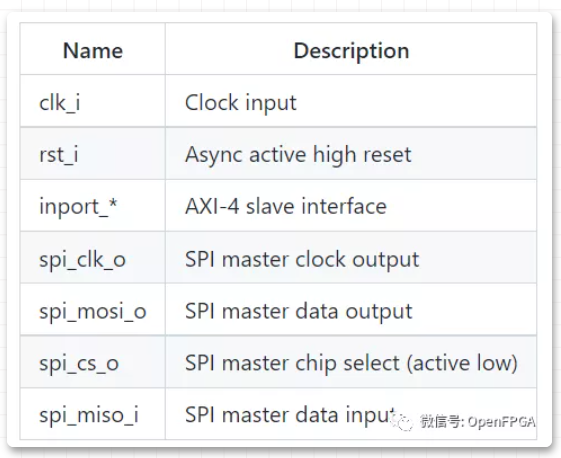

6 AXI to SPI FLASH

https://github.com/ultraembedded/core_spiflash

一个基本的 AXI4 到 SPI 闪存接口(1 位只读模式)。用于执行存储在 FPGA 配置 SPI PROM 中的引导加载程序。

接口

特征

- 一位 SPI 闪存支持(3 个地址周期)。

- AXI4 从设备支持单次和突发传输。

- 支持支持读取页面命令 (0x03) 的 SPI-Flash 设备。

- 仅支持 CPOL=0、CPHA=0 SPI(模式 0)。

- 在仿真并验证在 FPGA(XC7A35T 和 N25Q64A SPI-PROM)上。

7 SPI FLASH控制器

https://github.com/opalkelly-opensource/SPIFlashController

https://github.com/BNUGYX/Verilog_spi_flash

这是一个 SPI 闪存控制器,旨在连接基本的 FIFO 接口和 SPI 闪存设备。。

该控制器已在具有多个设备的FPGA 硬件中得到验证 。

8 开源板卡上的SPI FLASH控制器

https://github.com/osresearch/spispy

SPI Spy 是一个开源(硬件和软件)SPI 闪存仿真工具。它可以在连接到 FPGA 的 SDRAM 中存储闪存映像,并通过 SPI 总线将映像提供给主机 CPU。

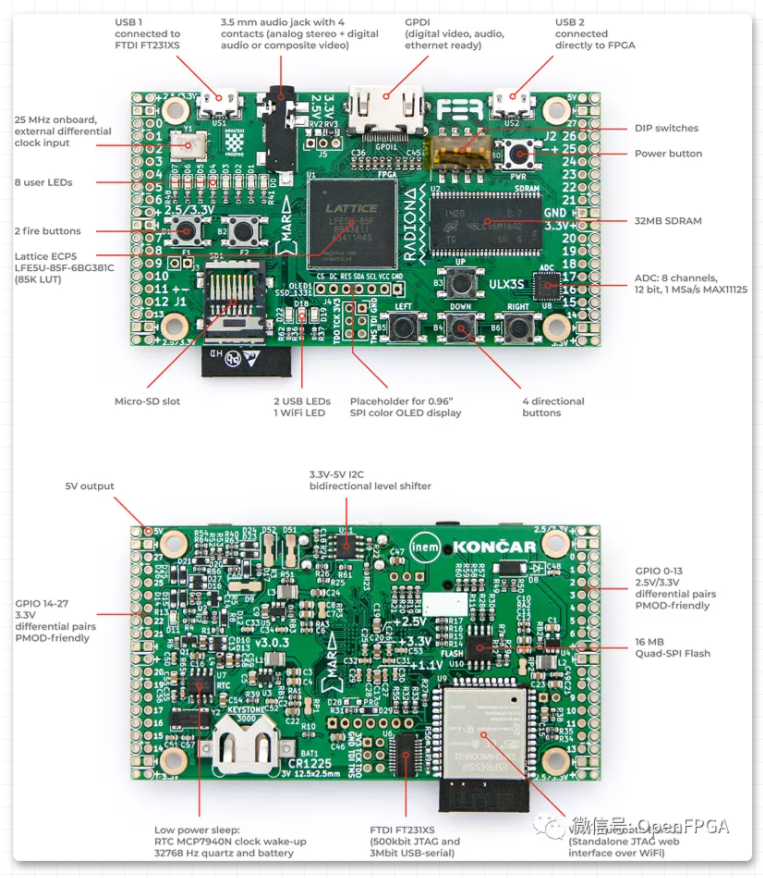

平台

- ULX3S(https://radiona.org/ulx3s/)

- TinyFPGA-EX(https://github.com/tinyfpga/TinyFPGA-EX)

- ECP5 板

支持的功能

- 单 SPI 高达 20 MHz 时钟

- 3 字节寻址(最多 16 MB 闪存映像)

- 高速 (1 MB/s)/dev/ttyACM0接口

- TOCTOU 根据读取模式更改闪存映像 ...

尚不支持

- 双和四 SPI

- 多个!CS引脚(无法扩展)

- 快速读取命令

- 块保护位 ...

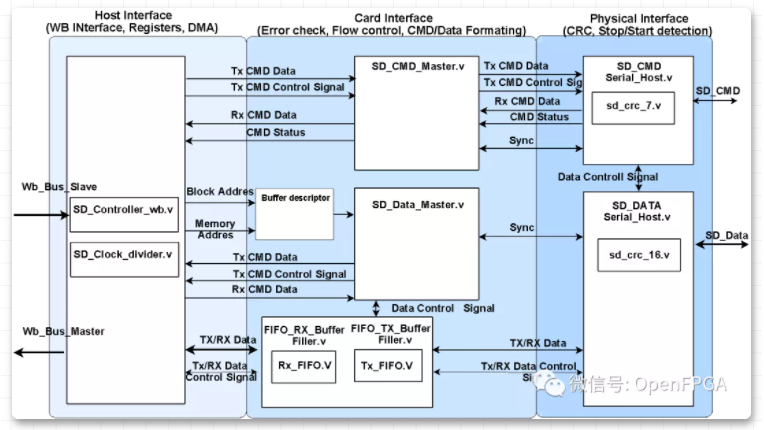

9 SD-Card controller

https://github.com/ZipCPU/sdspi

与其他提供完整 SD 接口(OpenCores SD 卡控制器)不同,该控制器专注于 SD 卡的 SPI 接口。虽然这是一个较慢的接口,但在一般情况下,在没有实现到 SD 卡的完整 9 位双向接口时,必须使用 SPI 接口来访问卡。此外,对于那些顽固的 Verilog 作者来说,这个核心是用 Verilog 编写的,而不是在 GitHub 上找到的XESS 提供的演示 SD 卡控制器(用 VHDL 编写的)。对于那些不是这种顽固的 Verilog 作者的人来说,该控制器为卡提供了比其他控制器更低级别的接口。尽管 XESS 控制器会自动启动卡并与之交互,但该控制器在与卡交互时需要使用外部软件。这使得这个 SD-SPI 控制器在面对卡接口的潜在变化时更加通用。

10 SD卡控制器

https://opencores.org/projects/sdcard_mass_storage_controller

重点是为 SD/SDHC 卡提供快速简单的接口。该项目的主要目标之一是控制器应可用作包含文件系统的系统磁盘。

https://github.com/xesscorp/VHDL_Lib

XESS VHDL 库文件,包含很多开源的VHDL接口文件,不止SD卡这一开源项目。

https://www.fpga4fun.com/SD.html

fpga4fun上的项目 包括SPI和高速模式两种。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。