写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释(使用斜体表示),转自:

http://blog.chinaaet.com/justlxy/p/5100053328

转载正文

链路初始化与训练基础(一)

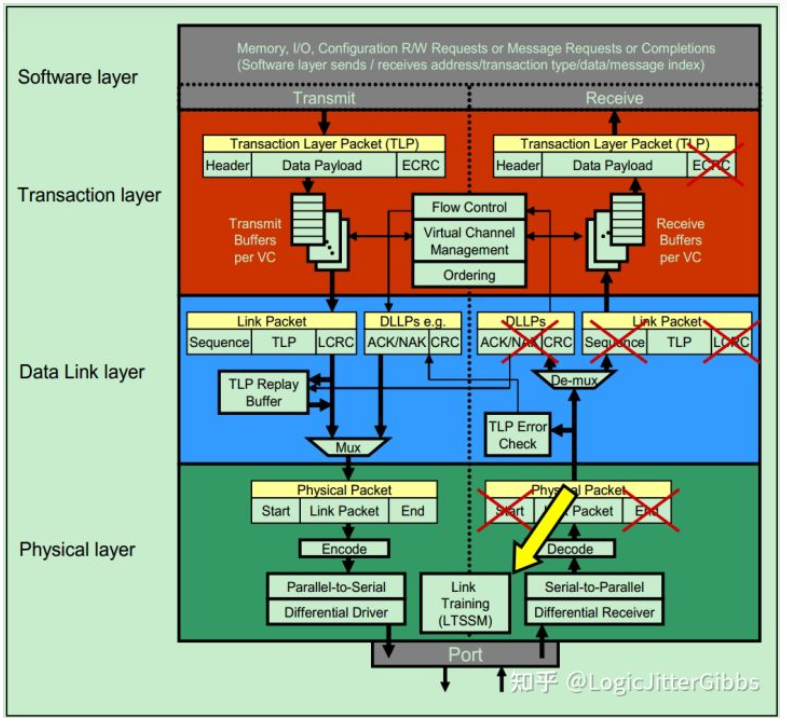

PCIe总线中的链路初始化与训练(Link Initialization & Training)是一种完全由硬件实现的功能,处于PCIe体系结构中的物理层。整个过程由链路训练状态机(Link Training and Status State Machine,LTSSM)自动完成,也就说基本没有数据链路层和事务层啥事。

LTSSM在PCIe体系结构中的位置的示意图如下:

在系统复位后,会自动进行链路训练,以达成以下目标:位锁定(Bit Lock)、字符锁定(Symbol Lock,Gen1 & Gen2 Only)、块锁定(Block Lock,Gen3 Only)、确定链路宽度(Link Width)、通道位置翻转(Lane Reversal)、信号极性翻转(Polarity Inversion)、确定链路的数据率(Data Rate)和通道对齐(Lane-to-Lane De-skew)等功能。

下面依次的,简要地介绍一下这些目标。

注:本次连载博文主要Gen2为主,所以一些和Gen3相关的内容只会简单提及,并不会深入地介绍,有兴趣的可以阅读PCIe Spec V3.0或者Mindshare的相关书籍。

首先是位锁定(Bit Lock):

前面的文章中提到过,PCIe总线采用了一种嵌入式时钟的机制,即发送端只向接收端发送数据信号,并不发送时钟信号(时钟信号隐藏在数据信号中)。接收端可以通过CDR(Clock and Data Recovery)逻辑将时钟从数据流中恢复出来,然后再用恢复出来的时钟对数据信号进行采样。当然,时钟恢复需要一定的时间,才能保证时钟信号与数据信号的相位对应关系符合要求。一旦CDR完成了时钟的恢复,我们就说PCIe总线完成了位锁定。

字符锁定(Symbol Lock):

完成了位锁定之后,只是能够准确地识别出数据流中的0和1,还是不知道发送的内容是个啥。对于Gen1&Gen2来说,采用的8b/10b编码,即传输的数据是以10bit为一个字符。LTSSM可以引导物理层相关逻辑通过识别COM(K28.5)等控制字符来确定每个字符的开始与结束为止,即字符锁定。

链路宽度(Link Width):

由于PCIe允许将x1的PCIe卡插入x4、x8甚至是x16的PCIe插槽中。因此在链路训练与初始化过程中,相邻的两个PCIe设备需要相互通信来确定其支持的最大链路宽度。

注:实际上PCIe Spec还允许采用动态带宽的机制,即允许链路宽度和数据率动态调整,以实现降低功耗等功能。

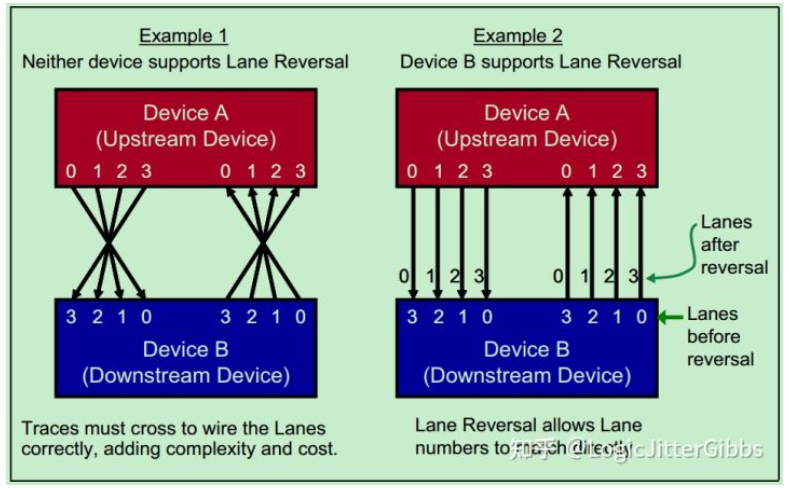

通道位置翻转(Lane Reversal):

有的时候两个PCIe设备的通道排列位置可能不太一致,PCIe Spec允许对默认的通道排列位置重新排列,如下图所示。但是,从大部分的PCIe设备(PCIe卡和插槽等)都是按照统一的标准实现的,一般不会出现这种情况,因此这一功能是可选的。

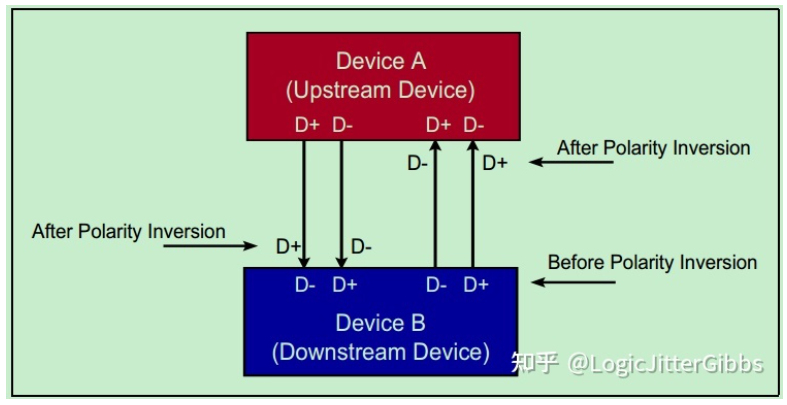

信号极性翻转(Polarity Inversion):

前面的文章中介绍过,PCIe收发的都是差分信号,有的时候Link两端的设备的对应信号的极性可能是相反的。因此,PCIe Spec允许在链路训练与初始化的时候,对其进行调整,如下图所示。和通道位置翻转(Lane Reversal)不一样的是,信号极性翻转(Polarity Inversion)并不是一个可选项,而是所有标准PCIe设备都应支持的。

链路的数据率(Data Rate):

系统刚复位的时候,链路训练和初始化都是基于2.5G T/s的速率的。如果Link两端的设备都支持更高的速率,则会自动进入Re-training状态,以重新切换速率。

注:PCIe Spec规定,高速率的PCIe设备必须能够向下兼容。即Gen2必须同时支持2.5G T/s和5G T/s。

通道对齐(Lane-to-Lane De-skew):

PCIe链路完成字符锁定后,还需要进行通道对齐。因为有的通道的信号可能先到达,有的可能后到达。PCIe Spec规定PCIe链路应有能力对一定范围了的Lane-to-Lane Skew进行移除,使得各个Lane上的信号是同步的。关于通道对齐,会在后续的博文中详细地介绍。

链路初始化与训练基础(二):TS1OS和TS2OS

前面的文章中提到过,Ordered Sets分别有以下几种:

TS1 and TS2 Ordered Set (TS1OS/TS2OS)、

Electrical Idle Ordered Set (EIOS)、

FTS Ordered Set (FTSOS)、

SKP Ordered Set (SOS)和Electrical Idle Exit Ordered Set (EIEOS)。

其主要用于链路初始化与训练等功能。在介绍LTSSM之前,先来简单地介绍一下Ordered Sets中的TS1OS和TS2OS。

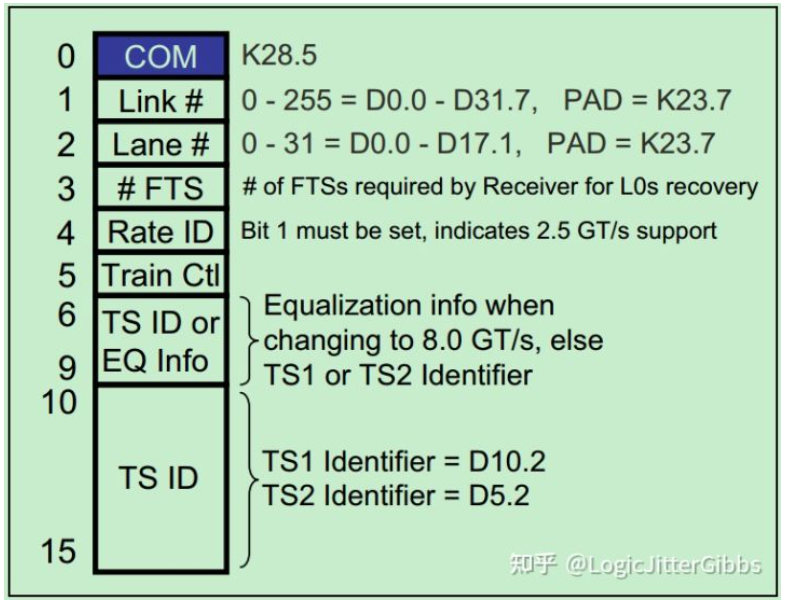

TS1OS和TS2OS类似都是由16个Symbol组成(10bit,8b/10b编码之后的Byte),其结构图如下图所示:

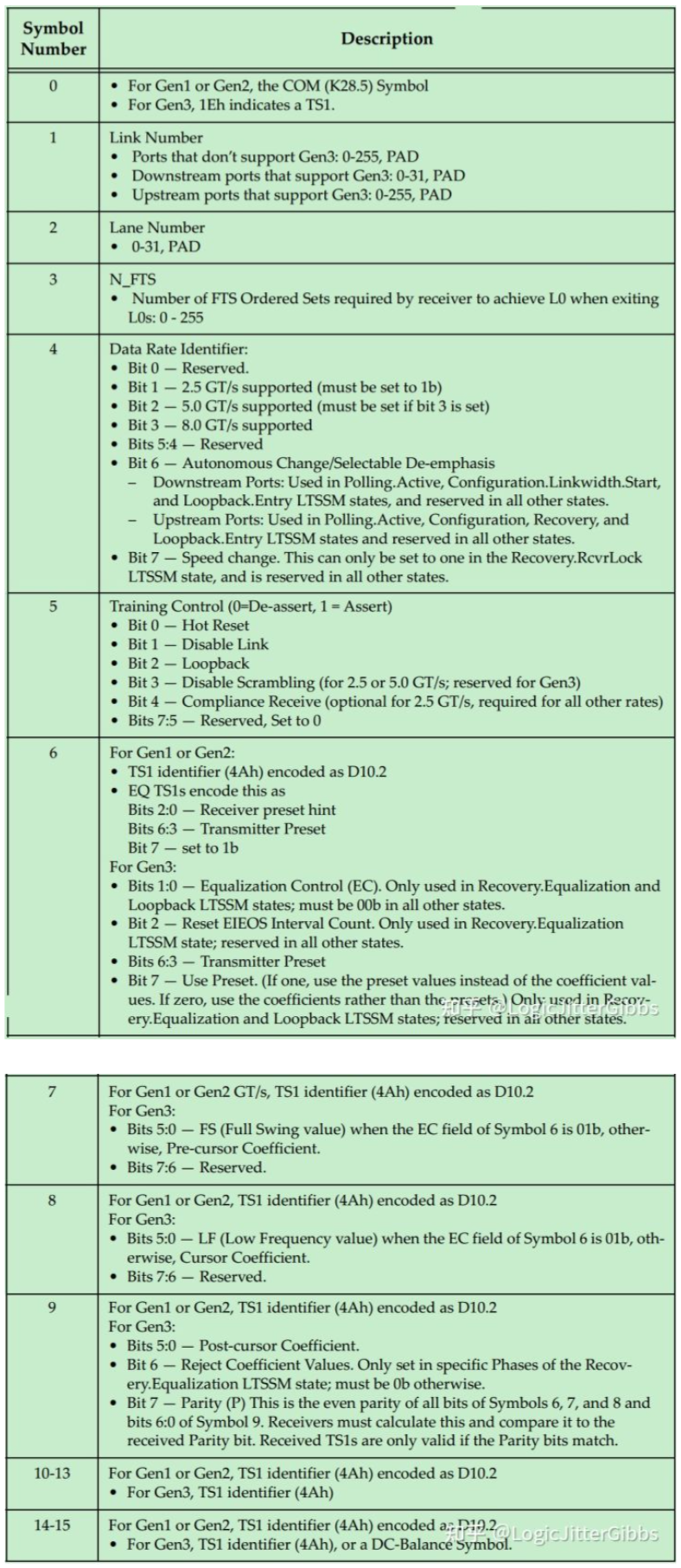

其中,TS1OS的详细内容如下表所述:

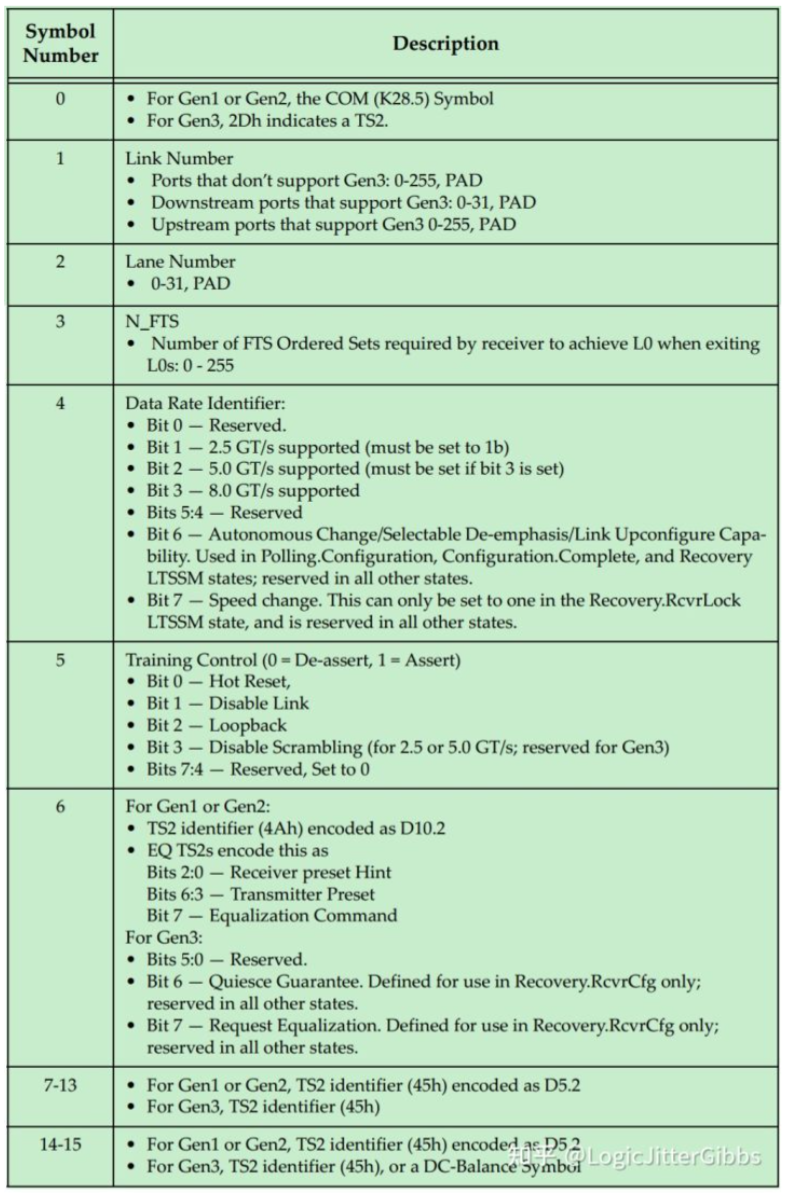

TS2OS的详细内容如下图所示:

链路初始化与训练基础(三)

这一篇文章来简单地介绍一下链路训练状态机(Link Training and Status State Machine,LTSSM),并简要地介绍各个状态的作用和实现机制。

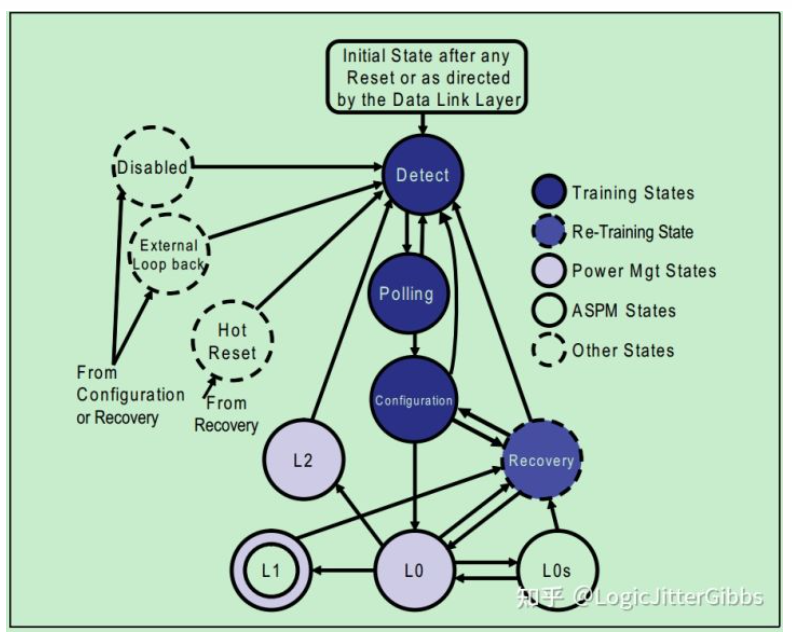

LTSSM有11个状态(其中又有多个子状态),分别是Detect、Polling、Configuration、Recovery,L0、L0s、L1、L2(L3是可选的)、Hot Reset、Loopback和Disable状态。

系统进行复位操作(Cold, Hot or Warm Reset)后,会自动进入Detect状态。

这11个状态又可以被分为以下五个类别:

- 1、链路训练状态(Link Training State);

- 2、重训练状态(Re-Training(Recovery) State);

- 3、软件驱动功耗管理状态(Software Driven Power Management State);

- 4、活动状态功耗管理状态(Active-State Power Management State,ASPM State);

- 5、其他状态(Other State);

如下图所示:

下面分别简要地介绍一下各个状态:

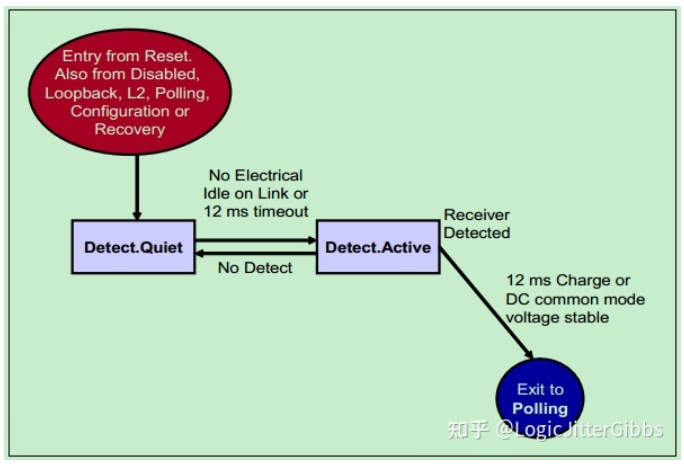

首先是Detect:

前面说到,系统进行复位操作(Cold, Hot or Warm Reset)后,会自动进入Detect状态。

在这个状态中,PCIe设备会去检测自己Link的另一端是否存在其他PCIe设备。换句话说,就是检测有没有其他的PCIe设备与其相连接。如下图所示:

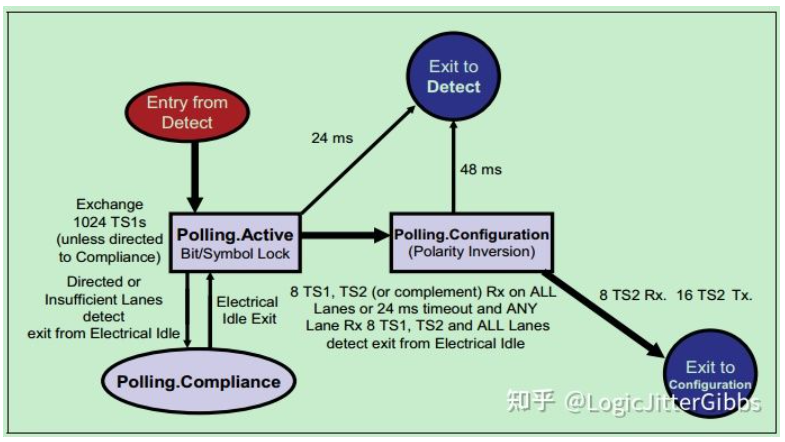

Polling:

在该状态中,PCIe设备会依次发送TS1OS和TS2OS以实现以下目标:

- 1、位锁定(Bit Lock);

- 2、字符锁定(Symbol Lock);

- 3、信号极性翻转(Polarity Inversion),如果需要的话;

- 4、确定各个设备支持的速率(Data Rates)。

如下图所示:

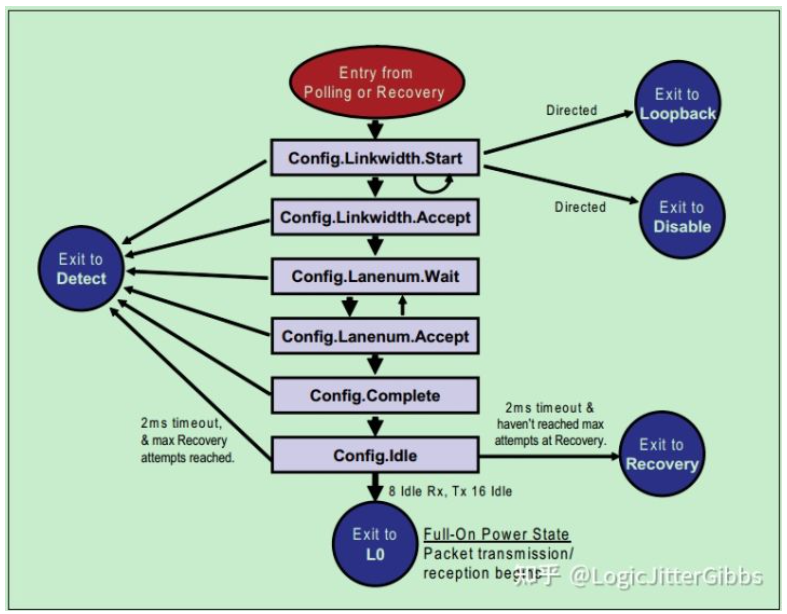

Configuration:

在该状态中,PCIe设备会依次发送TS1OS和TS2OS以实现以下目标:

- 1、确定链路宽度(Link Width);

- 2、分配通道(Lane)号;

- 3、通道位置翻转(Lane Reversal),如果需要的话;

- 4、通道对齐(Lane-to-Lane De-skew)。

如下图所示:

L0:

这是链路(Link)的正常状态(Normal and Full-Active State),所有的TLP、DLLP和Ordered Sets都可以被正常的收发。

该状态下,速率可以是2.5GT/s或者是5GT/s(如果链路两端设备都支持的话,且经过了Re-Trainning)。

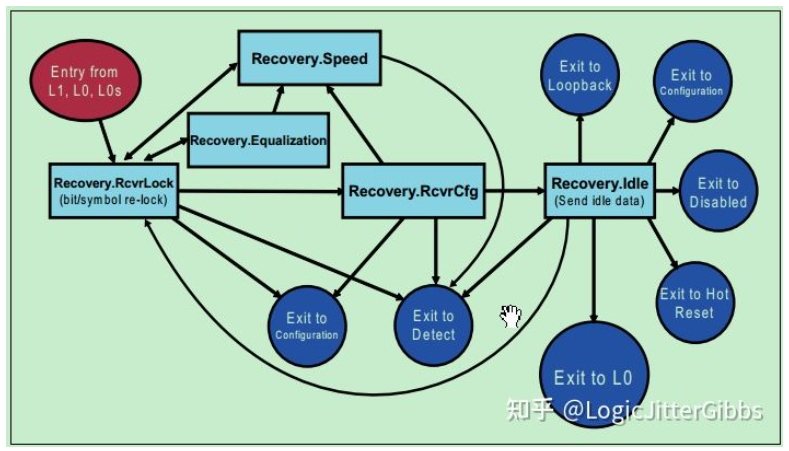

Recovery:

这个状态用于Re-Trainning,因此Re-Trainning可能会改变原有的速率,所以位锁定(Bit Lock)和符号锁定(Symbol Lock)操作都会被重新进行,但是花费的时间要比第一次少很多。

其内部的子状态转移图如下图所示:

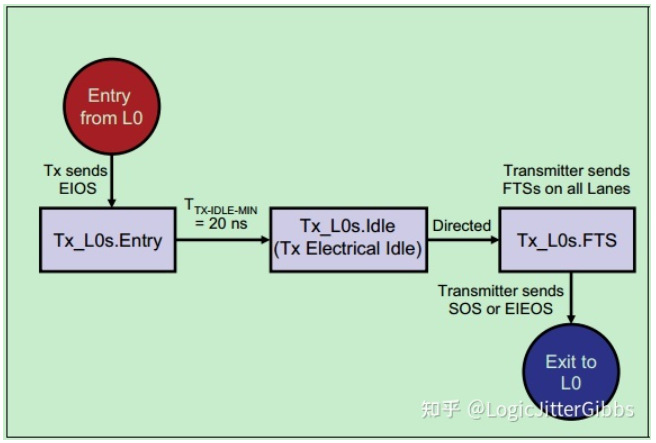

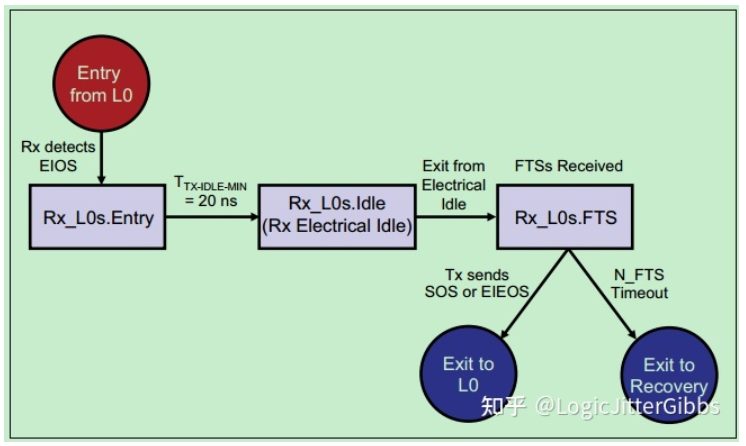

L0s:

该ASPM状态主要用于降低功耗,在总线空闲的时候可以进入该状态,且从该状态可以迅速地重新切换回L0状态。当在L0状态是,链路上出现EIOS时,则表明即将进入L0s状态。

当在L0s状态时,链路上出现FTS时,链路会迅速地完成位锁定和符号锁定,并进入L0状态。

发送端如下图所示:

接收端的示意图如下:

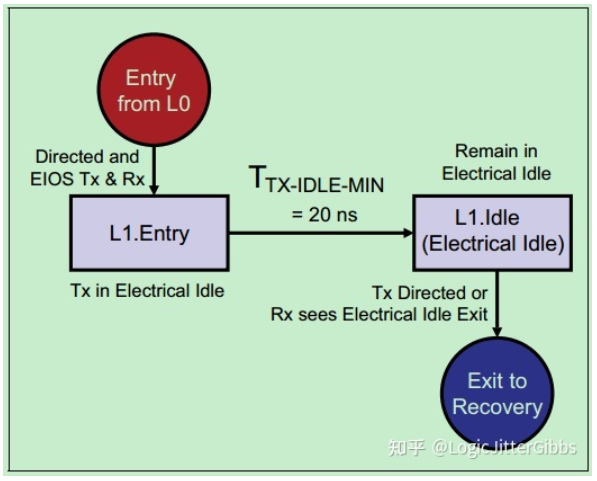

L1:

相对于L0s状态,L1状态下的功耗更低。进入L1状态需要链路两端的PCIe进行“沟通”,只有双方都“同意”进入该状态,链路才会进入该状态。一般有以下两种方式:

1、第一种是由ASPM引导,硬件自动完成的。发送端发现链路上长时间没有TLP或者DLLP时,便通过ASPM建议接收端进入L1状态。如果接收端“同意”了,则链路进入L1状态;如果接收端“不同意”,则链路进入L0s状态。

2、第二种是有软件引导的,软件发送一系列的命令让链路进入低功耗状态(D1,D2,or D3 Hot)。随后,链路的上端设备会通知下端设备进入L1状态,收到来自下端设备的应答后,链路进入L1状态。

如下图所示:

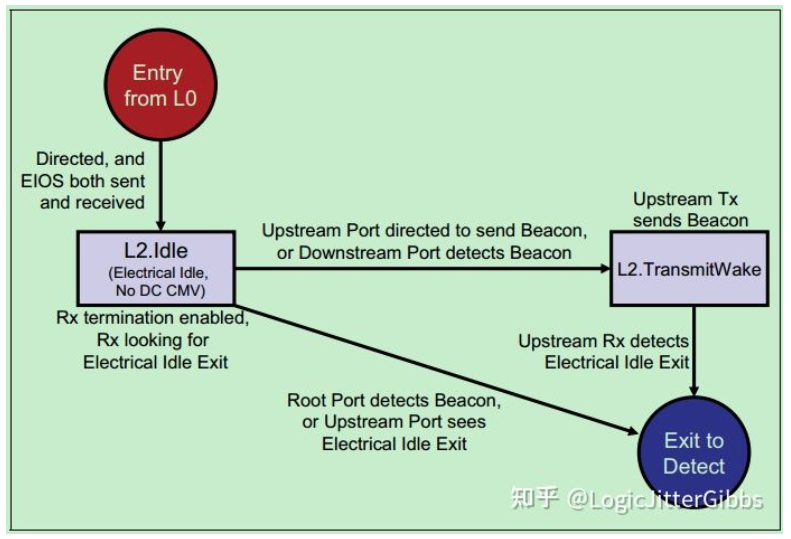

L2:

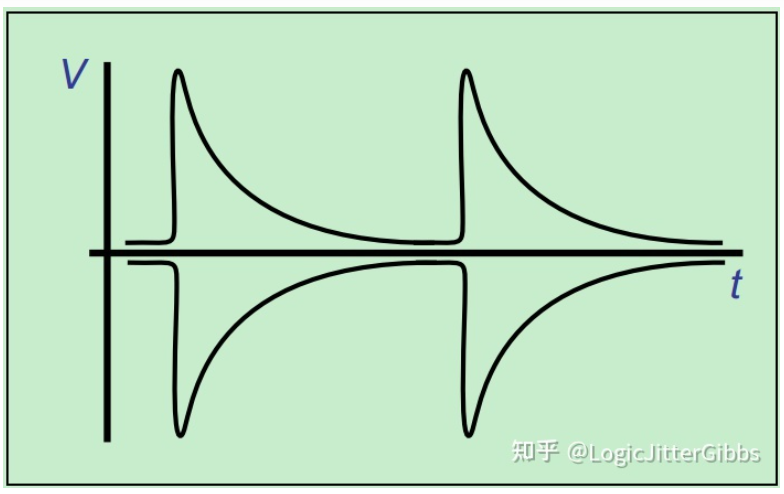

L2状态下的链路功耗更低,因为其只保留了Vaux,关闭了链路的其他功能。此时,需要Beacon信号或者WAKE#边带信号来唤醒系统。其中Beacon信号是一种低频信号(30KHz~500MHz),其波形图如下图所示:

注:此外,还有一个L3状态,不过其实际上已经不属于LTSSM了。由于L3状态连Vaux都关闭了,一旦进入L3状态,实际上和直接关闭PCIe设备的电源没有什么太大的差别了。

L2的子状态转移图如下图所示:

Loopback:

该状态主要用于测试,这里就不详细介绍了。

Disable:

该状态中链路被禁止,此时发送端处于电气空闲状态(Electrical Idle State),而接收端处于低阻状态(Low Impedance State)。进入该状态的原因可能是链路连接不稳定,或者链路中的某个设备被移除,如PCIe卡从插槽中拔出。

Hot Reset:

软件可以通过将桥控制寄存器(Bridge Control Register)中的Secondary Bus Reset位置位来复位链路。随后,桥下端的PCIe设备发送TS1OS,其中的Training Control中包含了Hot Reset的信息。当接收端发现连续的两个TS1OS中都包含Hot Reset时,链路随后进入复位状态。

注:本文只是对LTSSM进行了简单的介绍,关于具体的每一个状态内部是如何实现的,请参考PCIe Spec相关章节。

版权声明

版权声明:本文为 AET 博主「Felix」的原创文章,转载请附上原文出处链接及本声明。

原文链接:http://blog.chinaaet.com/justlxy/p/5100053328

转载自:知乎

作者:Felix

推荐阅读

更多招聘及面经请关注FPGA的逻辑。