写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释(使用斜体表示),转自https://blog.csdn.net/weixin_48180416/article/details/115605331

相应内容可参考:

- 《PCI Express 体系结构导读》 第 4.1.5 章

转载正文

PCI Express 复位主要分为两类

- PCI Express Conventional Reset: 传统复位

- Function Level Reset(FLR):功能级复位

PCI Express Conventional Reset: 传统复位,又分为Fundamental Reset和Non-Fundamental Reset.

Non-Fundamental Reset 指 Hot Reset

Fundamental Reset: 基本复位,在硬件中处理,复位整个device,重新初始化状态机、所有的硬件逻辑、Port状态和配置寄存器。

注意:一种特殊情况除外,sticky的寄存器是不能被Fundamental Reset复位的,sticky寄存器受到Aux Power的控制,如果有Aux Power没有Main Power寄存器的值不会丢失,如果所有的power都off了,寄存器的值也会丢失。这些寄存器在诊断链路问题的时候非常有用,重新复位链路使链路能重新工作,error status不会被复位,可以后续报告给软件。

Fundamental Reset又分为Cold reset和Warm reset. Fundamental Reset可以采用auxiliary signal---PERST#.

Cold reset:

应用Main Power时产生的复位。“A Fundamental Reset following the application of main power.”

Warm reset (Optional):

不关闭Main Power时,由硬件产生的复位。(Spec没有定义实现方法)

PCI Express 复位划分

所以整个 PCI Express 复位可以如此划分:

- PCI Express Conventional Reset: 传统复位

- Fundamental Reset

- Cold Reset

- Warm Reset

- Non-Fundamental Reset (Hot Reset)

- Function Level Reset(FLR):功能级复位

Reset 两个很重要的规则:

- Fundamental Reset(PERST#)释放后20ms内LTSSM要进入Detect状态; 如果component释放复位时间不同,各自分别要满足这个要求;

- 2.5GT/s时Fundamental Reset(PERST#)释放后软件至少等待100ms再发起Configuraion Request,

5GT/s及以上时link up后软件至少等待100ms再发起Configuration Request(因为高速时EQ可能会耗费50ms,导致如果从reset开始算100ms可能是不够用的)

注:

1)只有软件使能CRS Software Visibility才能用100ms等待时间,否则会产生Completion timeouts, platform timeouts, or lengthy processor instruction stalls

2)复位释放后的1s内,device必须收到Configuration Request并返回Successful Completion(运用Readiness Notifications会缩短这个时间限制)否则认为是broken device.

Configuration Request Retry Status

以下为关于Configuration Request Retry Status(CRS)的规定:

CRS Software Visibility未使能:

当RC收到CRS的Completion时,RC需要重新发新的请求;

CRS Software Visibility使能:

1) 当RC CfgRd Vendor ID的所有字节(枚举过程),但是收到CRS的Completion情况下,RC返回给host 0001h的Vendor ID,如果有其他字段设为全1,实际上是个假的Vendor ID;可以使软件先处理其他任务,稍后再来询问这个设备;

2) 当RC CfgRd其他字段或CfgWr,RC需要重新发新的请求,可以限制Request-CRS循环到一定数量后报错给host;

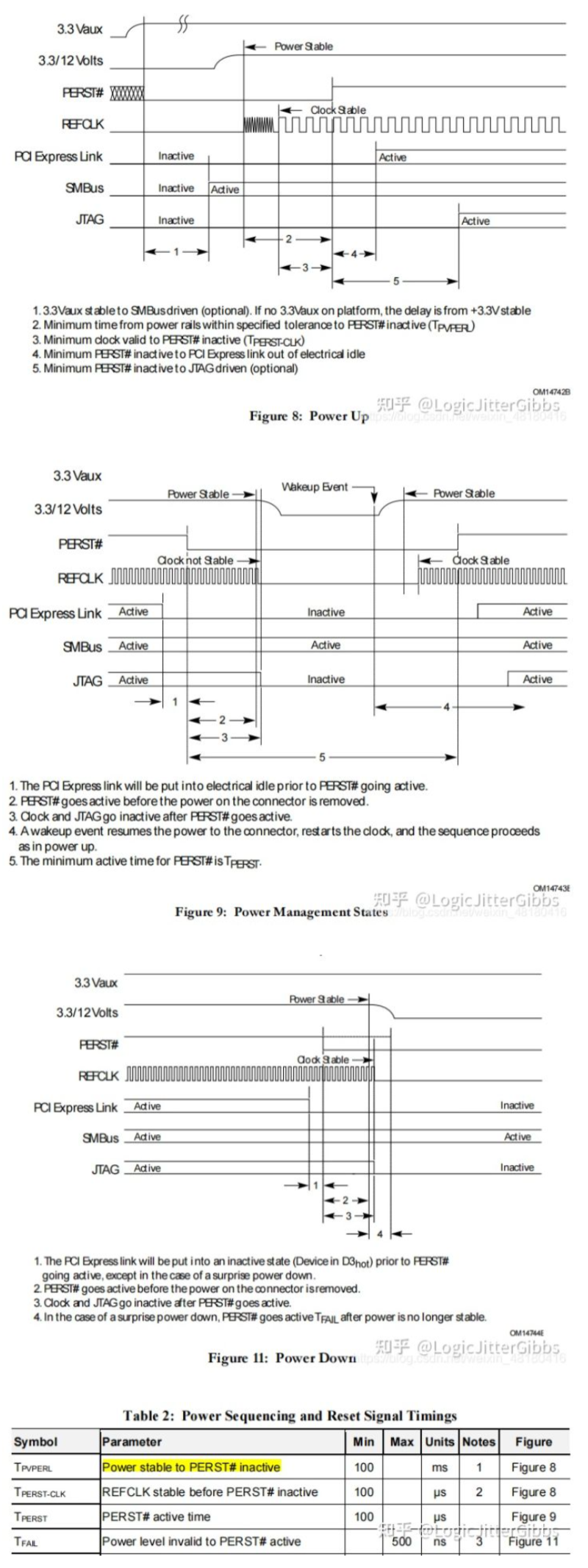

PERST#时序要求

以下为PERST#时序要求(摘自CEM手册):

版权声明:本文为CSDN博主「小雨滴落落」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:PCI Express学习篇---System Reset

转载自:知乎

作者:小雨滴落落

推荐阅读

- PCI Express 学习篇_Power Management(3)

- PCI Express 学习篇_Power Management(2)

- PCI Express 学习篇_Power Management(1)

更多招聘及面经请关注FPGA的逻辑。