写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释,转自https://blog.csdn.net/weixin_48180416/article/details/115576691

相应内容可参考:

- MindShare, PCI Express System Technology 3.0 第十六章。

- 《PCI Express 体系结构导读》 第八章

转载正文

此篇介绍L1低功耗状态。下一篇介绍L1 Substate低功耗状态。

以下详细介绍下进入L1状态的过程,有两种方法:PCI-PM,ASPM

原作者注:当EP和RC相连时,可以简单的理解Upstream Component=RC,Downstream Component=EP, Upstream Port (USP) =EP,Downstream Port (DSP) =RC

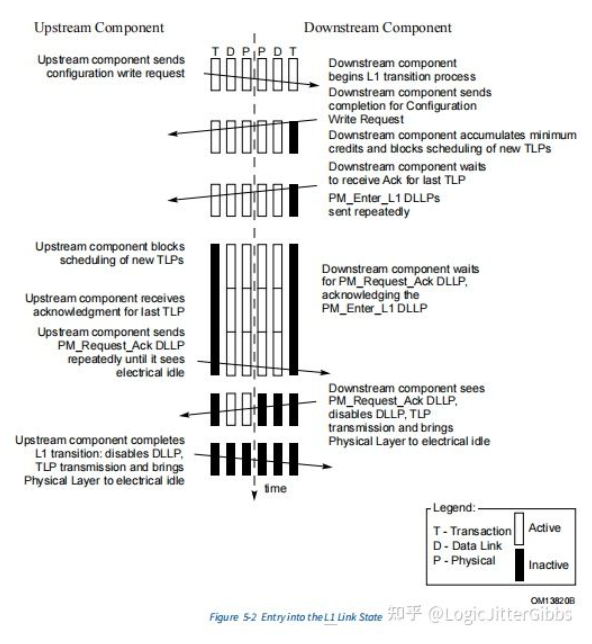

PCI-PM方法:

1) Upstream Component发送CfgWr写PMCSR的PowerState;

2) Downstream Component收到CfgWr后LTSSM状态机进入L1状态,并做一些进入Electrical idle前的准备工作;

3) DLLP包的交互 PM_Enter_L1 DLLP, PM_Request_Ack DLLP, 其中,Upstream Component收到DLLP后也会做一些进入Electrical idle前的准备工作;

4) 双方物理层进入Electrical idle状态,LTSSM进入L1状态。

ASPM方法:

方法一: 支持ASPM L0s,ASPM L1的情况下,链路空闲一段时间后先进入L0s,之后再空闲一段时间后再进入L1,由USP发起,软件只需要配置ASPM相关状态的使能;

方法二:支持ASPM L1,链路空闲一段时间后直接进入L1,由USP发起,软件只需要配置ASPM相关状态的使能;

方法三:支持ASPM L1,软件通过配置USP的寄存器直接发起DLLP,不需要超时后发起;

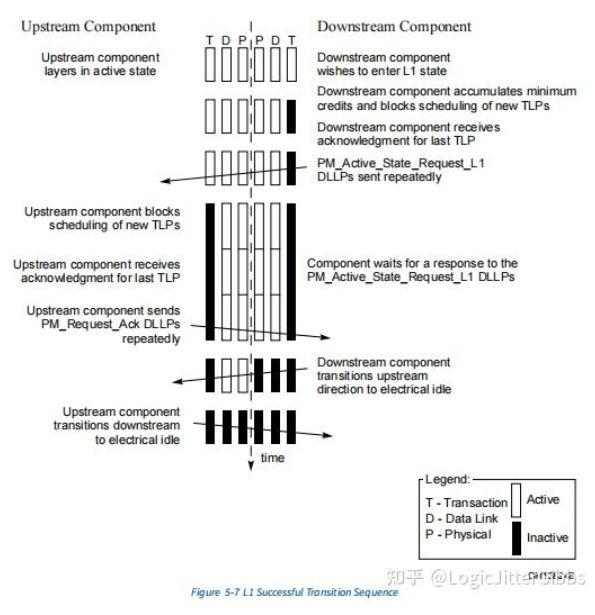

ASPM由USP发起,需要以下协商的过程:

1) USP通过上述三种方法中的一种发起,USP做一些进入Electrical idle前的准备工作;

2) DLLP包的交互 PM_Active_State_Request_L1 DLLP(USP->DSP), PM_Request_Ack DLLP(DSP->USP), 其中,RC收到DLLP后也会做一些进入Electrical idle前的准备工作;

另外,当RC拒绝进入L1时,发送PM_Active_State_Nak message(DSP->USP),双方进入L0s

3) 双方物理层进入Electrical idle状态,LTSSM进入L1状态。

链路层退出 L1 状态

以下详细介绍下退出L1状态的过程有很多方法,其中两种常见的方法:

- Configuration Request

- PME message

DSP和USP任何一方都可以发起退出的操作,并且不需要协商。

DSP发起Configuration Request退出:

- Software发起CfgWr配置USP PMCSR PowerState为D0;

硬件具体过程:

DSP的上层会有pending TLP, 导致DSP PHY的PowerState改变,退出Electrical idle状态,同时发送TS1/TS2序列,LTSSM进入recovery状态;USP检测到退出Electrical idle状态,同样发送TS1/TS2序列,LTSSM进入recovery状态;

- 双方重新link到L0状态,然后CfgWr成功配置到USP的PMCSR。

USP发起PME Message退出:

- USP通过配置寄存器发起PME Message;

硬件具体过程:

USP的上层会有pending TLP, 导致USP PHY的PowerState改变,退出Electrical idle状态,同时发送TS1/TS2序列,LTSSM进入recovery状态;DSP检测到退出Electrical idle状态,同样发送TS1/TS2序列,LTSSM进入recovery状态;

- 双方重新link到L0状态,然后PME Message成功发送给DSP。

- PME Message隐式路由到RC, RC收到后传递给Power Management Controller,然后通过中断通知软件;

- 软件利用PME Message包里面的Requester ID发送CfgRd,清除PMCSR PME_Status,配置PowerState为D0.

物理层进入和退出 L1 状态

以下介绍物理层进入和退出L1的过程

L1状态下包含Transmitter Electrical Idle和Receiver Electrical Idle.

Transmitter进入Electrical Idle:

将发送端的差分电压(TXD+ TXD-)变为0,保持接近于Common mode电压,这样可以降低功耗;

进入Electrical Idle(简称 EI)前先发送EIOS,然后"tri-state output driver"(将TX driver的三态门设为输入)。

有两点需要清楚:

- EIOS的格式:见PCIe Spec 5.0 Table 4-10 Table 4-11

- 为什么需要发EIOS? Receiver通过EIOS可以预知接下来需要进入EI状态

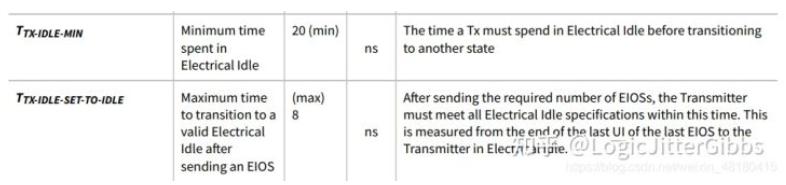

- 进入EI的时间上有什么要求?在PCIe Spec中有以下规定:

- 1) Transmitter发送完EIOS后8ns内进入EI;

- 2) EI至少维持20ns

- 3) EI时差分peak电压为0-20mV

Transmitter退出Electrical Idle:

Gen1: 发送TS1/TS2,Receiver端直接检测电压;

Gen2: 先发送8b/10b Electrical Idle Exit Order Set(EIEOS), EIEOS为低频信号,目的为

- Receiver端检测到退出EI,再发送TS1/TS2;

Gen3及以上速率: 先发送128b/130b Electrical Idle Exit Order Set(EIEOS), EIEOS为低频信号,目的为

- 1) Receiver端检测到退出EI

- 2) Receiver端Recovery状态时建立block alignment,再发送TS1/TS2;

(EIEOS的格式:见PCIe Spec 5.0 Table 4-12)

Receiver进入Electrical Idle:

首先Receiver检测到EIOS后,关闭检测error的逻辑,防止接下来由于链路不可靠报错;

然后Transmitter进入EI后,Receiver根据速率的不同有以下两种方法检测到EI:

- Gen1:直接检测电压小于阈值电压;

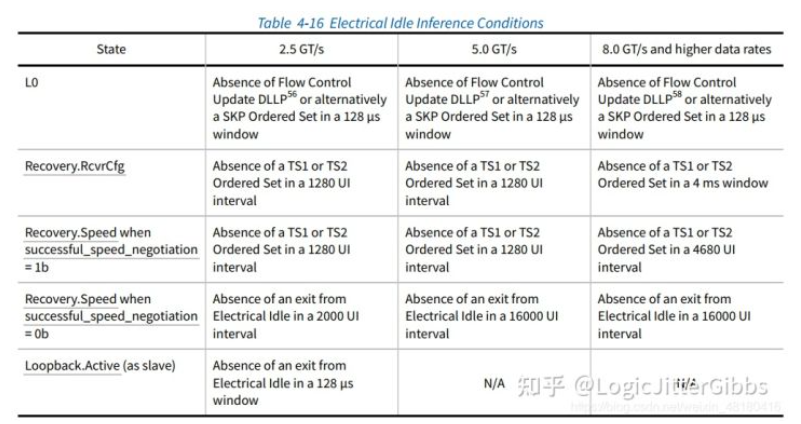

- Gen2及以上: 检测“Inferring Electrical Idle”(隐含是EI的情况),L0状态下缺少Flow Control Update DLLP或SKP Order Set

Receiver退出Electrical Idle:

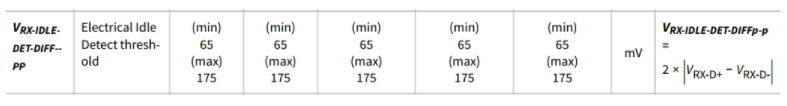

Gen1: Receiver端直接检测电压,大于65-175mV EI detect threshold;

Gen2及以上速率: Receiver检测到EIEOS退出EI,接收到TS1,用于接收端时钟恢复电路CDR重新同步,实现bit lock, symbol lock和block alignment

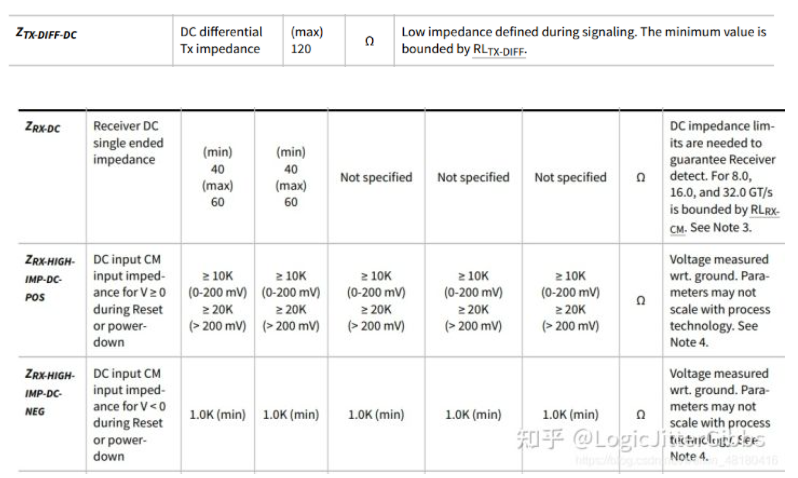

注: EI状态下Transmitter可以处于高阻抗模式或低阻抗模式(关闭或开启termination电路逻辑),接收端必须处于低阻抗模式。

个人理解,高阻抗低阻抗为下表的标准,摘自PCIe Spec Transmitter参数和Receiver参数:

版权声明

版权声明:本文为CSDN博主「小雨滴落落」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:PCI Express学习篇---Power Management(二)

转载自:知乎

作者:小雨滴落落

推荐阅读

更多招聘及面经请关注FPGA的逻辑。