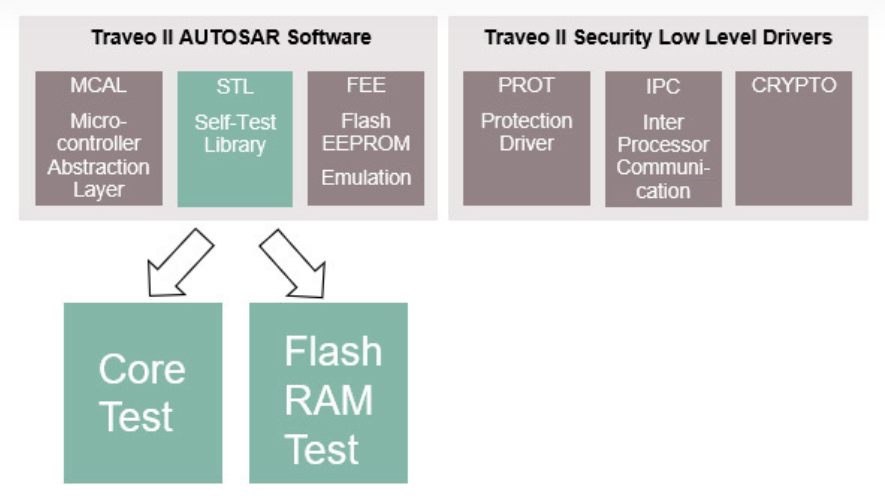

为实现功能安全应用的现代微控制器是非常复杂的设备,为了保证安全系统中,微控制器可以作为其中的一部分并且达到设计的安全等级,需要在硬件与软件中完成必要的功能安全机制与措施,完成必要的集成工作。

微控制器必须支持安全系统的前提假设——提供的功能是可信的,这个可以通过执行硬件诊断机制来支持。本节主要介绍AUTOSAR中硬件诊断是如何被支持的。

Core Test

总体目标是为了检测处理单元可能的故障而导致的不正确的执行结果,Core Test执行的控制单元软件的测试运行在微控制器启动时与运行时。

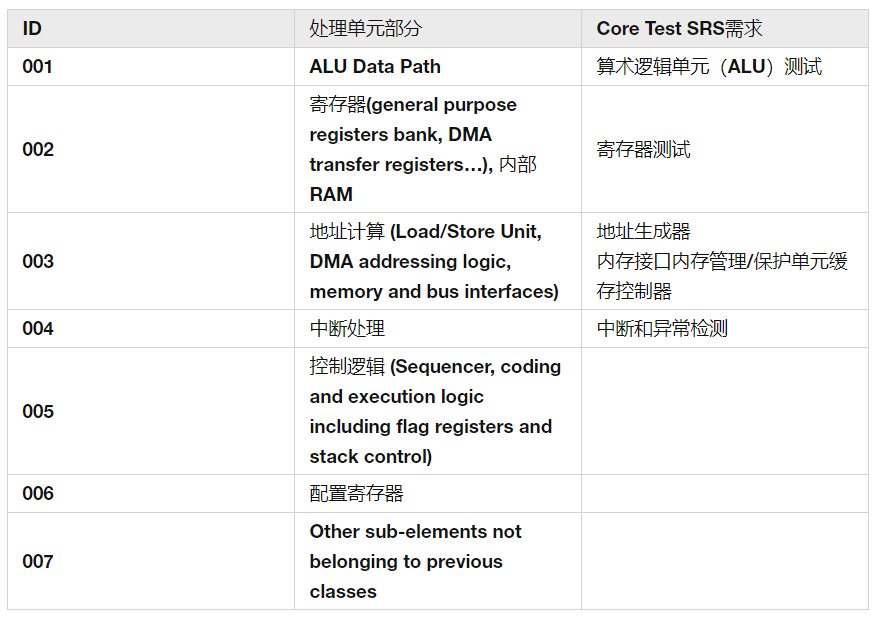

故障模式

根据ISO26262,一般将检测以下处理单元的错误作为诊断覆盖度的考虑条目,这个表格表示ISO26262与Core Test需求的对应关系。

限制

- Core Test不覆盖瞬态故障,Core Test可以用来检测启动和运行时地静态硬件错误。

- Core Test的实现可能仅限于在启动/上电时执行。Core Test需要能够互斥地访问核心资源,避免运行时测试和应用软件之间地非预期的行为和干扰。

- 测试结果仅在执行Core Test的核心上可用。

- Core Test无法保证能够可靠地将检测到地故障进行报告。

RAM Test

RAM Test的目的是检测可能会引发非易失性存储损坏的永久性故障。

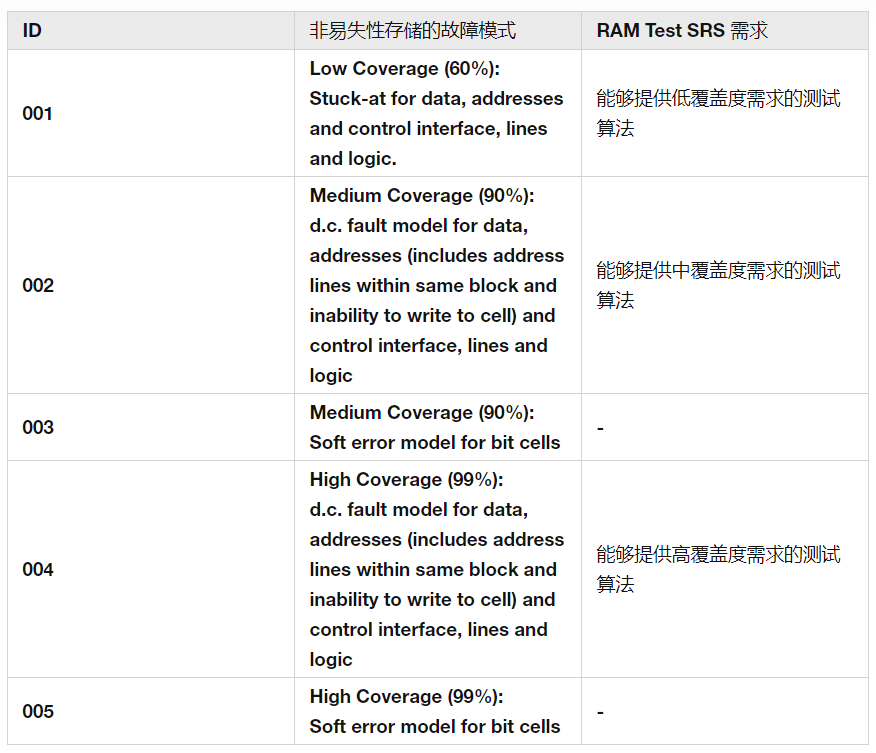

故障模式

根据ISO26262,下列在非易失性存储的故障检测和诊断覆盖度有关,这个表格代表ISO26262和RAM Test需求的对应关系。

RAM Test驱动是AUTOSAR的BSW模块,位于MCAL层,能够直接访问微控制器RAM。

RAM Test执行测试以检测RAM单元的物理健康状况,RAM Test并不检测RAM中存储的内容,用来做寄存器功能用的RAM也在测试范围内。

有多种不同的算法可以用来测试RAM。它们对应于不同的故障模式,能够达到不同等级要求的覆盖度,可以运行在不同阶段,可以是破坏性的(无法恢复之前存储的内容),也可以是非破坏性的。覆盖度与底层物理RAM架构也有关系。ECU安全分析必须进行,以确定需要运行那种覆盖度要求的RAM测试。RAM测试的算法和相关配置参数都在编译时决定。在运行时,应用软件可以选择使用那种编译好的算法。

RAM测试驱动支持被称作为“foreground test”的同步测试方法,也支持被称作为"background test"的异步测试。RAM测试算法的执行期间,不逊于任何其他软件修改正在被测试的RAM区域。

在运行非破坏性测试时,RAM测试模块保存测试RAM区域的内容,测试结束后恢复这些内容。

限制

- RAM测试不包含瞬态故障。RAM测试可以用来检测上电和运行时的静态硬件错误。

- 执行RAM测试算法期间,不允许其他软件和硬件修改正在测试的RAM区域。由于RAM测试不保证数据的一致性,因此RAM测试一般都只在微控制器上电,睡眠,关闭期间运行。

- 破坏性测试可能会修改/破坏正在测试的内存区域。

END

作者: KimChan

来源: https://mp.weixin.qq.com/s/MjbUCwJ1e_d4-v6aJc2mtA

微信公众号:

推荐阅读:

更多汽车电子干货请关注汽车电子与软件专栏。