DDS原理

直接数字频率合成技术(Direct Digital Synthesis,DDS)是一种从相位概念出发直接合成所需要的波形的新的全数字频率合成技术,该技术具有频率分辨率高、频率变化速度快、相位可连续性变化等特点,在数字通信系统中被广泛采用,是信号生成的最佳选择。

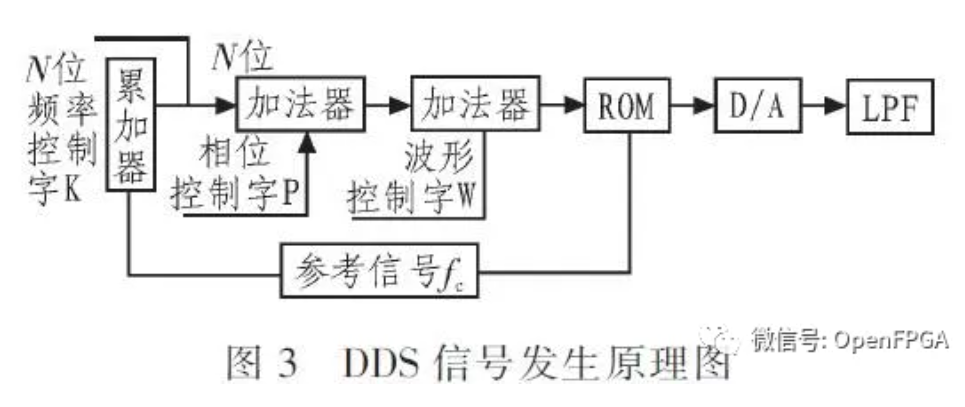

DDS的基本原理主要是从波形相位概念出发合成我们需要的波形,基本结构组成如下图所示,基本就是基准时钟、相位累加器、相位加法器、相位/幅度变换电路、DA转换、低通滤波器等组成,根据实现的功能不同,上诉结构会有所变化。

数字推到过程如下:

上面的数字推到过程可知,我们在采样频率一定的情况下,是可以通过控制N位频率控制字K,从而控制离散序列的频率,经后续电路(保持、滤波)处理后就可以唯一地恢复出此频率下的模拟信号。

FPGA实现DDS原理

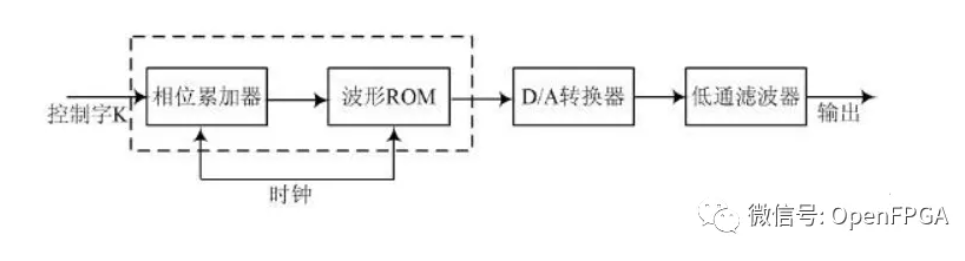

上节介绍的是DDS的基本原理,这节再简单介绍FPGA实现DDS的原理,两者基本原理不变,FPGA会有针对性的进行修改。

在例化RAM时初始化RAM内容的方式将固定(波形)数据存储到FPGA中,然后FPGA通过设计的相位累加器来计算并选择RAM中的数据(先控制地址),最后将数据给定的频率控制字输出给DAC,外围DAC转换后再经过低通滤波器后即实现了任意波形输出,上图是整个实现的原理框图,其中虚线框中是FPGA实现的,外围的DAC是一定要的。

小梅哥开发板

https://www.cnblogs.com/xiaomeige/p/6418761.html

DA芯片

TLC5620

介绍

https://www.cnblogs.com/xiaomeige/p/6418761.html

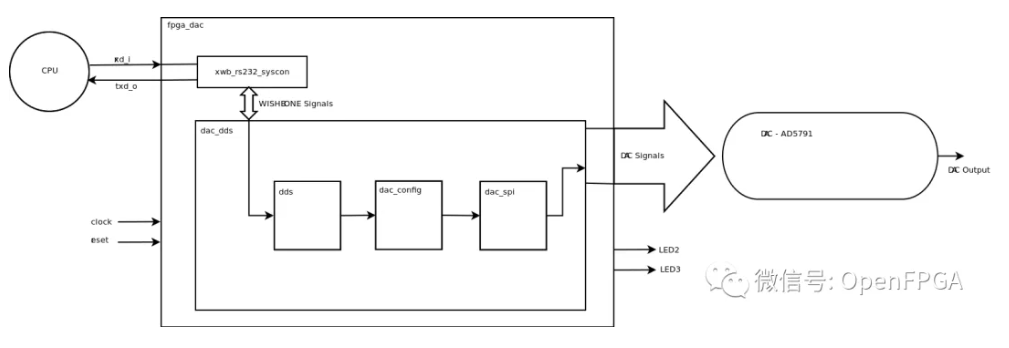

fpga_dac

https://github.com/julianofjm/fpga_dac

DA芯片

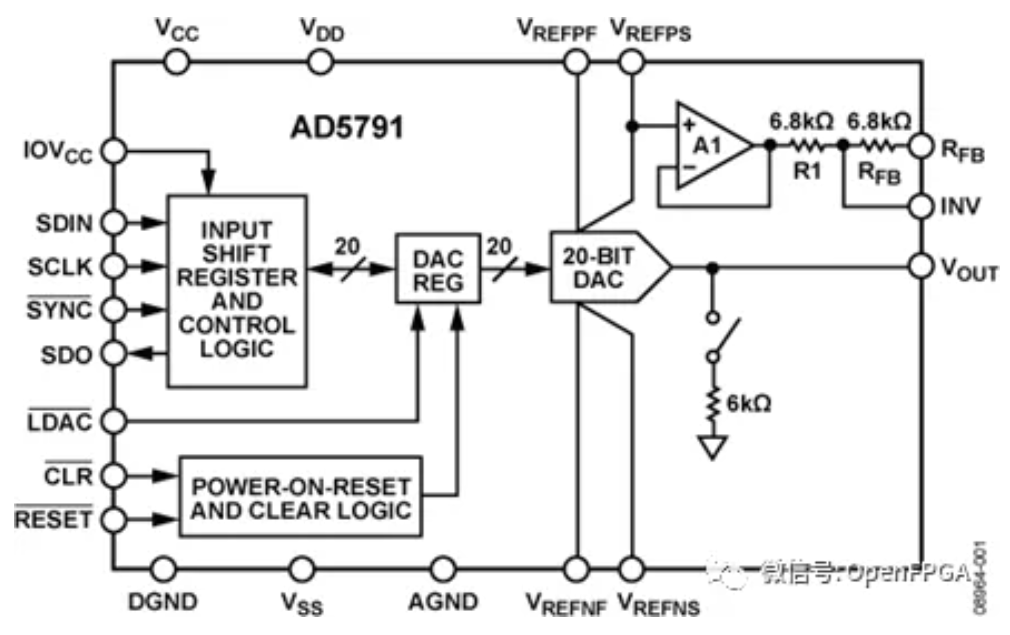

AD5791

数据手册

https://www.analog.com/cn/products/ad5791.html

开发环境

Xilinx FPGA+ISE

简介

使用 DDS 内核生成正弦波和 SPI 通信以控制 DAC 转换器(AD5791 Analog Devices)输出波形。通过上位机(cpp 应用程序)选择新数据的正弦频率和更新频率。

框图

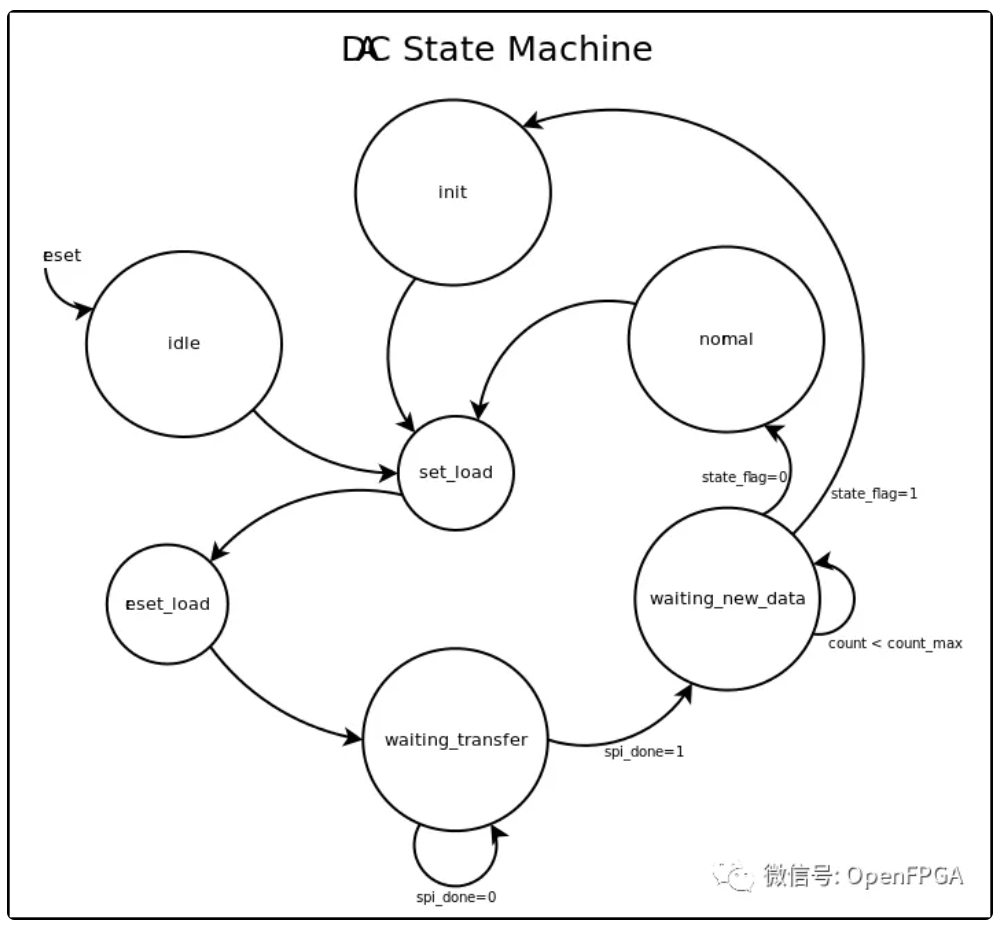

控制状态机

外部DDS芯片

https://github.com/TheWrangler/PSTR17R5B

DDS芯片

AD9914

数据手册

https://www.analog.com/cn/products/ad9914.html

开发环境

Xilinx FPGA+ISE

简介

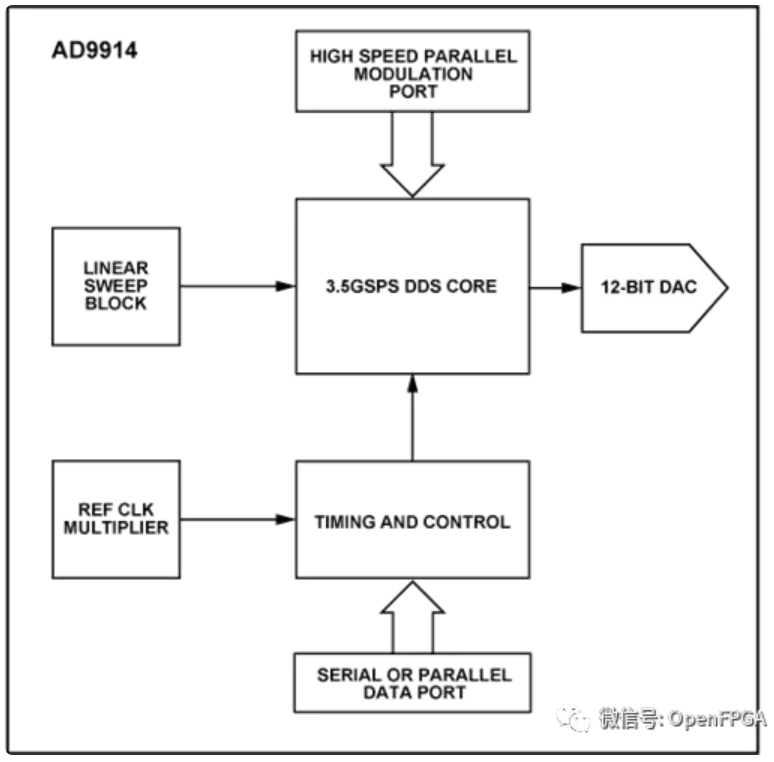

直接数字合成技术(DDS)采用相位查找表实现频率合成,广泛用于各类型信号发生器。AD9914是一款以DDS技术为基础的频率捷变芯片,可产生高达1.4GHz的频率信号。该芯片通过数字斜坡发生器(DRG)提供频率调谐功能,可产生线性扫频信号。同时,其数字斜坡发射器也可用于产生幅度和相位线性变化的信号。

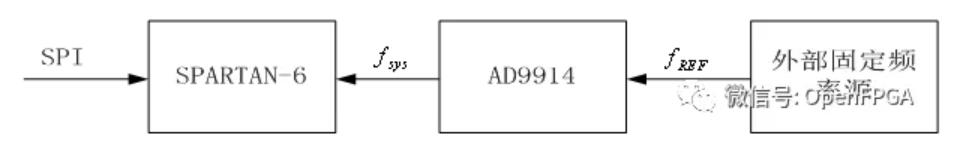

项目框图如下:

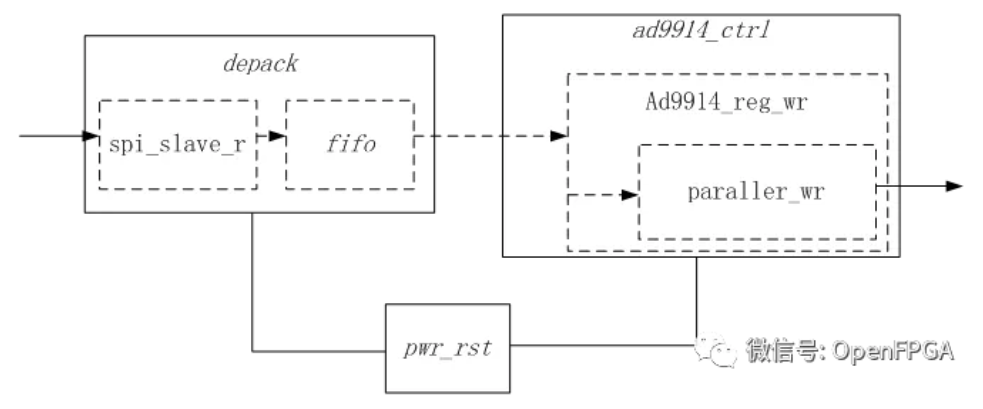

FPGA内部框图

FPGA-DDSsignalgenerator

https://github.com/JJ300119/FPGA-DDSsignalgenerator

DA芯片

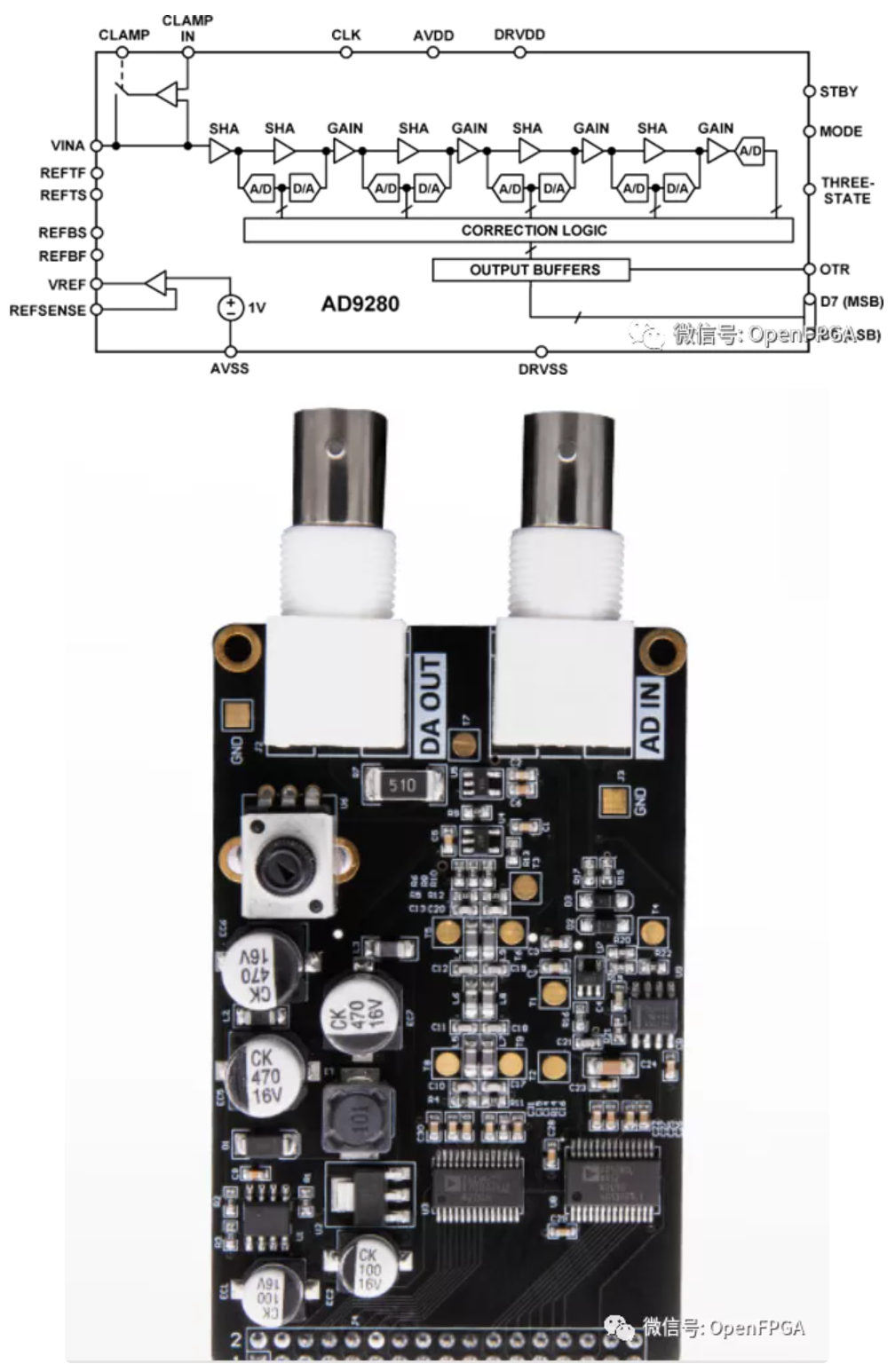

AD9280

数据手册

https://www.analog.com/en/products/ad9280.html

开发环境

Intel FPGA+Quartus II

简介

基于ALTERA FPGA + AD9280的DDS信号发生器,输出8位正弦波,频率大小可通过按键调节。

Arduino控制DDS信号生成

https://github.com/nicolacimmino/FunctionGenerator

简介

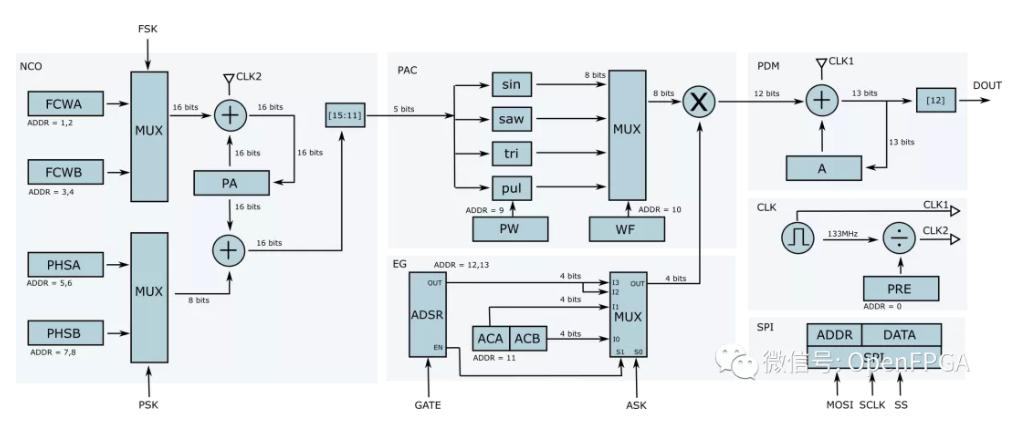

采用 Verilog 中内置的 DDS 的函数发生器,具有 FSK、PSK、ASK 功能和多种波形。

Signal_Generator_based_on_FPGA

https://github.com/yeby97/Signal_Generator_based_on_FPGA

简介

可以产生正弦/AM/FM/ASK/FSK信号,参数不可调(所以称其很简易)。

使用所平台的IP核产生,ROM初始化:Altera Quartus II使用mif文件;Xilinx ISE使用COE文件。相应文件使用MATLAB产生(提供源文件)。

verilog-DDS-generator

https://github.com/Zhiming-Huang/verilog-DDS-generator

简介

DE0-CV(Cyclone V)+ Quartus II 15.0

频率在 100khz-1Mhz 之间

产生正弦波、方波和三角波

总结

今天介绍了几个DDS项目,因为DDS和外围的DAC关系很大,所以这几个项目只能作为参考,主要就是看下控制方案,核心的部分一是外围DAC控制,而是波形文件的生成,这几个项目基本都提供了相关的波形生成的源文件(matlab或Python),对于很多人来说,整体难度比较低。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。