写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释(使用斜体表示),转自:

PCIe扫盲--复位机制介绍(FLR)-Felix-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台

转载正文

PCIe总线自V2.0加入了功能层复位(Function Level Reset,FLR)的功能。

该功能主要针对的是支持多个功能的PCIe设备(Multi-Fun PCIe Device),可以实现只对特定的Function复位,而其他的Function不受影响。

查询是否支持与产生 FLR

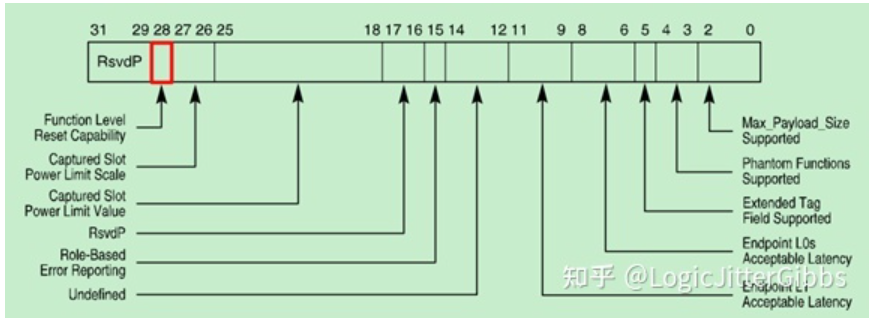

当然,该功能是可选的,并非强制的,软件可以通过查询配置空间中的设备功能寄存器(Device Capability Register)来查询该PCIe设备是否支持FLR。如下图所示:

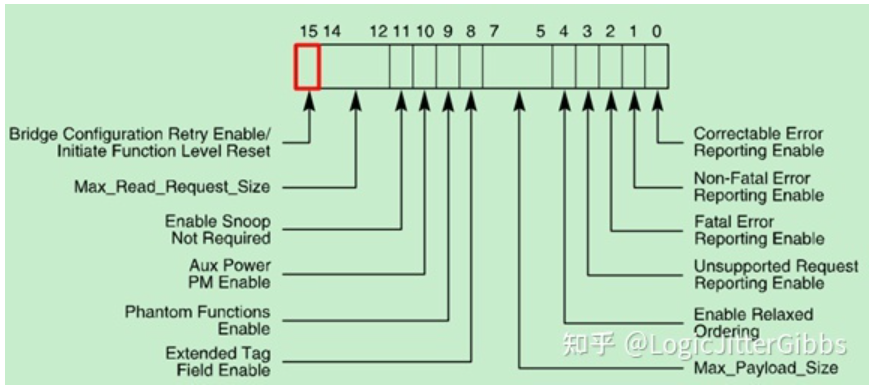

并可以通过设备控制寄存器(Device Control Register)中的将Initiate Function Level Reset bit置1,来产生FLR。

FLR只复位对应Function的内部状态和寄存器(使其暂时不变化,Making it quiescent),但是并不影响Sticky bits、有硬件初始化的值(Hardware-initialized bits)和链路专用寄存器(比如Captured Power,ASPM Control、Max Payload Size以及VC等寄存器)。

FLR 遵循的规则

如果该设备在FLR前,发出了Assert INTx中断消息,必须在开始FLR之前在发出对应的Deassert INTx消息,除非该INTx已经被与其他Function共享了。当收到FLR后,该Function的所有的其他功能都应被立即停止(Required to cease)。

此外,PCIe Spec还明确给出了FLR的完成时间应在100ms以内。

PCIe Spec还明确规定了,当某个Function处于FLR状态时的一些特性:

- 该Function不能有任何与外界通信的(外部)接口;

- 该Function必须将任何软件可读取的状态(可能包括加密信息等)打乱。换句话说,任何内部存储都必须被清零或者随机化;

- 该Function必须可以被另一个Diver配置为一般模式;

- 该Function必须为其收到的包含有FLR信息的配置写(Configuration Write)返回一个Completion,然后再进行FLR操作。

在进入FLR状态后,还需要:

- 该Function接收到的任何请求都应该被直接丢弃,且不登记(Logging),也不报错误。但是FC Credits必须要被更新,以维持链路的正常操作;

- 该Function接收到的任何Completion都应该被当做Unexpected Completions,然后直接丢弃,且不登记,也不报错。

版权声明

版权声明:本文为 AET 博主「Felix」的原创文章,转载请附上原文出处链接及本声明。

原文链接:PCIe扫盲--复位机制介绍(FLR)-Felix-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台

转载自:知乎

作者:Felix

推荐阅读

更多招聘及面经请关注FPGA的逻辑。