HDL设计是基础,设计完用一些工具检测自己的代码是很必要的,比如仿真工具去验证自己代码的功能。今天给大家介绍几种类型的工具,都是有助于HDL设计,其中包括:代码检查器(Lint)、代码覆盖率、波形设计、状态机设计等等,下面开始吧!

仿真

仿真是HDL建模基础,所有建模完成的硬件电路首先需要进行功能仿真,今天首先介绍一些仿真工具(除EDA工具自带的以外的仿真软件。)

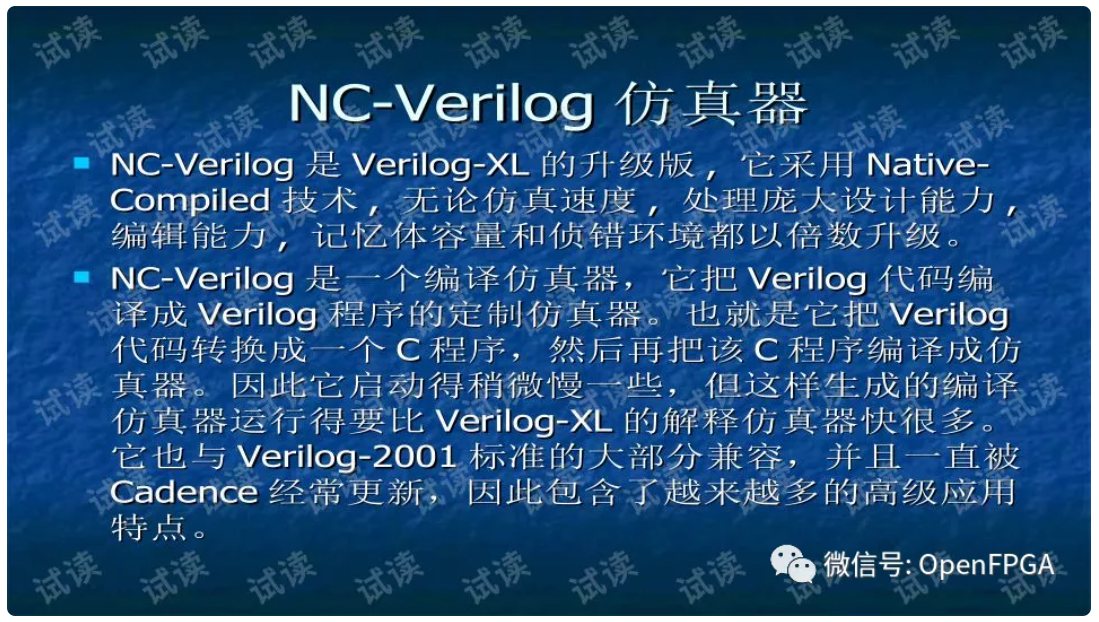

NCVerilog

http://www.cadence.com/

NC-Verilog 为 Cadence 公司之 Verilog 硬体描述语言模拟器 (simulator),可以帮助 IC设计者验证及模拟所设计 IC 的功能.使用 NC-Verilog软体,使用者必须使用 Verilog 硬体描述语言的语法来描述所要设计的电路.

这也是编译后的模拟器,其运行速度与 VCS 一样快,并且仍保持 Verilog-XL 的签核功能。当涉及到门级仿真时,这个仿真器很好用。

VCS

http://www.synopsys.com/

这是世界上最快的仿真器,这也是像 NCverilog 一样的编译仿真器。该仿真器在 RTL 仿真方面速度更快。支持 SystemVerilog。

MPSim

http://www.axiom-da.com/

Axiom 的 MPSim 是一个集成的验证环境,将业界最快的仿真器与先进的测试台自动化、基于断言的验证、调试和代码覆盖分析相结合。它带有内置的 Vera 支持。

Modelsim

http://www.model.com/

这是最流行的仿真器,它有非常好的调试器,支持 SystemC、Verilog、VHDL 和SystemVerilog。

其他

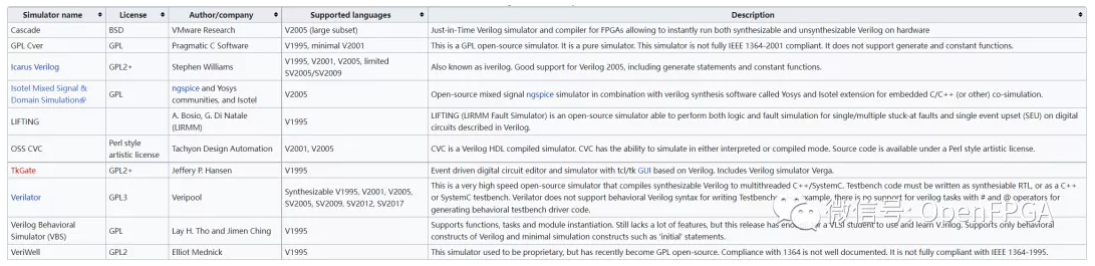

还有很多相对较好的仿真工具,但是国内的环境下,VCS和Modelsim 占了大多数,很难改变习惯,所以就简单介绍一些其他的见下面表格:

开源工具

开源用的相对较少了,而且是开源的,维护及持续性较差一些,也分为Verilog和VHDL版本去介绍

Verilog版本

这里只推荐Verilator(http://%20www.synapticad.com/)

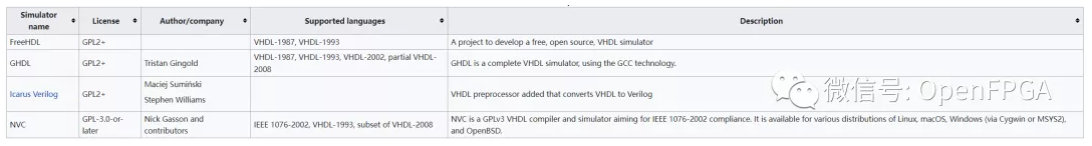

VHDL版本

这里只推荐GHDL

VCD 波形查看器

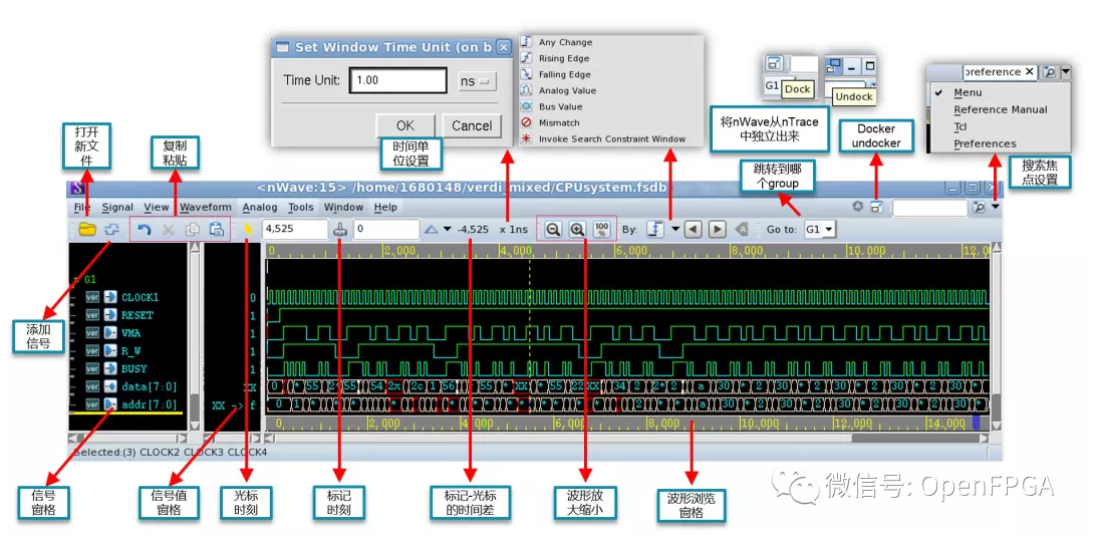

nWave :最好的 VCD 查看器之一,支持大型 VCD 转储。

http://www.springsoft.com/

Undertow:Undertow 波形查看器。

http://www.veritools-web.com/

GTKWave : 免费软件 VCD 查看器,似乎比其他免费 VCD 查看器好得多。

http://www.geocities.com/SiliconValley/Campus/3216/GTKWave/gtkwave-win32.html

Dinotrace : 来自 veritools 的免费 VCD 查看器

http://www.veripool.com/

代码覆盖率

Verification Navigator

http://www.transeda.com/

一个集成的设计验证环境,可通过一组强大的一流工具来管理 HDL 验证过程,从而实现一致、易于使用和高效的验证方法。这些工具包括 HDL 检查、覆盖分析、测试套件分析和 FSM 分析。该环境包括一个可扩展的流程管理器,用于轻松合并自定义验证流程。Verification Navigator 支持 Verilog、VHDL 和混合语言设计,并与所有领先的仿真环境无缝集成。

SureCov

http://www.verisity.com/

设计当今芯片和半导体 IP 内核的工程团队需要自信地了解功能测试套件对设计的执行程度。Verisity 的 SureCov 以任何可用工具中最低的仿真开销测量 FSM 和代码覆盖率,并且无需更改源设计。SureSight 图形用户界面准确地显示了设计的哪些部分已经被覆盖,哪些没有。

Code Coverage Tool

http://covered.sourceforge.net/

免费软件代码覆盖工具。Code Coverage Tool是一种 Verilog 代码覆盖率分析工具,可用于确定测试文件对被测设计的覆盖程度。

Lint 代码检查工具

Leda:

http://www.synopsys.com/

是一种代码检查工具,适用于使用 Verilog 和 VHDL 硬件描述语言 (HDL) 的设计人员。Leda 具有分析 HDL 代码预综合和预仿真的独特能力,并且与所有流行的综合和仿真工具和流程完全兼容。通过对语言语法、语义和有问题的综合/仿真结构进行 500 多项设计检查自动化,Leda 检测到常见以及微妙和难以发现的代码缺陷,从而让设计人员能够专注于设计。

HDLint

http://www.veritools.com/

用于 VHDL 和 Verilog 的功能强大的完整 linting 工具。

nLint

http://www.springsoft.com/

nLint 是一个全面的 HDL 设计规则检查器,与 Debussy 调试系统完全集成。

SureLint

http://www.verisity.com/

设计师需要工具来分析和调试他们的设计,然后再与项目的其余部分集成。SureLint 提供有限状态机 (FSM) 分析、竞争检测和许多附加检查,是市场上最完整的 lint 工具。

实用程序

FSMDesigner

http://mufasa.informatik.uni-mannheim.de/lsra/projects/fsmdes

FSMDesigner 是一个基于 Java 的有限状态机 (FSM) 编辑器,它允许硬件设计人员以简单舒适的方式指定复杂的控制电路。集成了硬件描述语言(HDL)生成器,使用 Simple-Moore FSM 模式,保证高效快速而复杂的控制流,提供一个图形化的设计界面。

TimeGen

http://www.xfusionsoftware.com/

TimeGen 是一种工程 CAD 工具,它使数字设计工程师能够快速有效地绘制数字时序图。波形可以很容易地导出到其他 Window 程序,例如 Microsoft Word,用于编写设计规范。与其他工具相比,TimeGen 的价格更低。

Waveformer

http://www.synapticad.com/

用于绘制波形的工具,用于文档目的。

Timing Tool

http://www.timingtool.com/

TimingTool 是一个免费使用的在线时序图编辑器。该工具提供了非常好的 VHDL 和 Verilog 测试平台,无需下载或安装。

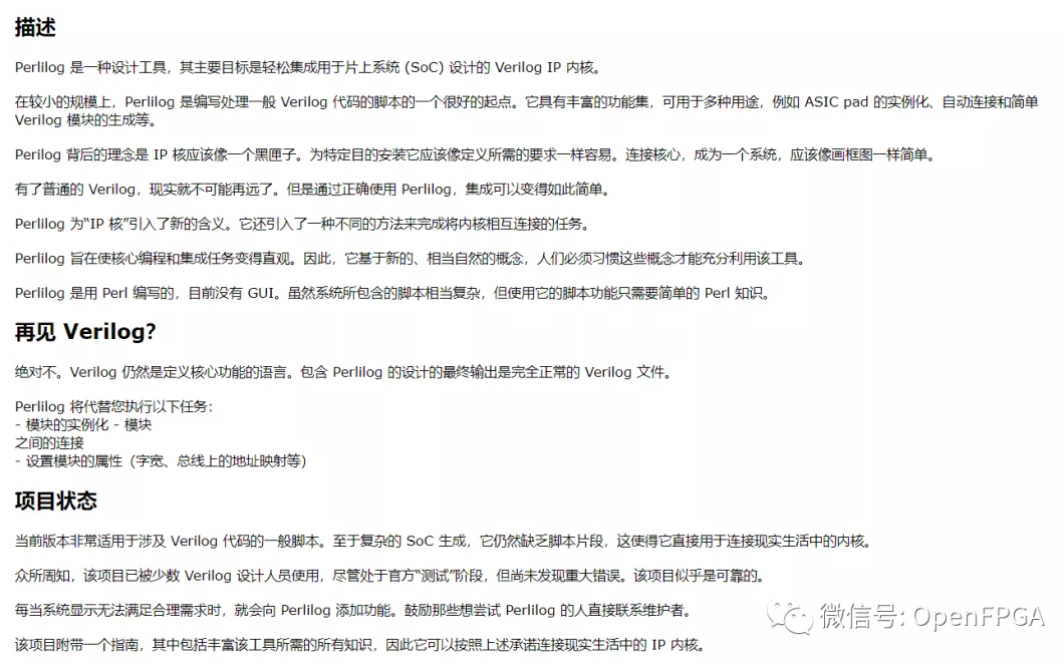

Perlilog

https://opencores.org/projects/perlilog

Perlilog 是一种设计工具,其主要目标是为片上系统 (SoC) 设计轻松集成 Verilog IP 内核。Perilog 背后的理念是 IP 核应该像一个黑匣子。为特定目的安装它应该像定义所需的要求一样容易。连接核心,成为一个系统,应该像画框图一样简单。Perlilog 是用 Perl 编写的,目前没有 GUI。虽然系统所包含的脚本相当复杂,但使用它的脚本功能只需要简单的 Perl 知识。

总结

推荐了一些小工具,都是方便大家在编写HDL时用于检测代码的缺陷、错误等,工具后续会持续更新,尤其是像Linting(Verilog/SV代码检查器-Lint 建模规则检查器与 Verilator)这种国内用的比较少的工具,其功能非常强大(后续介绍SystemVerilog时会介绍一些代码的隐藏转换,隐藏大小写转换等等,这些在设计时不会注意的地方-尤其针对初学者),主要是工具在检查代码时会给出错误的详细位置及原因,有些FPGA工具综合时不会给那么详细的错误指示,后续会出一些视频介绍这些工具,同时会增加这类工具的介绍,希望大家持续关注。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多IC设计技术干货请关注IC设计技术专栏