没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

在大多数实际应用中,移位寄存器用于对时钟的活动边缘执行移位或旋转操作。参考时钟信号正边缘的移位器时序如图5.27所示。如图所示时钟的每个正边缘,来自LSB的数据移位一位到下一级,因此,对于四位移位寄存器,需要四个时钟延迟才能从MSB获得有效的输出数据。

图5.27移位寄存器的时序

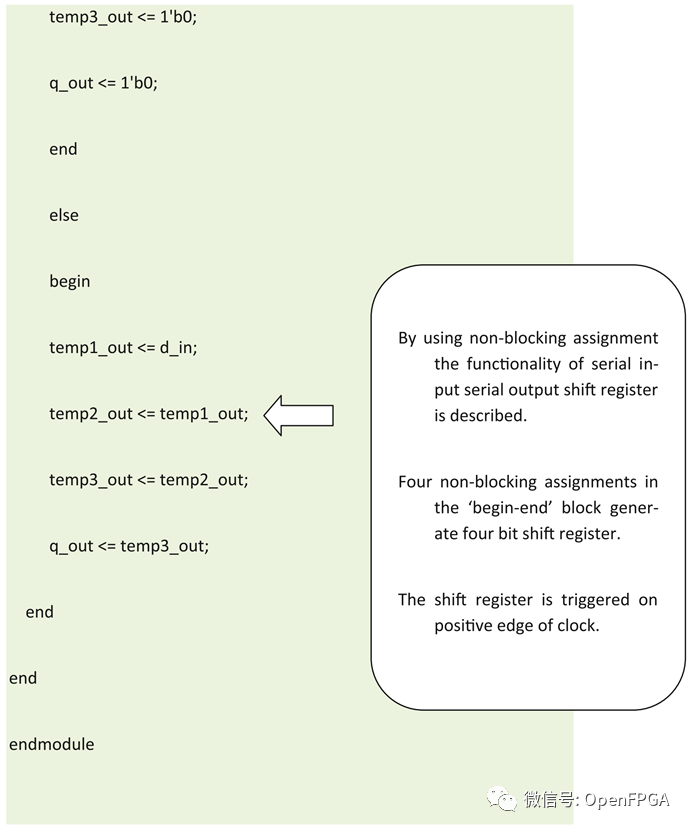

示例5.14中描述了串行输入串行输出移位寄存器的Verilog RTL。如示例中所述,数据“d_in”在每个时钟边缘上移位,以生成串行输出“q_out”。在正常操作期间,复位输入“reset_n”设置为逻辑“1”。为了为串行输入的任何更改生成有效的串行输出,移位寄存器需要四个时钟脉冲。

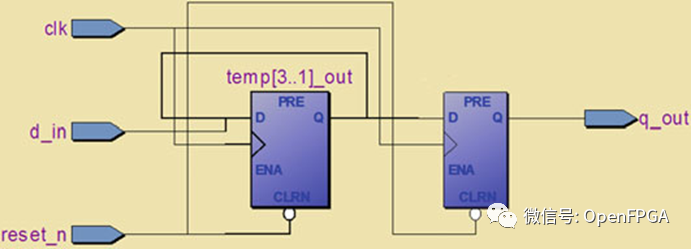

图5.28显示了用于串行输入串行输出移位寄存器的四个寄存器的综合逻辑。

示例5.14串行输入串行输出移位寄存器的Verilog RTL

图5.28四位移位寄存器的综合逻辑

右移或左移

大多数实际应用都涉及数据的右移或左移。考虑涉及字符串处理的协议,其中的要求是将字符串在右侧或左侧移动一位或多个位。在这种情况下,使用双向(右/左)移位寄存器。

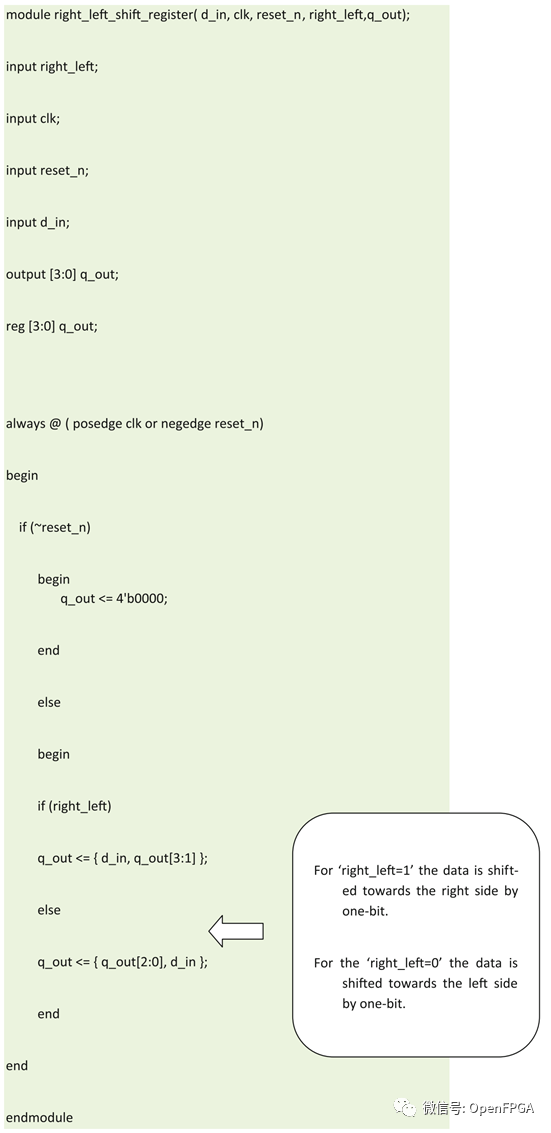

例5.15中描述了双向移位寄存器的Verilog RTL,数据的方向由“right_left”输入控制。对于“right_left=1”,数据向右移动;对于“right_left=0”,数据向左移动。

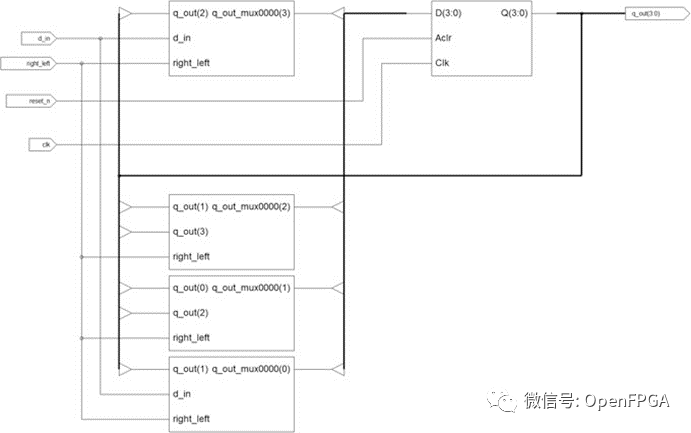

综合逻辑如图5.29所示,数据传输方向由“right_left”输入控制。综合逻辑由四个寄存器组成,附加组合逻辑控制数据流方向。

示例5.15右/左移位寄存器的Verilog RTL

图5.29双向移位寄存器的综合逻辑

并行输入和并行输出(PIPO)移位寄存器

在大多数处理器设计应用中,数据需要并行传输。考虑与外部外围设备通信的四位数据总线。如果处理器和外围设备都对并行数据进行操作,则必须使用并行输入并行输出逻辑传输数据。

在这种情况下,使用PIPO寄存器。PIPO四位寄存器的逻辑图如图5.30所示。四条并行输入线分别命名为PA、PB、PC和PD和四位并行输出线被命名为QA、QB、QC和QD。PIPO寄存器在时钟信号的正边缘触发。

例5.16中描述了Verilog RTL。

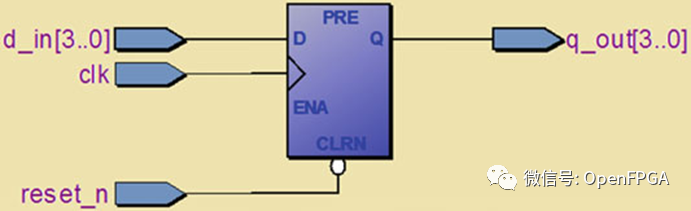

四位PIPO寄存器的综合逻辑如图5.31所示。

图5.30四位PIPO寄存器

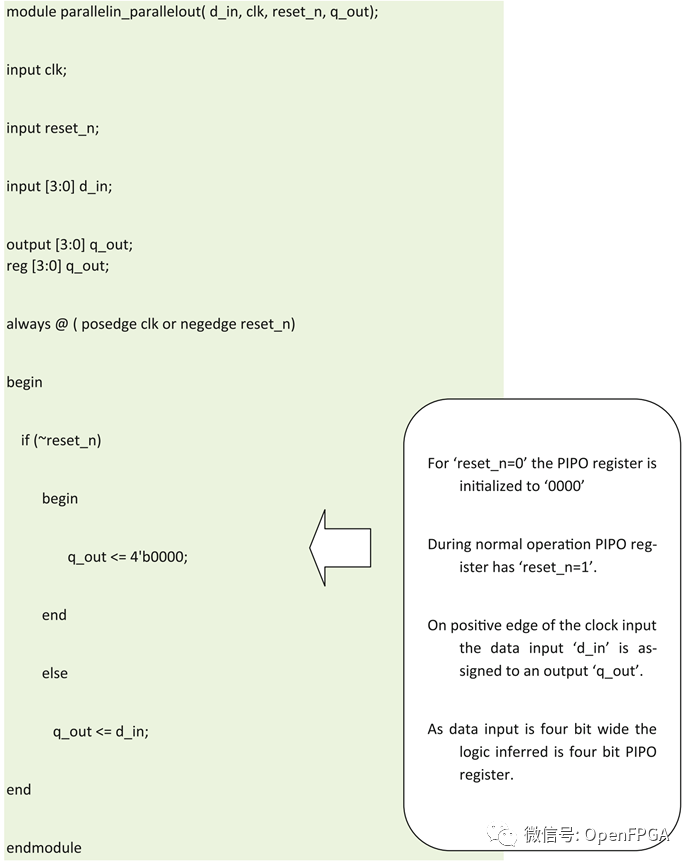

示例5.16 4位PIPO寄存器的Verilog RTL

图5.31 4位PIPO寄存器的综合逻辑

时序和性能评估

时序是ASIC/FPGA设计中非常重要的参数。时序电路的时序收敛对于复杂的ASIC/FPGA设计至关重要。RTL设计的详细时序分析和频率计算将在后续讨论。

为了更好地理解这一点,必须对寄存器输入和寄存器输出进行监督。在实际的ASIC/FPGA设计中,Verilog代码应该被有效地写入,并且应该具有寄存器输入和寄存器输出。这样做的原因是为了更好地进行时序分析,并获得干净的寄存器到寄存器路径。

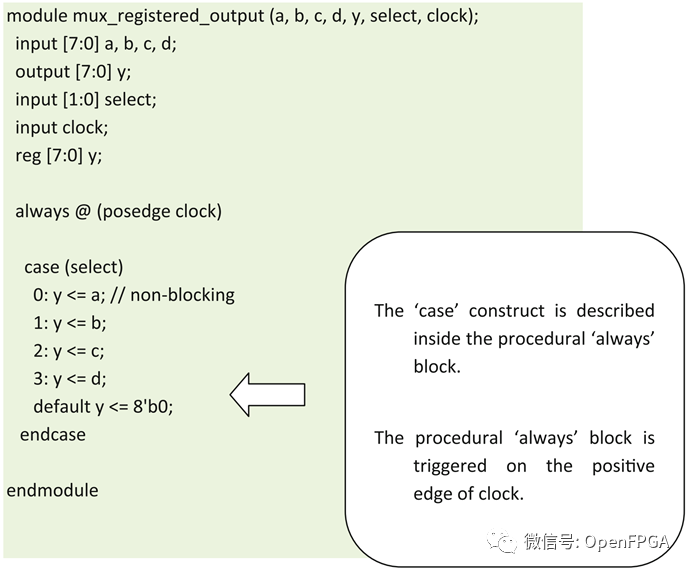

带有寄存器输出的Verilog RTL如例5.17所示。假设另一个模块驱动输入信号“a”、“b”、“c”、“d”和“select”。所有这些输入都是寄存器输入。这可以实现干净的寄存器路径和轻松的进行时序分析。

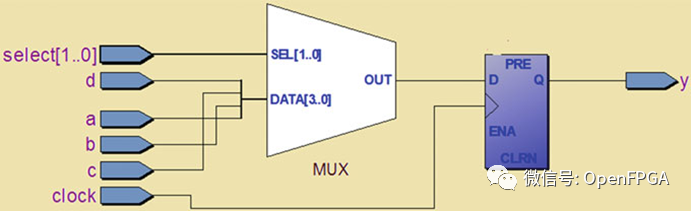

综合逻辑如图5.32所示,生成八位并行输入并行输出寄存器。该逻辑在时钟的正边缘触发。

示例5.17寄存器输出的Verilog RTL

图5.32寄存器输出逻辑的综合结果

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。