实验设计目标

- 编写程序,使用Anlogic 自带的ADC进行四通道数据轮询采集,同时介绍TD软件IP核的用法。

实验设计思路

本实验设计使用FPGA自带的12位串行AD芯片工作,将直流模拟信号转化为数字信号。

ADC分辨率为12bit,8个通道,采样率最大为1MSPS,如果4个通道工作,每通道最大采样率250KSPS。ADC 需要3.3V 模拟工作电压和模拟地以及一个独立的VREF 电压输入。8个模拟通道输入和用户IO 复用,用户实际可用通道数随芯片封装而异,当用户不需要ADC 时可以用作普通用户IO。采样时序如图3.1所示,每16个ADC时钟周期完成一次采样,输出一个EOC信号,ADC的驱动时钟最高16MHz,最高采样率1MSPS,EOC的时钟频率也即是最高1MSPS。

图3.1 Eagle ADC 采样控制时序

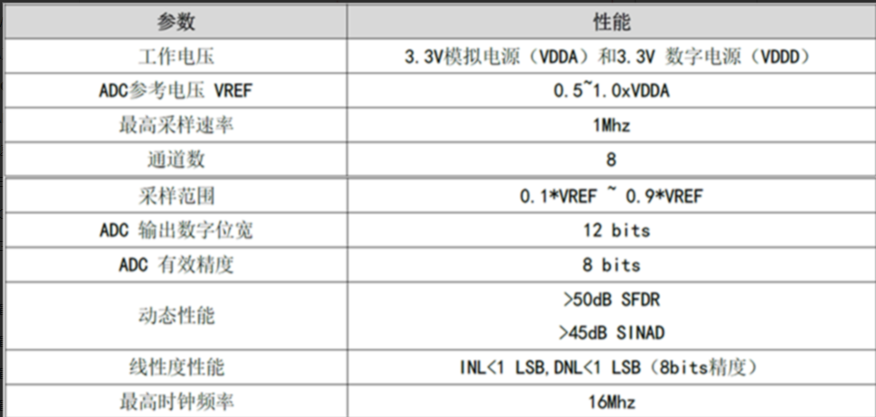

图3.2表示了Anlogic内部AD具体的性能指标。

图3.2 ADC内外部端口

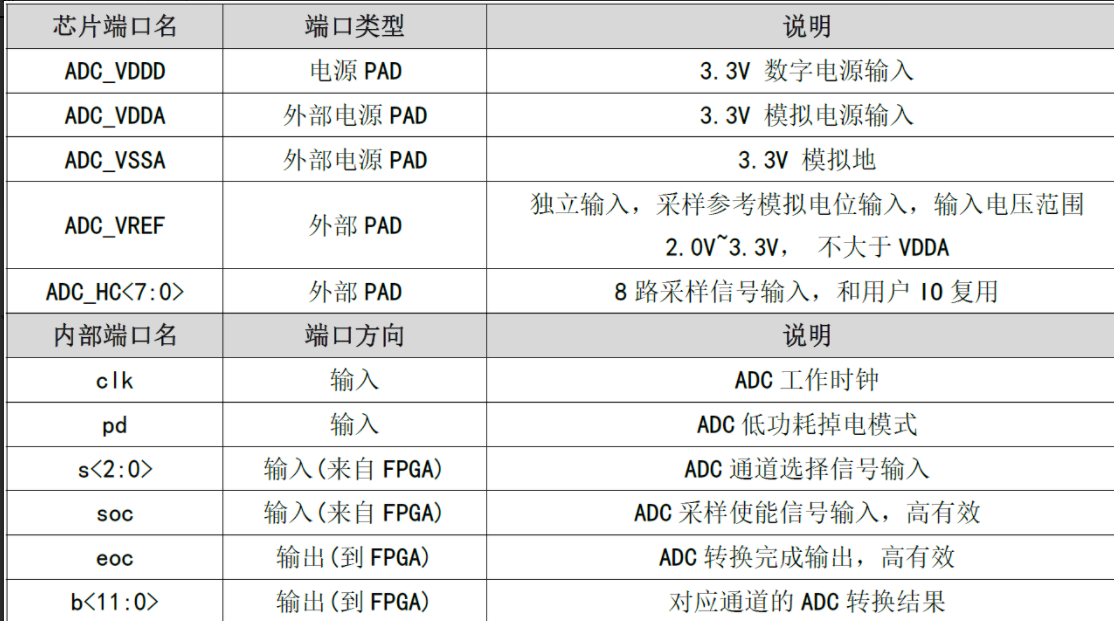

ADC内外部端口如图3.3所示。其中内部端口为IP模块的端口。

图3.3 ADC内外部端口

ADC 和PLL IP配置

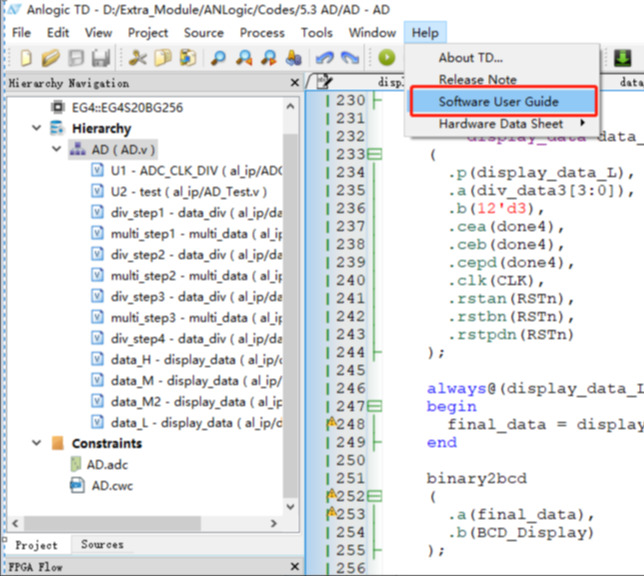

实验采用了TD软件自带的IP核,可以方便的进行ADC的配置。详细的说明可以参考TD User Guide。打开使用手册方法入图3.4所示。

图3.4 TD User Guide打开方法

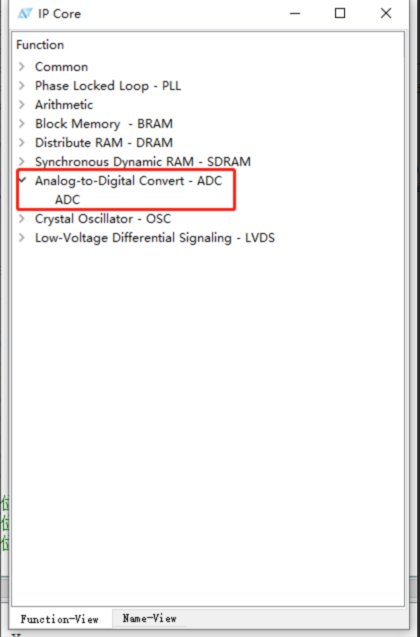

IP核的调用参考前面的介绍,本节介绍了AD核的具体实例化。

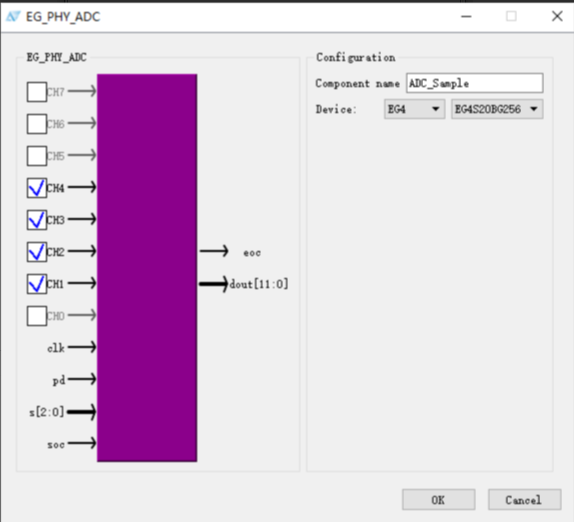

- 打开IP Generator里的AD模块,如图3.5所示。

图3.5选择内部AD采集的IP - 勾选需要进行采样的AD通道,然后在左上角输入模块的名称。EG4系列一共有8个通道,本次实验只采集通道CH1,2,3,4的数据,如图3.6所示。

图3.6 AD IP核参数配置 - 最后实例化这个IP。

图3.7 AD IP的例化

程序的解析后面我们会加以说明。

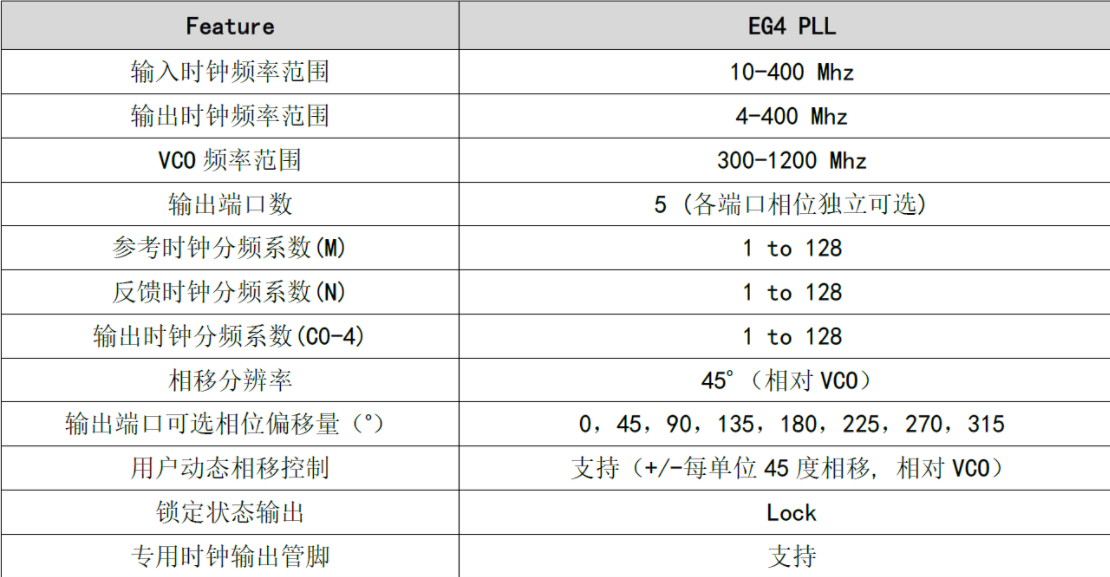

根据数据手册AD的最大输入时钟为16MHz,而实验板的时钟为50MHz,因此我们调用PLL模块,来产生16MHz的ADC时钟。EAGLE系列 FPGA最多内嵌有4个多功能锁相环(PLL0~PLL3),可实现高性能时钟管理功能。每个PLL都能实现时钟分频 /倍频、输入和反馈时钟对准、多相位时钟输出功能。

图3.8 EAGLE PLL 特性表

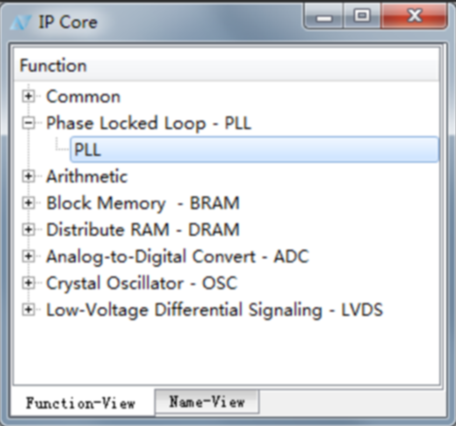

创建IP核PLL模块: - 打开IP Generator里的PLL模块,如图3.9所示。

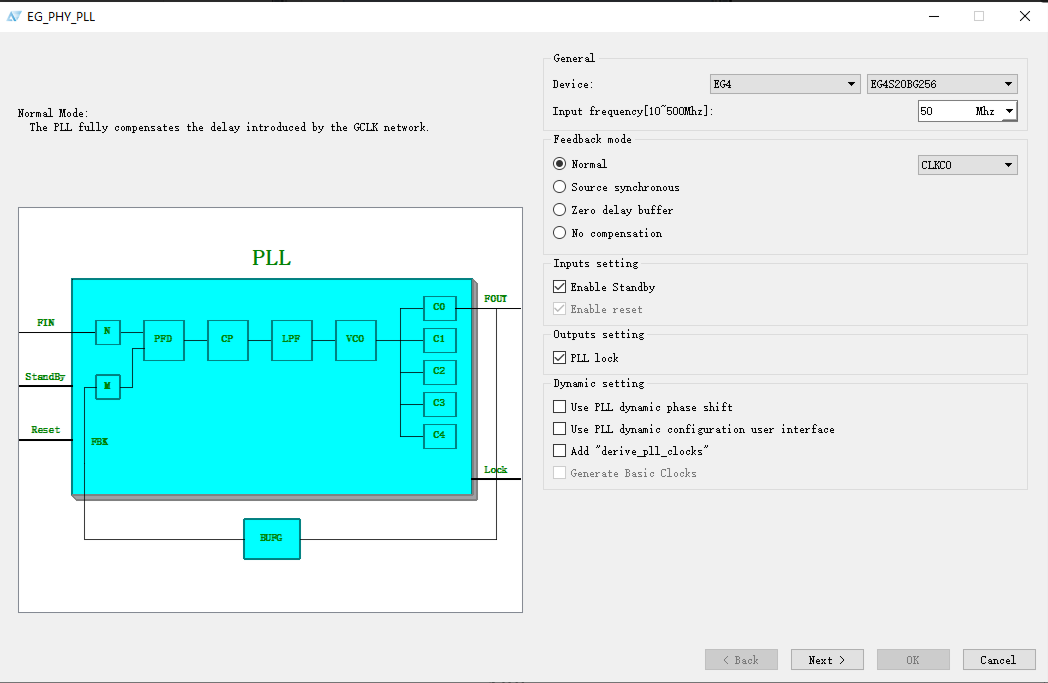

图3.9 创建PLL模块 - 在General设置界面,根据实验需求,选择输入时钟为50MHz,其他的设置保持默认。也可以根据自己的需要,选择反馈设置和动态设置。详细使用方法,可以参考TD_User_Guide文档。

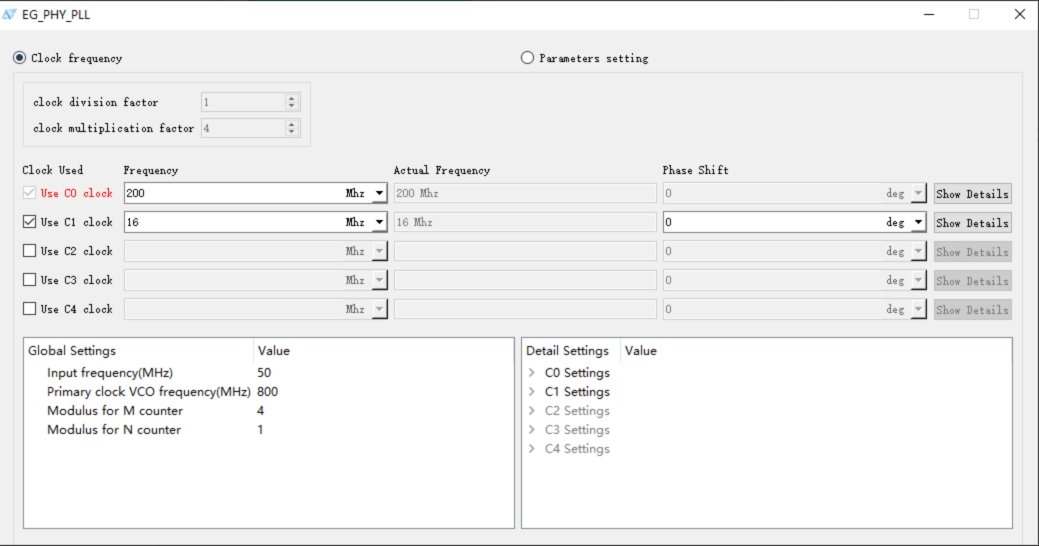

图3.10 PLL模块时钟输入配置 - 点击右下角的Next,进行时钟输出配置。本实验中我们使用C0产生200M时钟用于Chip Watcher采样时钟,使用C1产生16MHz的ADC时钟,其余设置保持默认。

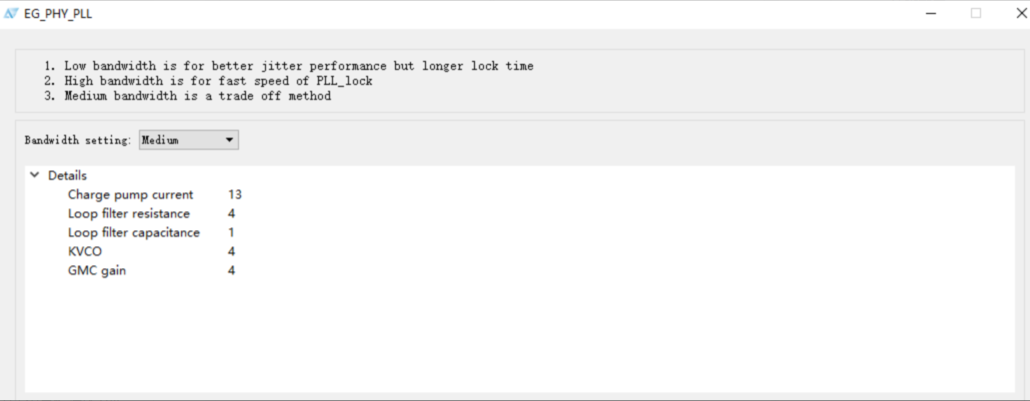

图3.11 PLL模块时钟输出配置 - 点击 Next, 选择输出时钟的带宽,本实验也选择默认Medium设置。如果用户需要更快的时钟锁定,需要把BandWidth选择为High,如果用户需要更小的时钟抖动,需要把Bandwidth设为Low。

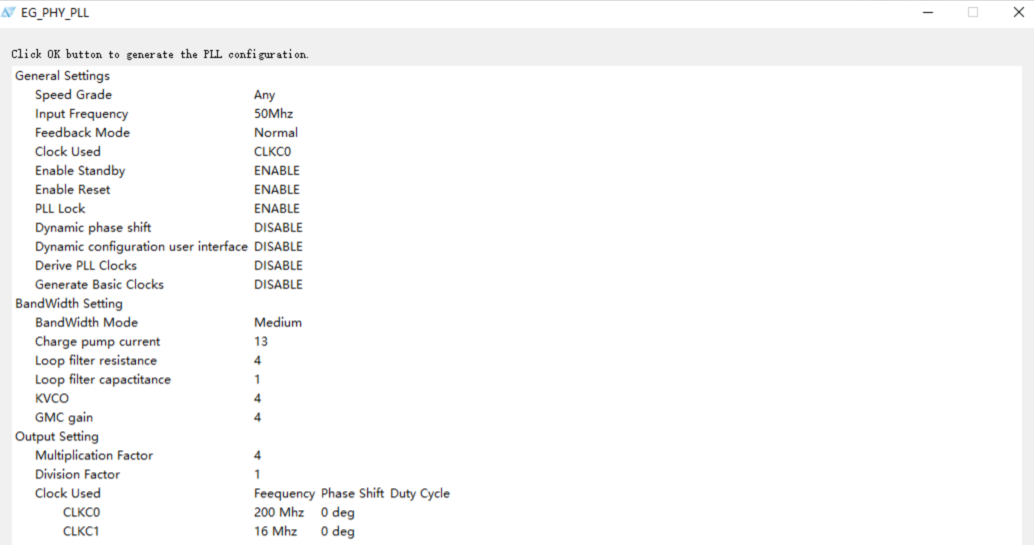

图3.12 PLL模块时钟输出带宽配置 - 点击Next,检查配置信息,完成PLL模块功能。

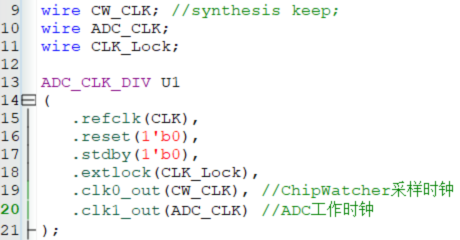

图3.12 PLL模块时钟输出带宽配置 最后实例化这个IP。Standby和reset功能暂时不启用,设置为1’b0。注意给CW_CLK加上 //synthesis keep;以免被编译器优化。

图3.12 实例化PLL模块程序设计

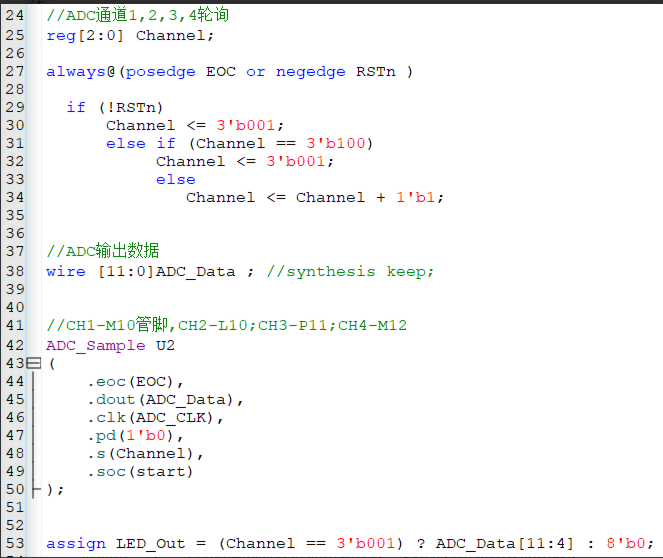

○ 24-34,使用EOC信号产生CH1-CH4的地址信号,3’b001 - 3’b100间循环。

○ 37-38,定义ADC的输出数据,注意我们整个程序里没有使用ADC_Data的低四位,这会导致编译的时候低四位被优化。我们这里使用//synthesis keep;语句来保证编译后该信号能够整体保留,以便我们在ChipWatcher里观察。

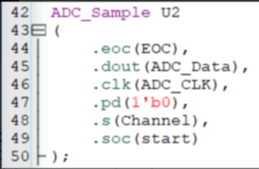

○ 41-50,调用ADC的例化。

○ 53,将ADC通道1采样后的数据的高八位放到LED上观察。FPGA管脚配置

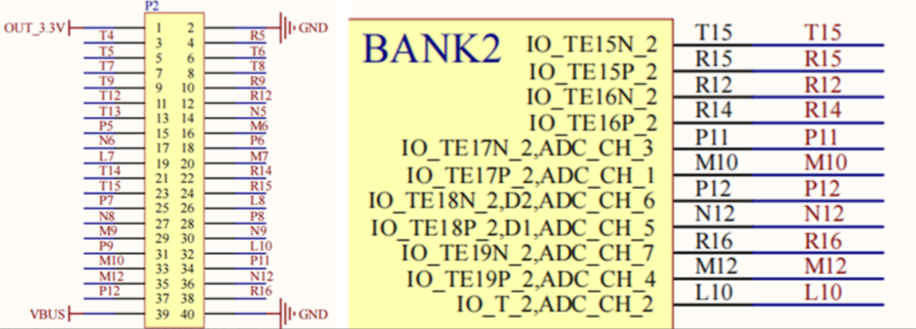

下面是Anlogic FPGA的IO Constraint,CLK是50MHz时钟输入,EOC信号我们把它送到插座上观察,LED0-LED7用来观察ADC CH1的直流采样结果(取高8位);RSTn、start输入信号分别与开发板上的SW0、SW1相连。ADC输入通道不需要在IO Constraint里配置,我们需要对照原理图查找插座上的输入位置。

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { RSTn } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { start } { LOCATION = A10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { EOC } { LOCATION = T4; IOSTANDARD = LVCMOS33; }

ADC 输入端口CH1-M10,CH2-L10,CH3-P11, CH4 - M12

实验结果

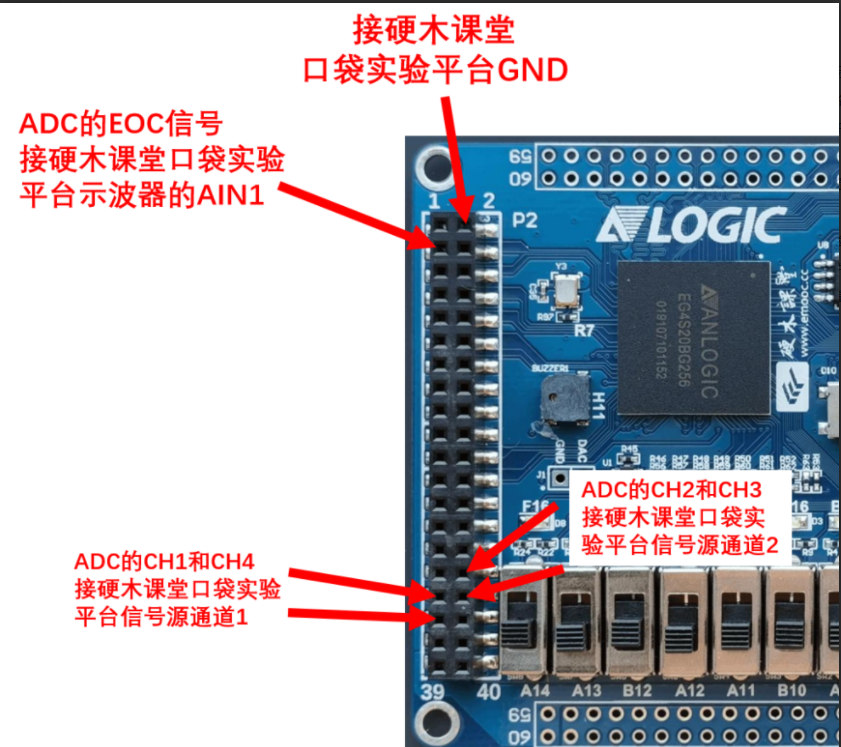

使用口袋仪器的“信号源”向ADC的CH1和CH4提供直流1V,向CH2和CH3提供直流2V,ADC的EOC信号接示波器通道1,并注意口袋仪器和开发板需共地。

图3.22 硬件连接示意图

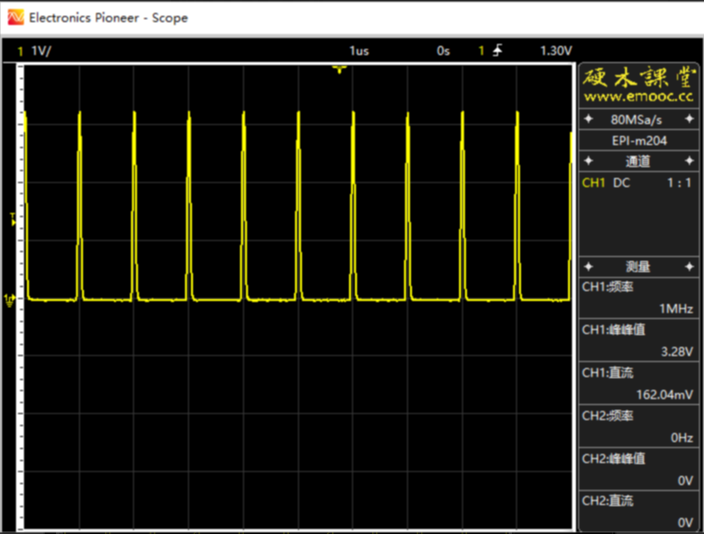

- 图3.23是使用口袋仪器EPI-m204产生的直流信号及参数说明。

图3.23 AD转换前的直流信号 - 图3.24是EOC信号,可以看到周期是1uS,频率1MHz

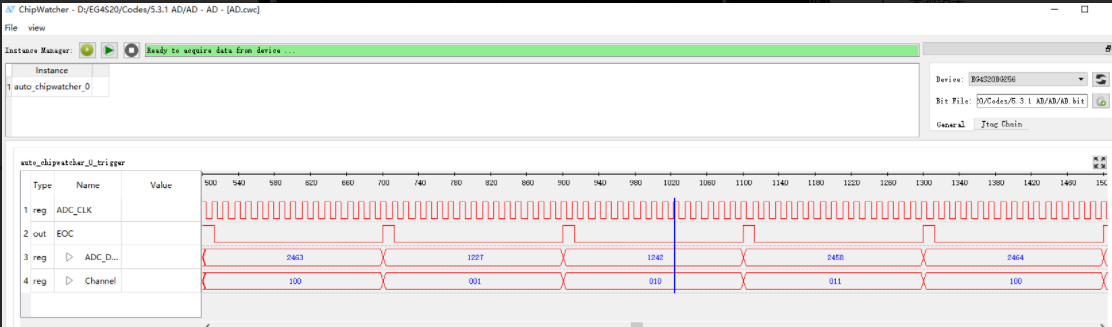

图3.24 实测EOC信号 - 图3.24是使用200MHz观察时钟的Chip Watcher得到的ADC_CLK (16MHz),EOC (1MHz),ADC_Data和Channel的时序图,可以看到ADC_Data比Channel信号滞后一个周期(3’b001对应的是CH4数据,3’b010对应的CH1,3’b011对应的CH2,3’b100对应的CH3),CH4和CH1采到的值分别为1227和1242,CH2和CH3采到的值分别为2458和2464。

图3.24 Chip Watcher工作图 - 通过 Vin = Vref Code/4096 = 3.3V Code/4096可以换算得到实际采到的电压值。

END

文章来源:https://www.yuque.com/yingmuketang/01/qeznn7

推荐内容

- 【安路 EG4S20 版本】基础板卡信息及使用教程:芯片和板卡简介

- 【安路 EG4S20 版本】基础板卡信息及使用教程:第一工程

- 【安路 EG4S20 版本】基础板卡信息及使用教程:使用ChipWatcher

- 【安路 EG4S20 版本】基础板卡信息及使用教程:使用Modelsim

- 【安路 EG4S20 版本】基础实验设计与实现:实验1 流水灯

- 【安路 EG4S20 版本】基础实验设计与实现:实验2 集成逻辑门及其基本应用

- 【安路 EG4S20 版本】基础实验设计与实现:实验3 译码器 编码器

- 【安路 EG4S20 版本】基础实验设计与实现:实验4 数据选择器

- 【安路 EG4S20 版本】基础实验设计与实现:实验5 触发器

- 【安路 EG4S20 版本】基础实验设计与实现:实验6 加法计数器

- 【安路 EG4S20 版本】基础实验设计与实现:实验7 抢答器

- 【安路 EG4S20 版本】基础实验设计与实现:实验8 功能数字钟

- 【安路 EG4S20 版本】基础实验设计与实现:实验9 矩阵键盘

- 【安路 EG4S20 版本】基础实验设计与实现:实验10 二进制转BCD码

- 【安路 EG4S20 版本】综合性实验设计与实现:实验11 PWM

- 【安路 EG4S20 版本】综合性实验设计与实现:实验12 DA及DDS

更多内容请关注走进FPGA专栏