模块简介

HDMI_VGA_Ethernet_SD_DAP模块是和DMZ_EG4S20 FPGA开发板配合使用的,为EG4S20大拇指核心板提供HDMI输出、VGA输出、千兆以太网通信、SD卡(与VGA复用IO)功能,模块上还集成了Arm CMSIS DAP调试器,用于调试编写到FPGA内部的Cortex-M0软核。

开发板功能和接口介绍

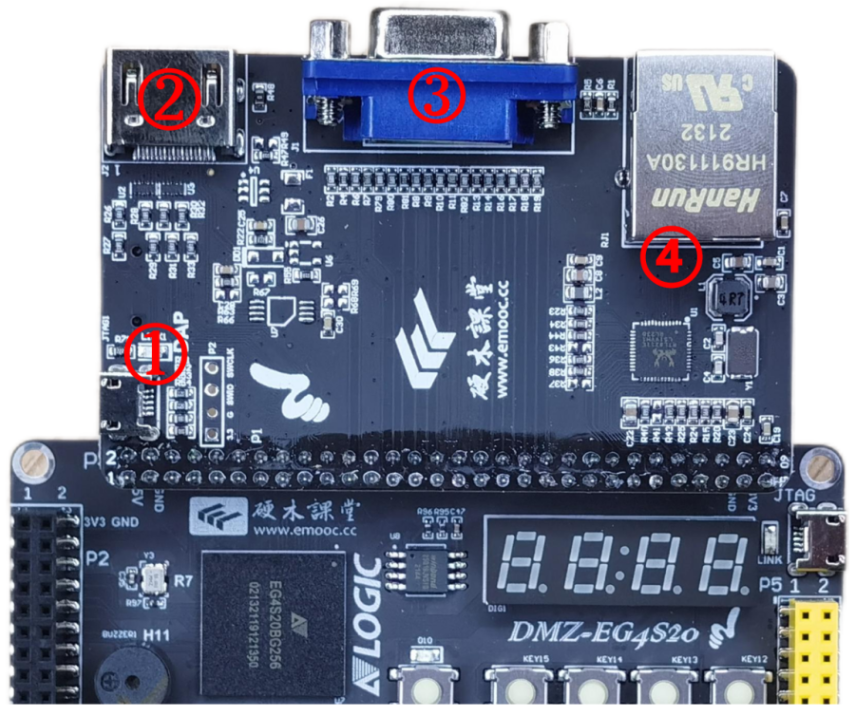

模块插在EG4S20上的正面视图

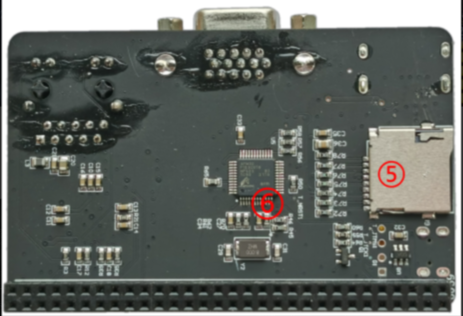

模块背面视图

功能模块说明

模块与FPGA的引脚连接

//Ethernet

set_pin_assignment { e_mdc } { LOCATION = F4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { e_mdio } { LOCATION = F3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_rxc } { LOCATION = K6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_rxctl } { LOCATION = L4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_rxd[0] } { LOCATION = L3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_rxd[1] } { LOCATION = J6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_rxd[2] } { LOCATION = K3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_rxd[3] } { LOCATION = K5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_txc } { LOCATION = H3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_txctl } { LOCATION = G3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_txd[0] } { LOCATION = H5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_txd[1] } { LOCATION = G6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_txd[2] } { LOCATION = H4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { rgmii_txd[3] } { LOCATION = G5; IOSTANDARD = LVCMOS33; }

//HDMI

set_pin_assignment { HDMI_CLK_P } { LOCATION = P4; IOSTANDARD = LVDS33; }

set_pin_assignment { HDMI_D0_P } { LOCATION = J3; IOSTANDARD = LVDS33; }

set_pin_assignment { HDMI_D1_P } { LOCATION = N1; IOSTANDARD = LVDS33; }

set_pin_assignment { HDMI_D2_P } { LOCATION = P1; IOSTANDARD = LVDS33; }

//VGA

set_pin_assignment { VGA_B[0] } { LOCATION = D1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_B[1] } { LOCATION = M5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_B[2] } { LOCATION = E1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_B[3] } { LOCATION = E2; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_B[4] } { LOCATION = F1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_G[0] } { LOCATION = F2; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_G[1] } { LOCATION = H2; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_G[2] } { LOCATION = G1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_G[3] } { LOCATION = J1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_G[4] } { LOCATION = H1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_G[5] } { LOCATION = K2; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_R[0] } { LOCATION = K1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_R[1] } { LOCATION = L5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_R[2] } { LOCATION = L1; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_R[3] } { LOCATION = M4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_R[4] } { LOCATION = N3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_VS } { LOCATION = M3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { VGA_HS } { LOCATION = M2; IOSTANDARD = LVCMOS33; }

//DAP调试器接口

set_pin_assignment { SWCLK } { LOCATION = R2; }

set_pin_assignment { SWDIO } { LOCATION = P2; }

例程功能

VGA_hdmi_tx_display

在HDMI和VGA口上同时输出纯色、彩条和黑白格等测试图像

rgmii_ethernet

移植自黑金科技的千兆以太网程序,请查看压缩包中的PDF实验文档

Cortex-M0

用于测试DAP调试器接口的M0程序:

- 使用MicroUSB线连接EG4S20调试器USB口和电脑,在TD文件夹中使用TD5.0.3版本打开工程下载bit文件到FPGA中,将SW0开关拨向上方(设定RSTn=1)。

- 用另一根Micro USB线连接HDMI模块上的DAP USB口和电脑。

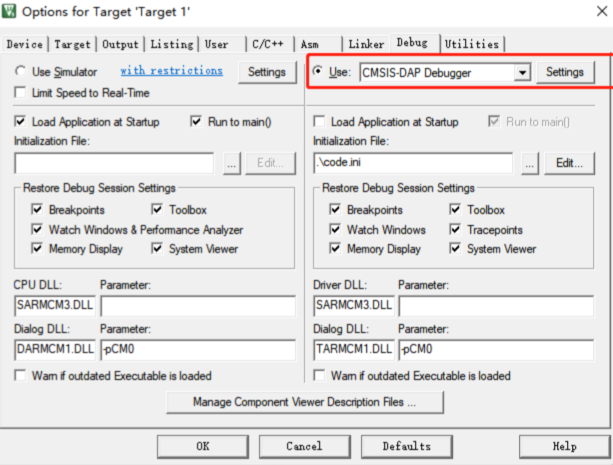

- 在Keil文件夹中打开exp1.uvprojx工程,点击Options for Target按钮。

在debug项目条中选择CMSIS-DAP Debugger:

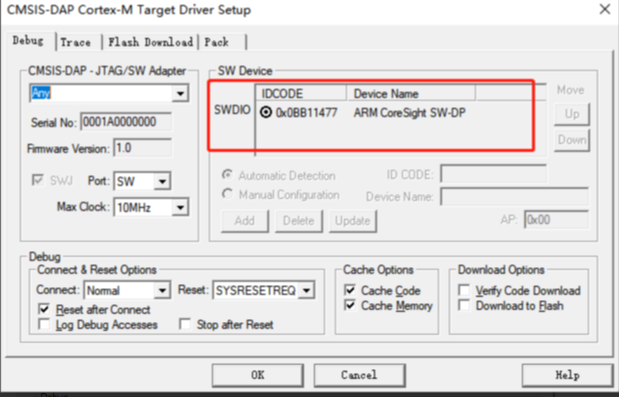

点击Setting,看到SWDIO中找到器件,说明成功

SDRAM_FIFO_503

用于测试EG4S20内部SDRAM,注意在5.0.3以上版本由于RAMFIFO的IP变动,程序无法编译通过。

程序下载后,SW0拨向上方,LED0常亮说明测试通过,LED0闪烁说明测试不通过。可以通过Chipwatcher观察读写结果。

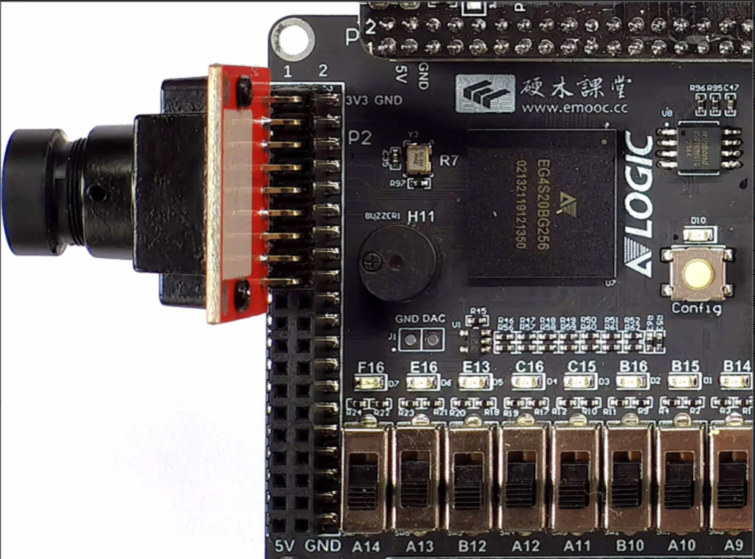

Cam_DVP_565

摄像头OV2640通过FPGA的BRAM后从VGA口发出的例程。OV2640的插接位置如下:

OV2640的引脚分配如下:

set_pin_assignment {cam_data[0]} { LOCATION = T8; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[1]} { LOCATION = T9; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[2]} { LOCATION = R9; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[3]} { LOCATION = T12; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[4]} { LOCATION = R12; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[5]} { LOCATION = T13; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[6]} { LOCATION = N5; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_data[7]} { LOCATION = P5; IOSTANDARD = LVCMOS33; }

set_pin_assignment {cam_href} { LOCATION = T5; }

set_pin_assignment {cam_pclk} { LOCATION = M6; }

set_pin_assignment {cam_pwdn} { LOCATION = P6; }

set_pin_assignment {cam_rst} { LOCATION = T7; }

set_pin_assignment {cam_soic} { LOCATION = R5; PULLTYPE = PULLUP; }

set_pin_assignment {cam_soid} { LOCATION = T6; }

set_pin_assignment {cam_vsync} { LOCATION = T4; }

set_pin_assignment {cam_xclk} { LOCATION = T14; }

ov2640_sdram _vga

摄像头OV2640通过EG4S20内部的SDRAM后从VGA口发出的例程。

END

文章来源:https://www.yuque.com/yingmuketang/01/lko336#Irndt

推荐内容

- 【安路 EG4S20 版本】基础板卡信息及使用教程:芯片和板卡简介

- 【安路 EG4S20 版本】基础板卡信息及使用教程:第一工程

- 【安路 EG4S20 版本】基础板卡信息及使用教程:使用ChipWatcher

- 【安路 EG4S20 版本】基础板卡信息及使用教程:使用Modelsim

- 【安路 EG4S20 版本】基础实验设计与实现:实验1 流水灯

- 【安路 EG4S20 版本】基础实验设计与实现:实验2 集成逻辑门及其基本应用

- 【安路 EG4S20 版本】基础实验设计与实现:实验3 译码器 编码器

- 【安路 EG4S20 版本】基础实验设计与实现:实验4 数据选择器

- 【安路 EG4S20 版本】基础实验设计与实现:实验5 触发器

- 【安路 EG4S20 版本】基础实验设计与实现:实验6 加法计数器

- 【安路 EG4S20 版本】基础实验设计与实现:实验7 抢答器

- 【安路 EG4S20 版本】基础实验设计与实现:实验8 功能数字钟

- 【安路 EG4S20 版本】基础实验设计与实现:实验9 矩阵键盘

- 【安路 EG4S20 版本】基础实验设计与实现:实验10 二进制转BCD码

- 【安路 EG4S20 版本】综合性实验设计与实现:实验11 PWM

- 【安路 EG4S20 版本】综合性实验设计与实现:实验12 DA及DDS

- 【安路 EG4S20 版本】综合性实验设计与实现:实验13 FPGA内部AD多通道采样实验

- 【安路 EG4S20 版本】综合性实验设计与实现:实验14 UART串行通信

- 【安路 EG4S20 版本】综合性实验设计与实现:实验15 高速ADC和DAC实验

更多内容请关注走进FPGA专栏