刚毕业那会研究了一段时间的3D-Torus,近期又看了CHI和CMN相关的内容,感觉互联架构挺有意思的。我想尝试做一个支持AXI协议的互联架构,使用SpinalHDL实现。主要目的有两个,一是了解互联,二是SpinalHDL练手,后者更为强烈,该项目可能并无实际价值。

01 CHI的片上互联总线

片上互联是将SoC内部不同模块连接起来的结构,如前文提到过的硬件系统结构中, Interconnect Bus就是片上互联。需要支持模块之间的高速数据传输,高效地互联互通。互联只是结构,可以使用不同的总线协议,如APB、AXI或CHI,不同协议的互联结构会有所不同。

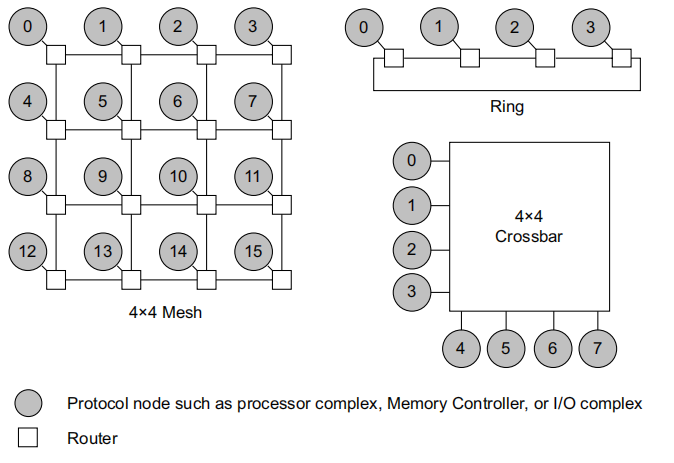

近期看了一些CHI协议内容,其中举了几个互联拓扑的例子,如下图所示。CHI协议基于FLIT传输的方式,FLIT的顺序由接收方进行恢复,使用Credit的握手方式。这些特征可以使得互联结构做得非常灵活,如下图的Mesh、Ring和Crossbar,根据流量做自适应调整、拥塞处理等等,其路由算法也比较复杂,存在dead-lock和live-lock的风险。

02 AXI协议的互联

AXI协议之间定义了5种类型的通道,通道之间存在依赖关系,同一通道也都存在顺序关系,如数据通道相同ID的数据、请求通道相同ID按顺序完成。这一特征使得AXI互联总线只能使用Crossbar或其级联的结构,也就是分发和汇聚的模式。由于不同通道之间存在依赖关系,存在相互阻塞的问题,影响性能。

03 openMeshNetwork

基于AXI协议,做一些裁剪,实现一种Mesh Network的互联结构,可以类似于CHI协议支持多种互联结构,进而实现高效地互联互通。称之为open Mesh Network,缩写为openMN。

首先,是对AXI协议做一些简化处理。

- 仅支持2^n Byte的输出传输,最大支持512Byte

- 仅支持INCR的传输Burst

- 支持数据位宽为32/64/128/256/512/1024bit

- 乱序执行,不支持请求操作的保序处理

其次,参考CHI协议定义,并使用同一通道传输请求、数据和响应,互联结构使用FLIT进行支持完全乱序的传输方式。

另外,还需要将AXI接口与上述定义的FLIT接口进行相互转换,对乱序返回的数据和响应进行重排序。

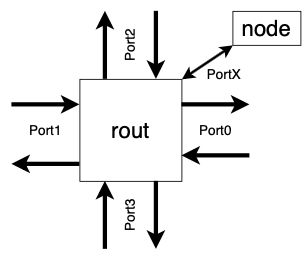

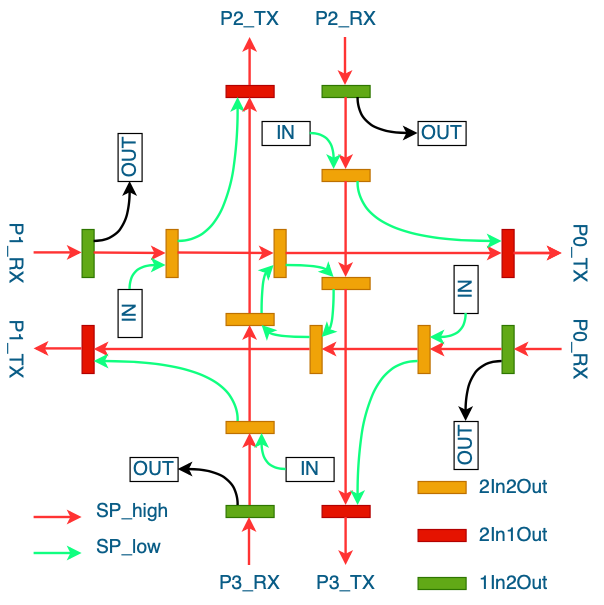

这一修改之后,可以将互联结构实现得非常灵活,其中的关键点是CHI协议内例子的Rout实现,如下图所示,决定了互联的效率。每个Rout最大支持4个互联Port和1个节点Port,每个Port均有发送和接收两个方向的通路。

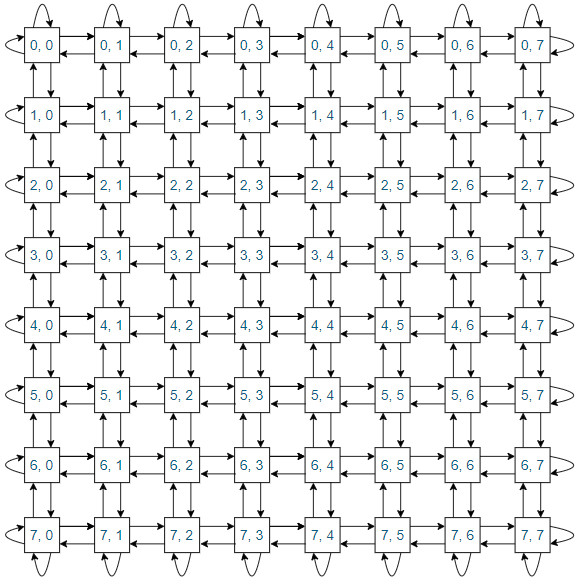

完成Rout设计之后,可以支持64个节点的Mesh Network,如下图所示,还可以根据需求进行扩展或简化。在互联拓扑内,每个节点均分配一个特定的坐标信息,路由算法基于该坐标进行处理,扩展该坐标信号位宽可支持更大的互联网络。

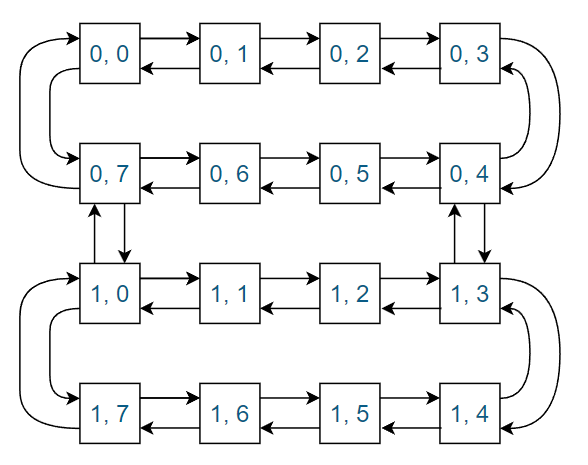

或者如下,将两个Ring结构通过两个方向共4条通路进行互联。

04 路由节点rout设计

rout的每个输入需要发送至node或其余3个方向,每个输出的来源可能是其余3个方向的输入或node。经过几次迭代,考虑做成如下的形式。

这一微架构有如下的特征和优势。

- 使用完全无阻塞传输,无需握手

- 使用2输入和2输出的调度单元,优先调度直通路的FLIT

- 调度分离,后端易于实现,达到较高的频率

- 最大支持4个节点输出和4个节点输入

但是,当前没有考虑dead-lock和live-lock问题,不支持基于qos的调度逻辑,还有较多细节暂未考虑。

05 代码设计

计划使用SpinalHDL实现,主要目的还是学习这一语言。不可否认当前的Verilog在PPA实现非常高效,但实在是太臃肿了。这里主要还是想尝试探索高级语言的灵活性,高效实现。

具体代码包含如下几部分。

- 接口信号定义

- 路由节点rout设计,包括调度单元和路由算法

- 请求节点node设计,实现FLIT与AXI协议的相互转换,分为Master和Slave

- 互联拓扑结构的生成函数

以上是当前考虑的方案设计,已经过几次迭代,前几次的微架构就没有再贴上来了,有兴趣的话可以再交流。后续完成的SpinalHDL代码计划共享,也是互相学习的过程。

- End -

作者:芯工阿文

原文链接:芯工阿文

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。