1. PCIE总线概述

1.1 PCIE总线的发展历史

PCIE总线技术,也叫计算机内部总线技术”Peripheral Component Interconnect”,即外围组件互联,其前身是PCI总线,但PCI总线真正应用是随着Intel的Pentium处理器诞生而开始的,在1994年的时候,以绝对的优势,战胜了VESA总线,成为了当时的标准,从此,几乎所有的外围设备,从硬盘控制器到声卡,网卡,都用PCI插槽。

在过去的十几年中,PCI总线得到了广泛的应用,虽然PCI总线,在往后的10几年当中也有所发展,先后出现了64位的PCI-/66MHz、PCI-X,但是随着微处理器、存储器和互联网络的发展,并行数据传输的PCI总线技术逐渐成为系统整体性能提升的瓶颈,首先是高性能的图像处理芯片从PCI总线分离出来,形成单独一种总线技术,那就是AGP总线,随着千兆以太网和其他高带宽设备在消费级系统上的出现,PCI133MB/s的带宽明显不能满足这些应用的需求。而串行点对点的PCI Express总线的提出彻底改变了原来PCI总线的并行技术,克服了PCI总线在系统带宽、传输速度等方面的固有缺陷。

1.2 PCIE总线的特点:

a) 在数据传输的模式上,采用LVDS串行传输方式,一条PCIE通道由2对LVDS差分信号线来实现发送和接收。(添加PCIE收发结构图)

b) PCIE采用点对点的串行连接,和PCI等其他总线的共享并行架构相比,能够为系统内的所有设备分配独立的通道资源,充分保障设备的带宽,提高数据传输率。

c) 具有很好的灵活性,一个PCIe物理连接可以根据实际需要配置成x1,x2,x4,x8,x16和x32链路模式(lanes)(添加传输速率对比的表)

1.3 PCIE总线的系统架构

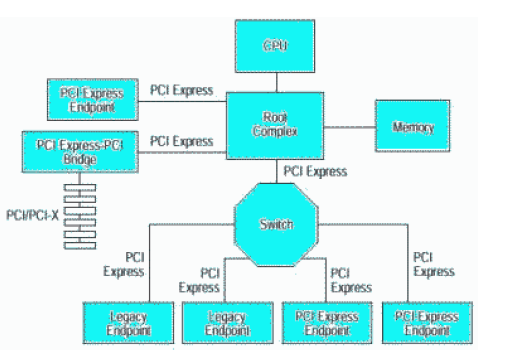

PCIe的基本结构包括根组件(Root Complex),交换器(Switch)和各种终端设备(Endpoint)。根组件可以继承在北桥芯片中,用于处理器和内存子系统与I/O设备之间的连接,而交换器的功能通常是以软件形式提供,它包括两个或者更多的逻辑PCI到PCI的连接桥(PCI-PCI Bridge),以保持与现有的PCI兼容。下图列出了PCIe 1.0的拓扑结构图。

2. 目前PCIE开发的常用方法

A. 利用专用的PCIe协议接口芯片设计。

专用PCIe协议接口芯片主要功能是实现了PCIe物理层、数据链路层和事物层的逻辑控制。常见的桥接芯片有PEX8311,、PEX8111等。虽然这种方式的开发难度不算太大,但是它并不能够有效发挥出PCIe高带宽的优势(桥接芯片提供的通道数有限),也缺乏可配置性核灵活性,难以提高系统性能。

B. 使用可编程逻辑器件的方式来实现。

使用可编程逻辑来实现PCIe也有三种方法。1、采用第三方PHY接口器件和非集成GTP接口的FPGA芯片实现,PCIe的物理层协议由PHY接口芯片负责,而事物层以及逻辑设计在FPGA芯片实现,PHY器件和FPGA之间有个PIPE(PCIe的物理接口);2、基于软核的思想,利用FPGA内部的软核,实现PCIe的协议,FPGA执行并实现PCIe协议中的物理层、事物层,但是部分协议需要用户自己编写;并且利用软核的话,会耗费FPGA内部的逻辑资源。3、基于硬核的设计思想,FPGA里面提供的硬核就相当于完整地实现PCIe中的物理层和数据链路层的协议,只需用户自行设计事物层数据传输内容以及配置空间信息,可以大大缩短开发周期。

3. PCIE协议概述

和TCP/IP 协议一样,PCIe数据传输也有它自己的协议,PCIe设备根据协议功能也有分层,下面将分别加以介绍。

3.1 PCIe的事务类型

PCIE运用数据包实现设备之间的数据传输。根联合体可以与各种端点进行通信。一个端点也可以与另一个端点通信。通信就是处理层数据包传输。

PCIe事务可以分为四大类:

a) 存储器事务

b) IO事务

c) 配置事务

d) 消息事务

其中事务是指请求者和完成者之间完成一次消息传送需要完成的一系列一个或者多个数据包的传送过程。

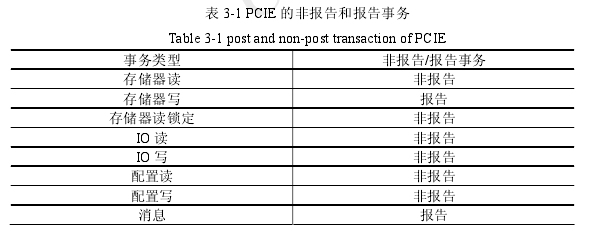

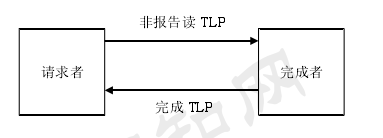

报告事务与非报告事务的区别是:请求者发起一个非报告事务给完成者,完成者完成事务之后要发起一个完成数据包给请求者。而报告事务不需要完成者发送完成数据包。

3.2 非报告事务与报告事务

非报告读事务的传输过程为:请求者发送一个非报告请求TLP给它打算读取其数据的完成者。其中非报告读请求TLP包括存储器读请求,IO读请求和配置读请求,请求者可以是根联合体或者端点设备。

非报告写事务与非报告读事务的传输过程类似,请求者发送非报告写请求TLP给它打算写入数据的完成者。非报告写请求TLP包括IO写请求和配置写请求。存储器写请求和消息请求是报告事务。请求者为根联合体或者端点设备。

当完成者接收该请求数据包并解码其中的内容时,它接收数据。完成者创建一个没有数据的完成数据包,确认成功接收到写请求。这是完成的目的。

3.3 PCIE的分层结构协议

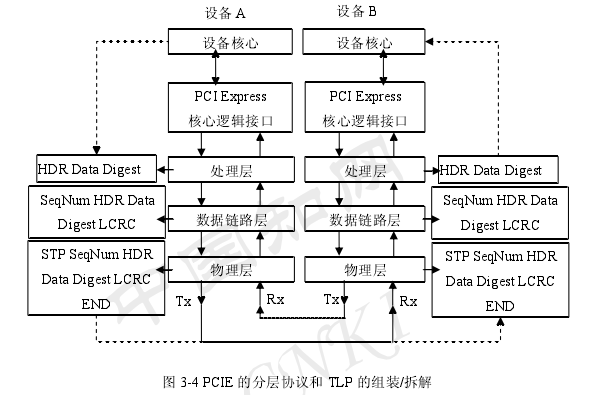

针对三种设备层,PCIE有三类数据包,每一类语气中一个设备层相关,与处理层相关的是处理层数据包(TLP),与数据链路层相关的是链路层数据包(DLLP),与物理层相关的是物理层数据包(PLP)。PCIE事务使用的TLP起源于发送器设备的处理层,终止于接收器设备的处理层。当TLP通过发送设备的数据链路层和物理层时,他们对TLP的装备也起作用,在接收TLP链路的另外一端,由物理层、数据链路层和处理层拆解该TLP。

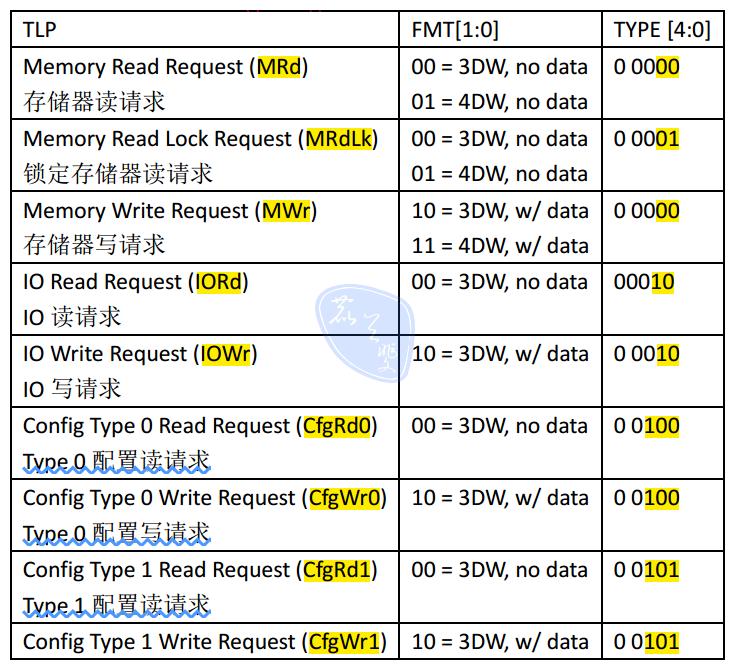

3.4 各种TLP包头格式

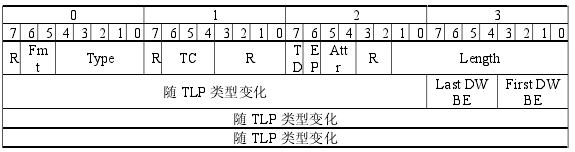

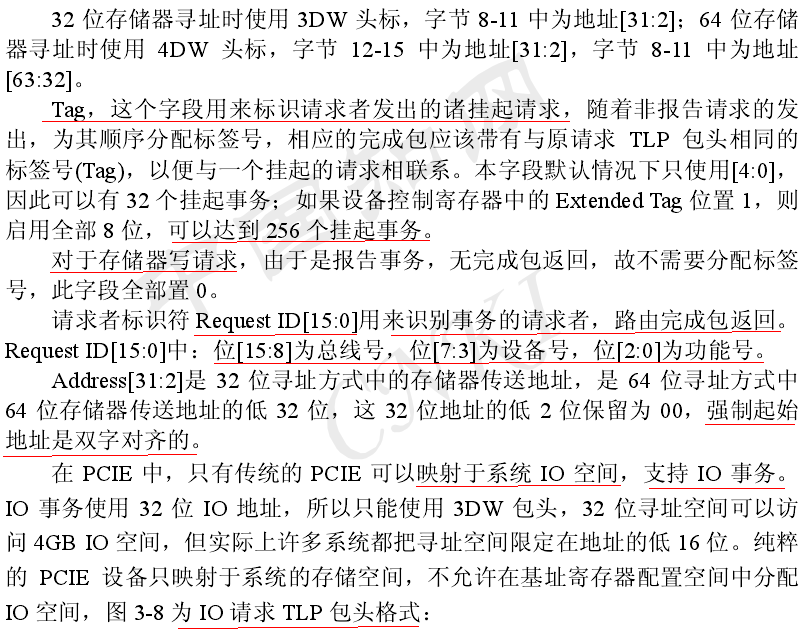

TLP包头长可能为3DW或者4DW,其每一位所代表的意义随着事务类型的不同而不同,其中,所有事务类型TLP包头的通用字段如图一所示:

图一 TLP包头中的通用字段

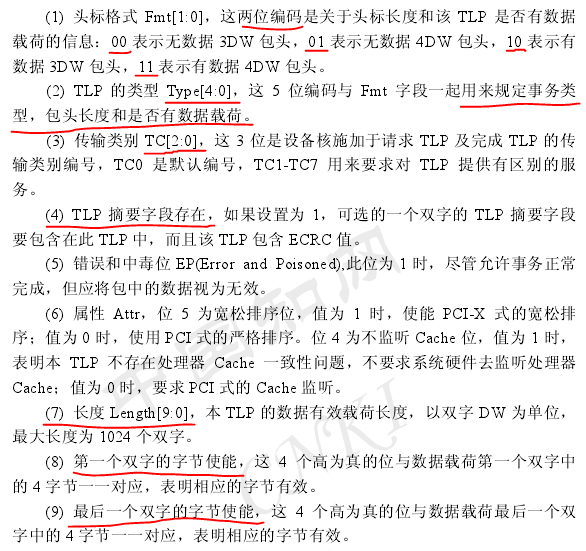

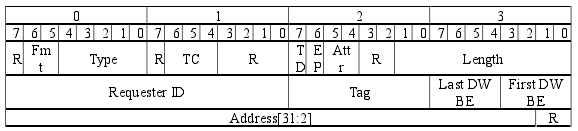

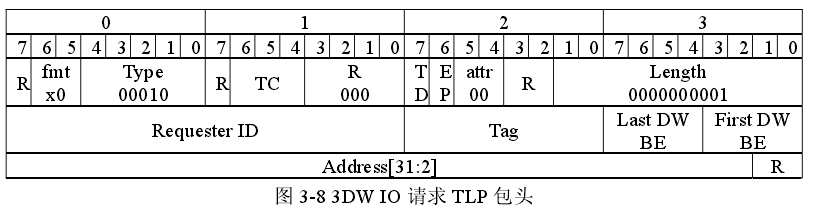

PCIE的存储器事务包括两类:读请求(完成)和写请求。图二和图三分别给出3DW 和4DW存储器读请求包的格式。

图二 3DW存储器读请求TLP包头

图三 4DW存储器读请求TLP包头

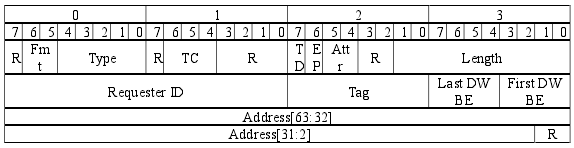

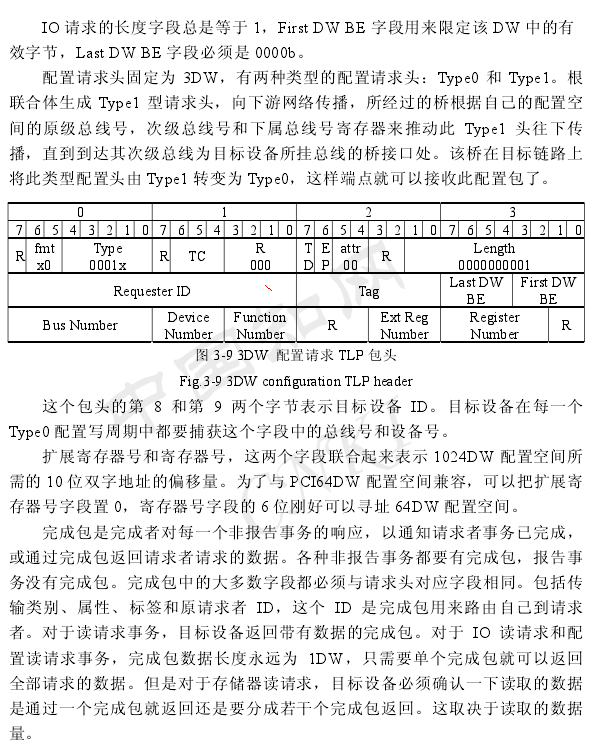

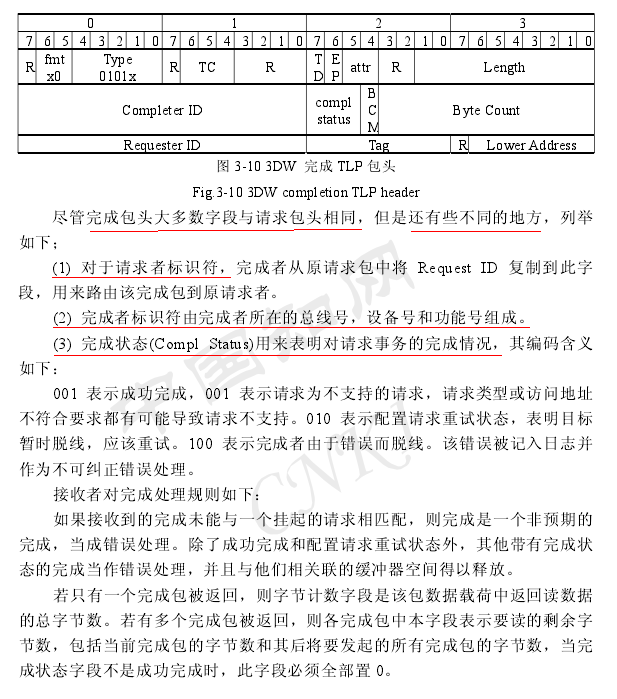

下图附上常见的几种TLP包类型:

4. Xilinx公司PCIe硬核简介

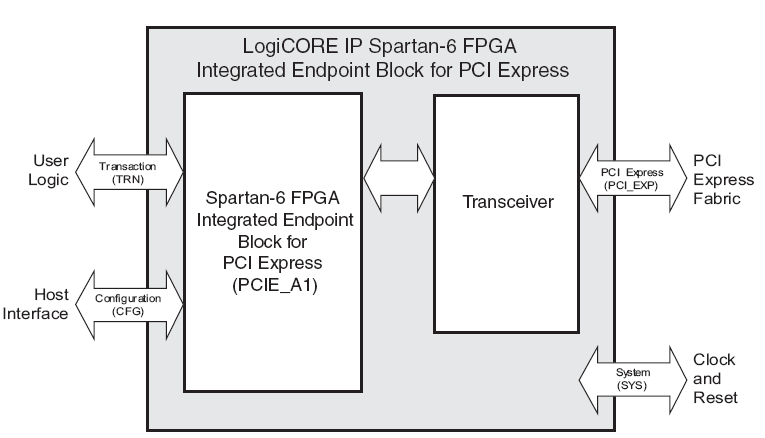

PCIe硬核内部结构

从图中我们可以看出整个PCIe硬核的接口,可以分为以下4种接口,分别是System(SYS)interface; PCI Express(PCI EXP) inteeface;Transaction(TRN) interface和Configurationinterface(CFG)。其中Host Interface(CGF)可以对PCIE进行配置,以控制器件的状态,或者读取PCIE的配置寄存器的值,让主机知道器件的状态。User logic(TRN)是需要自己设计的部分,用户根据自己的需要设计一个符合PCIE规范的local interface将user logic 和Endpoint连起来;PCIe Fabric 是器件的物理接口,接口可以传输2.5Gbps的差分信号,它直接与桥或者根联合体的物理层接口相连;系统时钟和复位(SYS)提供给PCIE工作时钟信号和复位信号。

XILINX的PCIE通过数据包实现不同模块之间的信息交换。数据包形成于IP核的传输层或数据链路层,携带必要的信息从发送部分传输到接受部分。在接收端对数据包进行处理,一层一层往上传输,即从物理层经过数据链路层最终传输到传输层。

根据PCIE规范的定义,IP核包含以下几个功能:产生并处理传输层数据包(TLPs),流控制管理,初始化及电源管理,数据保护,错误检查及重试,串行化,去串行化等功能。根据协议,该核包括如下三层:

传输层(处理层,事务层):传输层是PCIE的最上层,它的首要功能是接收、缓存和传输传输层数据包,并负责处理层数据包的合成与分解,进行流量控制管理,数据包队列管理以及利用对虚拟通道提供服务质量功能。

数据链路层:数据链路层如同联系传输层和物理层的媒介,它的首要功能是为TLPs在两层之间的传输提供可靠性支持,他可以进行错误检查以及恢复,产生并解析数据链路层包(DLLP),DLLP被用来在两个互联的PCIE的数据链路层之间传输信息,从而实现电源管理,流量控制以及TLP确认等功能。

物理层:物理层可分为逻辑物理层和电气物理层,逻辑物理层完成对PLP的合成和分解,8b/10b编码,10b/8b解码,并串转换和串并转换。电气物理层负责所有通道的数据差分驱动传输与接收。

注意:下面论述的是旧版本总线。新版本的IP核全部换成了AXI4总线接口,道理是相通的,根据IP核的用户手册依样画葫芦就是了。

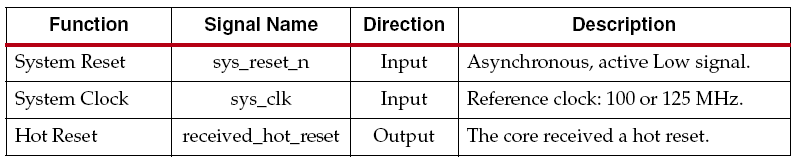

System(SYS) interface:主要包括系统时钟和复位信号:

系统复位信号是异步复位信号,低电平有效。系统时钟输入必须是100MHz或者125MHz,可以在生成ip核的GUI界面中设定。

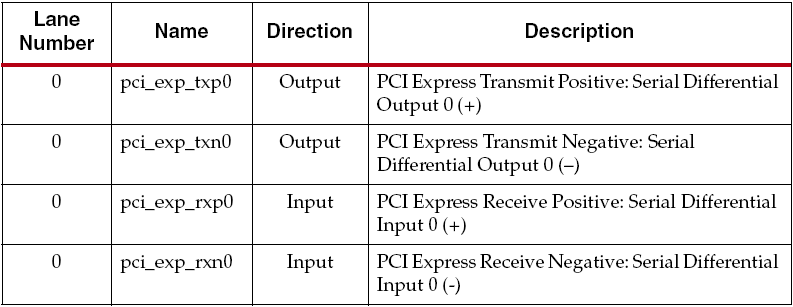

Ø PCI Express(PCI EXP):PCIe物理接口由发送和接收的差分对组成。一个PCI Express通道包含一对发送信号差分对和一对接收信号差分对。

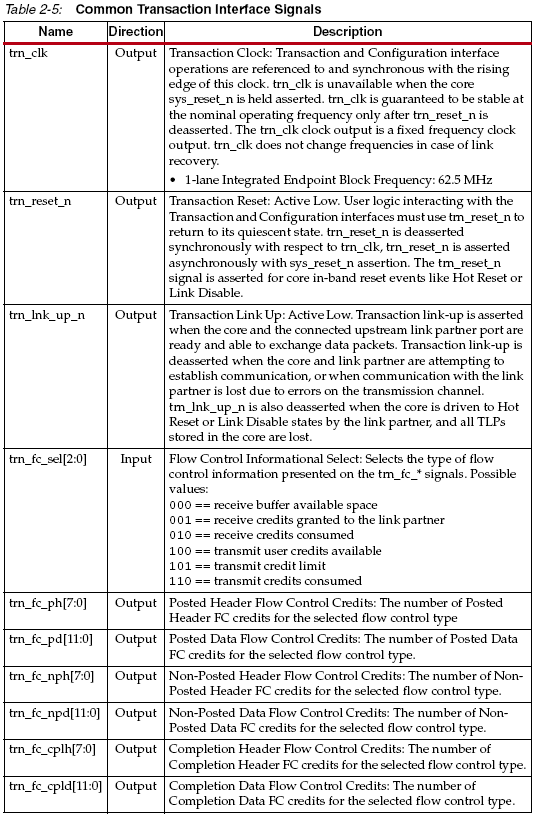

Ø Transaction(TRN) interface:事务层接口,该接口给用户提供了一种产生和分解TLPs的机制。也可以叫用户逻辑接口,是连接PCIE和User Logic的接口,他输出符合PCIE规范的TLP包给用户逻辑,或者接收来自用户逻辑的数据包。用户需要自行设计自己的电路对接收到的数据包进行解码,然后根据解码结果做出相应的相应,:如果是非报告事物,用户逻辑就需要组织自己的数据包通过用户逻辑接口发送给PCIE。该接口可以细分为3类,即Common TRN Interface、Transmit TRN Interface和ReceiveTRN Interface,具体信号的描述如下:

其他部分信号,请参照用户手册,这里就不意义列出了。

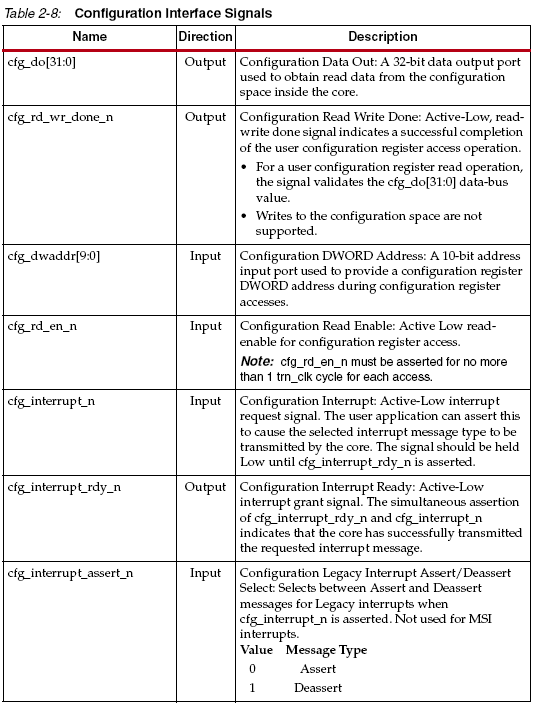

Ø Configuration interface(CFG):配置接口可以让用户访问并检测PCIe Endpoint的配置空间,10位的地址信号可以让用户寻址所有的1024个DW配置空间。对配置空间的访问是由配置请求来实现的,配置请求头有两个字段来表示配置空间各寄存器的偏移地址,分别是:寄存器数号和扩展寄存器数号。寄存器的数号为10位地址的低6比特,他可以访问64个双字的地址。扩展寄存器数号为高4比特,他跟寄存器数号的组合可以访问1024个双字地址,这样的设置为后向兼容PCI设备提供了方便。MSI中断方式以及传统的中断也都是通过配置接口发送。配置接口的具体描述如下:

这里也仅列出部分信号,详细的请参考用户手册。

5. Xilinx PCIe硬核配置

PCIe硬核的配置主要需要完成以下内容:基础参数设置、基址地址寄存器(BAR)设置、配置寄存器设置等。其中基础参数设置包括通道宽度、接口频率、器件ID值以及类码等。BAR设置是指用户完成对BAR地址空间的设置。配置寄存器允许用户定义设置设备功能寄存器和链接功能寄存器。设备在默认设置下高级设置被保留。

END

原文链接: https://mp.weixin.qq.com/s/fAzQ30knz79y5ATc262-ZQ

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。