本文将介绍如何创建一个支持 HDMI 输入到输出的图像处理平台。这可以用作基于 HLS 的图像处理演示的基础。

概述

该项目将演示如何基于 Xilinx Zynq 创建一个简单的图像处理平台。然后,该项目将用作后续开发的基础,这些开发侧重于基于高级综合的开发,允许使用行业标准 OpenCV 库。

为了创建这个示例,我使用 Zybo Z7,因为它提供 HDMI 输入和输出,以及用于 MIPI 相机的 CSI-2 接口,我们也可以将其用于未来的开发。

除了 Zybo-Z7,我们还将使用:

- HDMI 摄像头,例如 Apeman 1080P 运动摄像头

- HDMI 输入和输出端口的相关电缆

- HDMI显示

为了创建应用程序,我们将使用以下开发工具和库:

- 维瓦多 2017.4

- 赛灵思 SDK 2017.4

- Digilent Vivado 库

要创建此示例,我们需要执行以下准备步骤:

- 将 Digilent Vivado 库下载并解压到您的计算机

- 安装 Digilent Board 定义,如果您不确定如何执行此操作,请单击此处

- 创建一个针对 Zybo-Z7 的新 Vivado 项目

- 在 Vivado 中创建新的框图

构成

在 Vivado 框图中,我们需要添加以下 IP:

Zynq 处理系统 -这将提供图像处理系统的配置和控制,同时它的 DDR 也用作帧缓冲区以确保以下配置

- PL 时钟 0 = 200 MHz

- PL 时钟 1 = 100 MHz

- HP 0 Slave enabled - 这将用于将图像传输到 PS DDR 或从 PS DDR 传输图像

- GP 0 Master enabled - 用于配置图像处理链

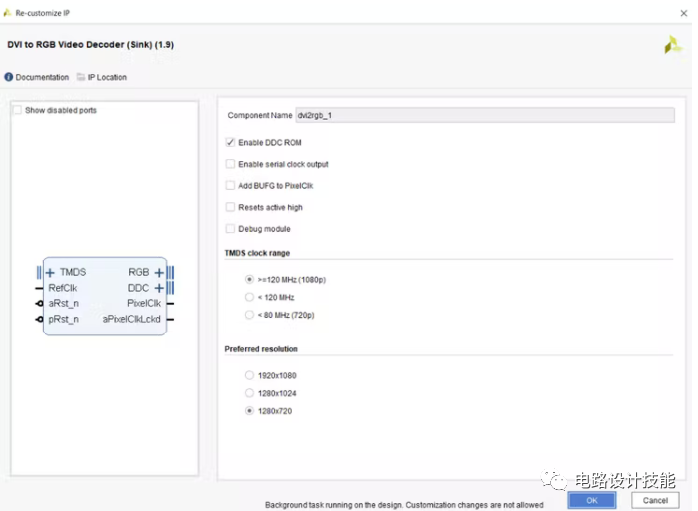

DVI2RGB -这将 HDMI 视频流转换为具有适当垂直和水平同步的 24 位 RGB 总线。

AXI GPIO - 用于断言 HDMI 源上的热插拔检测的单个输出,未能断言这可能意味着没有接收到视频。

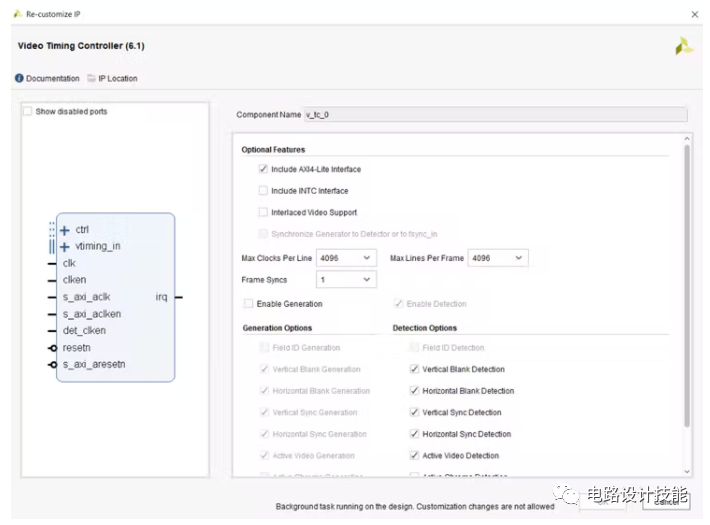

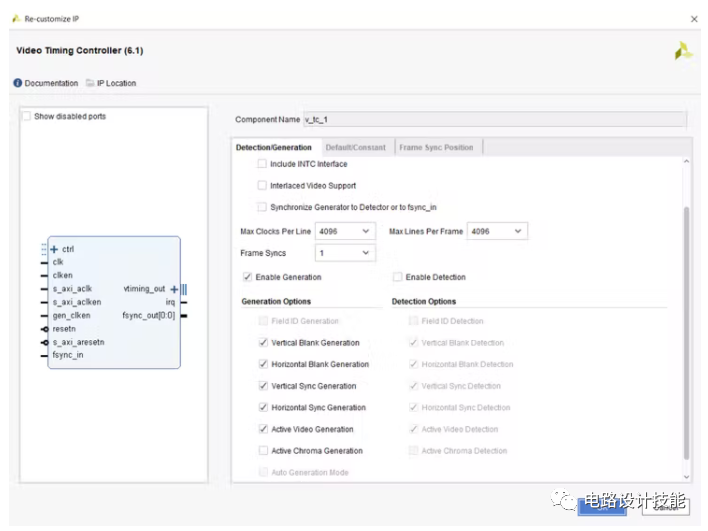

视频定时控制器- 配置为检测,这将检测从 HDMI 源接收的视频的模式。

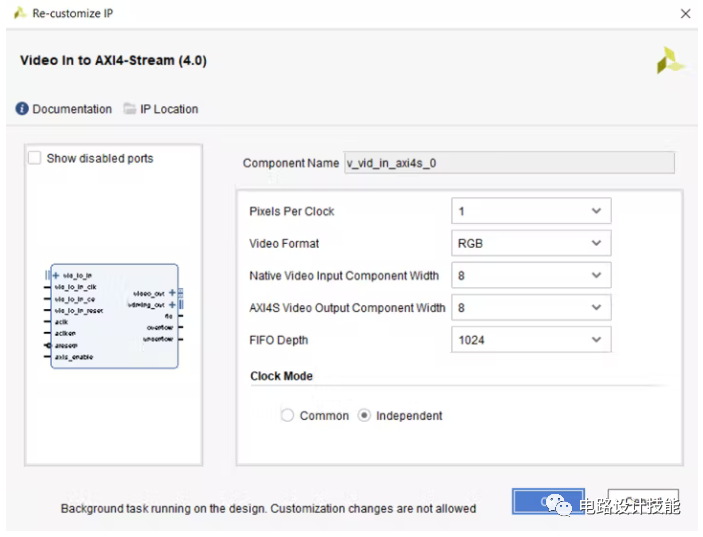

视频输入到 AXIS -这会将并行视频和同步转换为 AXI 流。与 TDATA 上的图像数据一起,帧的开始由 TUser 信号标识,而行尾由 TLast 信号标识。

将此配置为具有独立时钟,以便像素时钟和 AXI 流时钟不同。

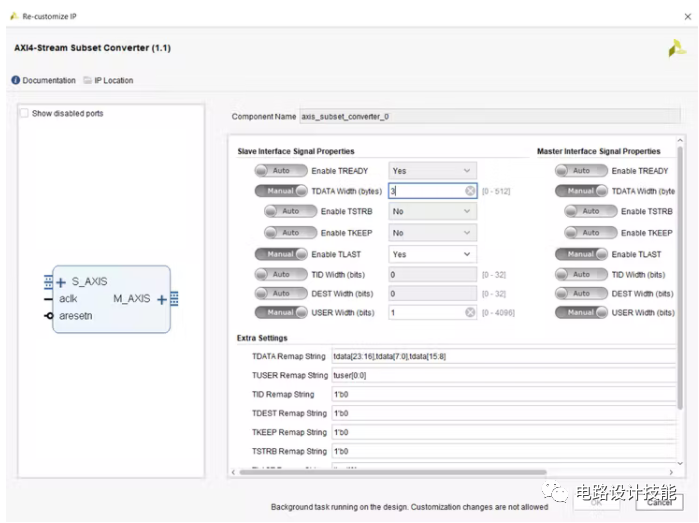

AXIS 子集转换器 -此组件将 24 位视频输出的格式重新映射为正确的 RGB 格式。其中两个在 VDMA 之前和之后使用。

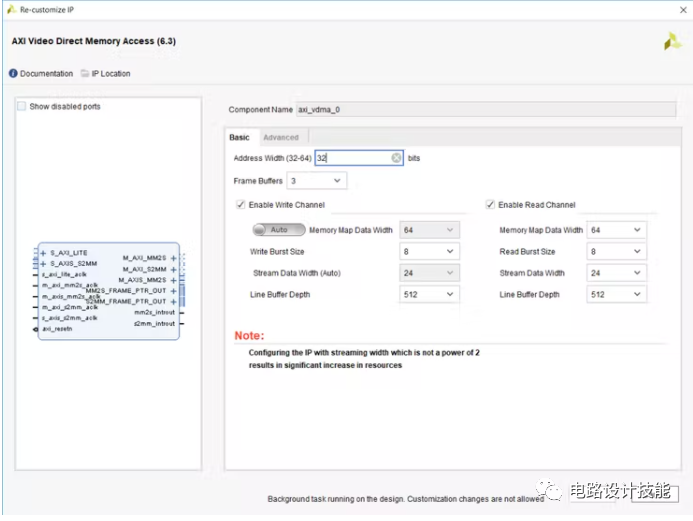

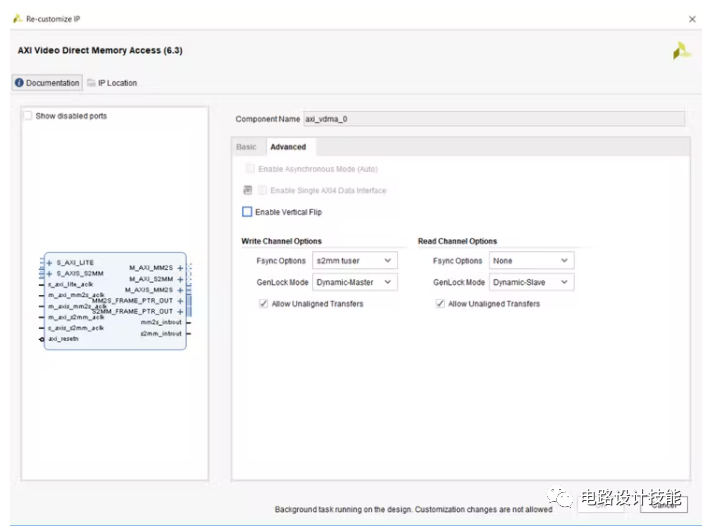

视频直接内存 -写入通道将 AXI 流视频移动到 AXI 内存映射形式,以便存储在 PS DDR 内存中。而读取通道访问 PS DDR 并将 AXI 内存映射格式转换为 AXI 流以供输出。确保启用两个方向。

视频时序控制器- 配置为时序源,配置所需的时序取决于输入视频时序。这被 AXIS 用于视频输出以生成输出并行视频和同步

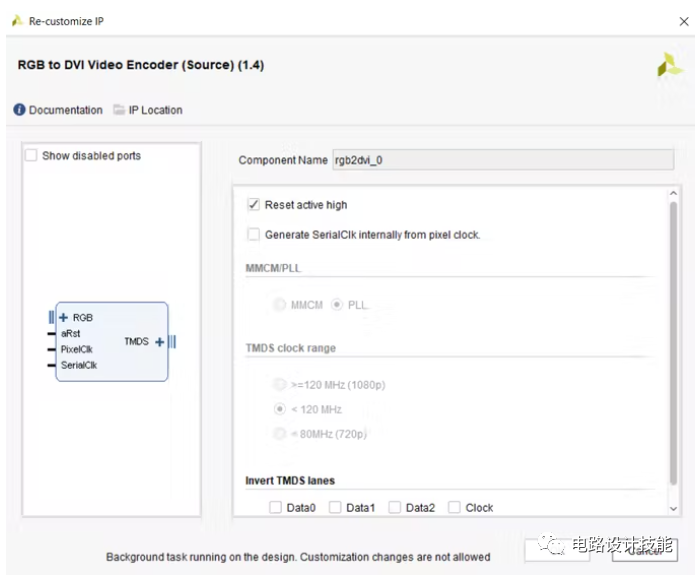

RGB2DVI -这将输出并行视频和垂直和水平同步转换为 HDMI

为了支持动态配置输出时钟,使用了 Digilent Vivado 库中的动态时钟发生器。这允许使用 AXI lite 根据接收到的视频格式来改变像素时钟频率。

Vivado 项目

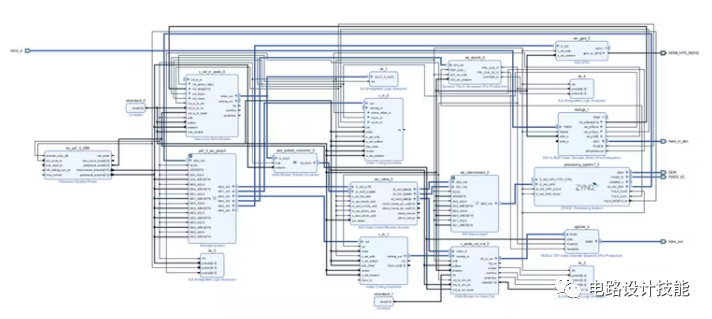

将所有这些放在一起可以创建一个 Vivado 项目,如下所示。

然后可以构建 Vivado 项目并将其导出到 Xilinx SDK 以使我们能够创建应用软件。

在 Xilinx SDK 中,我们需要编写我们的软件应用程序来执行以下操作:

- 断言连接到 HDMI IN 热插拔检测的 GPIO - 断言此信号后,处理器等待 5 秒以确保 HDMI 源生成视频。

- 配置视频定时控制器(检测器)以报告传入视频模式。

- 配置视频时序控制器(生成器)以根据检测视频模式生成时序。

- 配置动态时钟

- 将 VDMA 配置为从 PS DDR 读取和写入数据

运行应用程序 SW 应该可以让您看到所选 HDMI 源上的图像。

实物

总而言之,这个项目为我们提供了一个想法平台,我们可以在未来使用它来展示我们基于 HLS 图像处理的应用程序。

项目链接:https://github.com/ATaylorCEn...

以上内容翻译自网络,原作者:Adam Taylor,如涉及侵权,可联系删除。

👉要查看详情

请猛戳底部“阅读原文”

END

原文链接: https://mp.weixin.qq.com/s/cGGtVLgznmTxnAodZtUHbg

微信公众号:

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。