LDPC码属于前向纠错码的一类,用于在噪声传输信道中发送信息。这些码可以用一个奇偶校验矩阵来描述,该矩阵主要包含0和少量的1。因此,与其他代码结构相比,译码复杂度较小。解码器采用了一种非常高效的迭代译码算法——置信传播算法。LDPC码可分为两组:规则LDPC码,PC矩阵的列重和行重是常量且相等;不规则的LDPC码,所在的行重和列重不是常数和相等,这意味着每行和列1的数量是不同的。

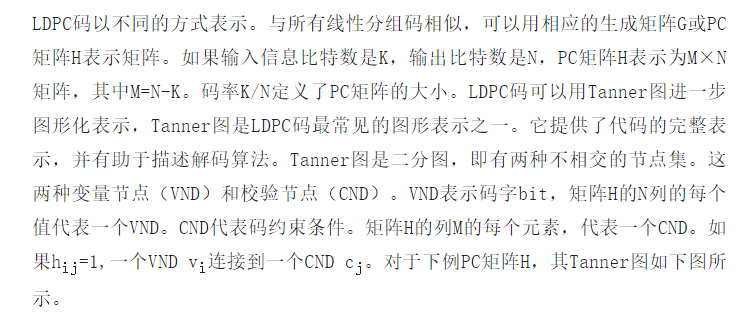

H矩阵对应的Tanner图

准循环(QC)LDPC码属于结构化码的一类,在不显著降低代码性能的情况下相对容易实现。QC-LDPC码可以使用简单的基于其生成矩阵的线性复杂度的移位寄存器来实现。设计良好的QC-LDPC码已被证明在BER、BLER性能和错误平层方面优于计算机生成的随机LDPC码。这些码在解码器硬件实现方面具有循环对称的优点,可以实现简单的规则互连和模块化结构。在包括3GPP NR在内的大多数无线通信标准中,LDPC码的定义都采用了基本图u。然而,u需要使用提升因子Z转换为PC矩阵H。提升意味着基本图u的每一个(整数)项都被一个置换的Z×Z单位矩阵所取代。我们从一个单位矩阵I开始,并根据基图项uij循环移动该矩阵的元素以得到所需的矩阵H。例如,假设有一个2×2的基图矩阵u和提升因子Z=3。从u到H的变换可以这样进行:

LDPC码通常由它们的PC矩阵确定。本文给出了一个QC-LDPC码的PC矩阵,它是一组相同大小的稀疏循环矩阵。循环矩阵是一个方阵,其中每一行是其上一行的循环移位,第一行是最后一行的循环移位。对于循环矩阵,每一列是左列向右的循环移位,第一列是最后一列的循环移位。循环矩阵的行重和列重是相同的。如果行/列权重等于1,那么循环矩阵也是一个置换矩阵。循环矩阵的第一行(或第一列)是其完整的特征,称为循环矩阵的生成器。对于一个在GF(2)域的m×m的循环矩阵A,如果它的秩为r=m,那么它所有的行都是线性无关的。然而,如果它的秩r<m,那么任意连续的r行(或列)A可以被认为是线性无关的,而其他的m-r行(或列)是线性相关的。这是由于A的循环结构。一个QC-LDPC码是由一组相同大小的稀疏循环矩阵的零空间给出的。

LDPC码的译码算法是独立发现的,它们有不同的名称。最常见的是BP算法、消息传递算法(MPA)和和积算法。在BP算法中,概率消息在变量和检查节点之间迭代交换,直到找到有效码字或超过最大迭代次数。LDPC码可以使用消息传递或二分Tanner图上的BP进行解码,CND和VND相互通信,在每次解码迭代中依次传递相关LLR的修正估计。Bit的可靠性度量被定义为:

其中,bi代表接收码字的第i比特。如果LLR>0,意味着更有可能bi=0,当LLR<0,意味着更有可能bi=1。

举个例子,假设发射的码字(0,0,0,0,0,0,0,0,0,0,0),译码器接收到的码字为(0,0,0,0,1,0,0,0,0,0,0)。11bit有效码字c=(c0,c1..,c10),所有比特应该等于0(mod 2)。接收向量不满足此约束,表明接收码字出现了错误。进一步,假设解码器具有比特级可靠性度量,其形式为正确概率(接收值的置信度)为(0.9,0.8,0.86,0.7,0.55,1,1,0.8,0.98,0.68,0.99)。这些软信息中,比特c4可靠性最低,应翻转以带来符合代码约束的接收码字。使用LLR作为消息,与消息传递算法相比,硬件实现变得容易得多。通过简化消息传递算法中最复杂的CND更新过程,进一步降低了实现的复杂性。这种算法被称为最小和算法(min-sum algorithm)。

LDPC解码器可以使用串行、并行或部分并行架构来实现。LDPC解码器的性能取决于解码器的算法、架构、LLR的定点量化和最大译码迭代次数等因素。译码过程中使用的最大译码迭代次数决定了LDPC译码器的数据速率和延迟。在执行最大译码迭代次数之后,然后估计码字。为了节省解码器功耗和减少延迟,需要在每次迭代后验证码字,并在估计的码字正确时停止解码过程的解码器设计。如果在下次迭代开始时,估计码字奇偶校验得到满足,则译码过程停止。

LDPC码与常见的几种纠错码相比,其性能有较大优势,因而可满足5G高数据率、低延时和高可靠等应用需求。

LDPC码与其他纠错码性能对比

上面介绍了LDPC码的基本原理,重点把握几个概念:

- 什么是变量节点?

- 什么是校验节点?

- 校验矩阵H与Tanner图之间的相互转换过程。

- QC-LDPC码的基本特点是什么?

- LLR的具体求解方法。

- LDPC译码算法有哪些?译码算法各自的特点,以及硬件实现复杂度评估。 - 影响LDPC译码性能的几个关键因素是什么?

- 如何有效提升LDPC译码性能?(BLER、吞吐率)

对于LDPC码在DVB-S2、WLAN和5G NR中的具体应用,其码率和码块长度有所不同。特别是在5G NR中,将支持低至1/5、高至8/9的多种码率,在Sub-6GHz频段100M带宽下,下行需满足1~3Gbps、上行几百Mbps~Gbps的数据速率需求。而在毫米波频段,需要更高的吞吐率需求。

关于LDPC译码算法,可阅读前期文章《5G通信算法:LDPC译码算法详解》。

从通信系统角度看,除高速接口外,基带的信道编解码器和射频前端的AD/DA的设计,是最难的部分,然而这在很大程度上决定一款产品的竞争力。当然,各种滤波器、功放、MIMO估计与均衡器,也是影响性能的重要部件。

那么,我们该如何采用FPGA自行设计一款LDPC编解码器呢?在设计之前,我们需要基于某一标准或自定义LDPC码,完成相应的算法分析和资源评估,同时对其中的关键模块要有相应的实现方案。在具体设计实现时,RTL模块设计高内聚、低耦合,同时参数和控制逻辑应友好灵活,并以较少的资源实现整个功能,并尽可能提升时钟运行频率。

来源: FPGA算法工程师

作者: Duoqiang Liu

原文链接:FPGA算法工程师

推荐阅读

更多IC设计技术干货请关注FPGA的逻辑技术专栏。