趁着元旦假期,我们来捋一下芯片设计中的几个基础问题。

我们都知道,最近关于芯片设计与制造的话题,依然占据着人们的茶前饭后时间,敌人的围追堵截,使我们丢弃幻想,奋起抗争。在我们的工作中或生活中,不论处于半导体行业的上游还是下游,对于芯片都无法避开,缺了它,我们寸步难行。

当你在家开着空调,从冰箱里拿出一瓶冰可乐,葛优躺拿着手机刷视频时,你希望视频流畅无卡顿。在这背后,是一群群芯片设计工程师、移动通信工程师、网络工程师、图像处理工程师、芯片开发/验证工程师、芯片制造工程师、芯片封装测试工程师......日以继夜奋斗的结果。

任何一款芯片的设计,都需要庞大的设计和验证团队进行密切合作共同完成。在芯片设计中,我们需要考虑众多因素。那么,我们的脑海里在想些什么呢?

芯片逻辑开发工程师的三重境界:心中有电路,脑中有时序,手中有代码。

如果我们在设计中使用同步设计或任何IP,或最终确定体系结构和微体系结构,那么我们需要制定各种策略。以下列出了其中一部分:

- 设计的功能性和兼容性

- 并行性、并发性和流水线策略

- 外部IO和高速接口

- 设计的面积和初始门数估计

- 速度和最高频率要求

- 功耗要求和使用低功耗设计

- 时钟网络和延迟

- 接口和IO延迟与建模策略

经过以上考虑,由经验丰富的技术人员组成的团队最终确定ASIC/ SOC 设计的架构和微架构。

为了便于理解架构和项目研发,我们需要考虑的一些设计因素,主要有以下几个方面。

01 时序参数

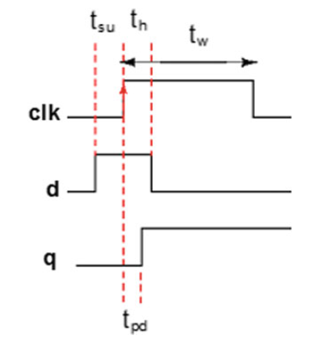

上升沿敏感触发器的重要时序参数如图1所示,它们是:

- 建立时间 (tsu)

- 保持时间(th)

- 触发传播延时(tpd)

图1 D触发器时序参数

建立时间(tsu):在时钟的有效边沿到达之前,触发器的数据输入应该保持稳定值的最小时间被称为建立时间。

有效边沿表示上升沿(正边沿)灵敏的D触发器从低电平到高电平的跳变,下降沿(负边沿)灵敏的D触发器从高电平到低电平的跳变。

在建立时间窗口期间,如果数据输入从1到0或反之,那么触发器输出将是亚稳态的,这表明存在建立违例。

保持时间(th):触发器的数据输入在时钟有效边沿到达后保持稳定的最小时间,称为保持时间。

有效边沿表示上升沿(正边沿)灵敏的D触发器从低到高的跳变,下降沿(负边沿)灵敏的D触发器从高到低的跳变。

在保持时间窗口期间,如果数据输入从1到0或反之,那么触发器输出将是亚稳态的,这表明存在保持违例。

触发器的传播时延(tpd\=tcq):触发器到达时钟有效边沿后产生有效输出所需的时间,称为触发器的传播时延。

传播延迟也称为时钟到q端的延迟,也称为tcq。

02 亚稳态

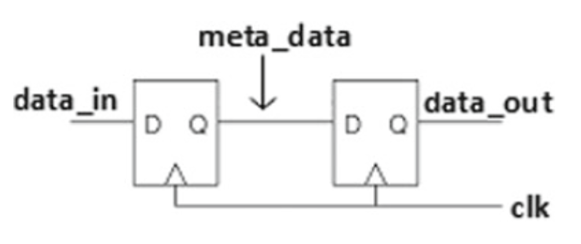

如果将图2所示设计的数据输入连接到另一个模块上,该模块的时钟由不同的时钟源产生,则第一个触发器输出将处于亚稳态。

meta_data表示触发器数据是亚稳态的,因此第一个触发器存时序违例。亚稳态表明数据输出是无效的,为了得到有效的数据输出,设计需要使用多电平同步器。

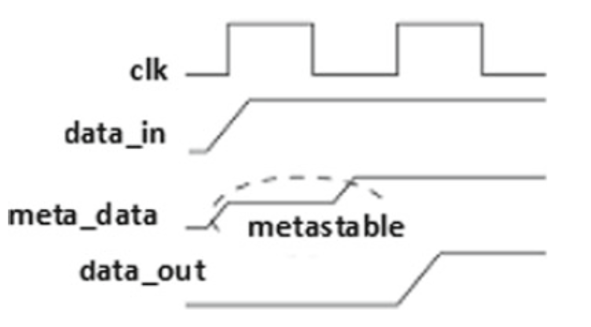

所述第一触发器所采样的数据与所述第二触发器的输出的时序如图3所示。如图所示,第一个触发器的输出处于亚稳态,输出触发器的data\_out输出处于合法有效状态。

图2 电平同步

图3 亚稳态电平同步时序

03 时钟偏斜

如果ASIC设计中有多个时钟,那么时钟分布和时钟树综合将对平衡各块不同时钟输入之间的时钟偏斜起到非常重要的作用。

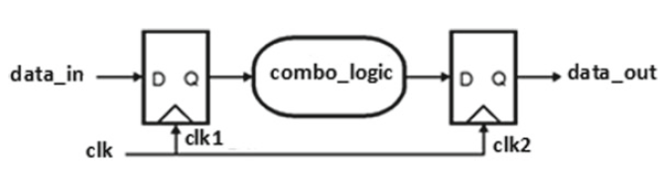

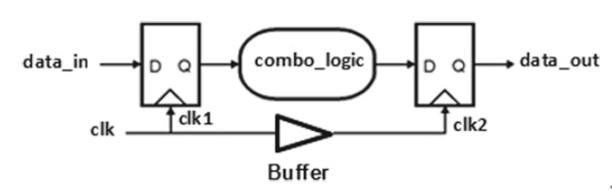

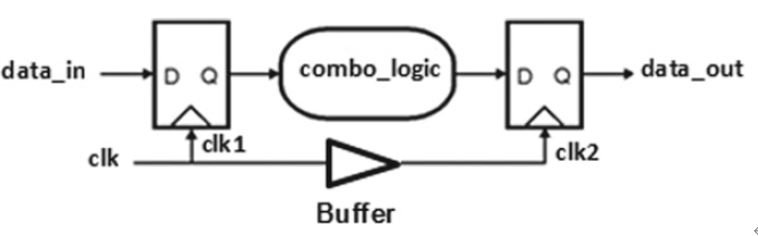

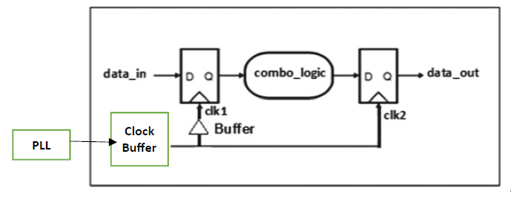

如果设计中的两个不同的时钟到达不同的时间实例,则设计具有时钟偏斜。时钟偏移的原因是路由延迟,即单时钟域设计的线延迟。考虑所示的图,让我们考虑在发射触发器的clk边缘在时间实例t0到达,在时间实例t2捕获触发器。由于这个同步设计的时钟到达时间不同,clk1和clk2之间存在相移,我们可以认为这是时钟偏移。另一个原因是振荡器的老化;然后,振荡器产生的时钟周期频率变化,因此到达时间的差异可以称为抖动。

图4 同步设计

在图4中,时钟偏斜是由于clk1引脚和clk2引脚之间的互连延迟引起。

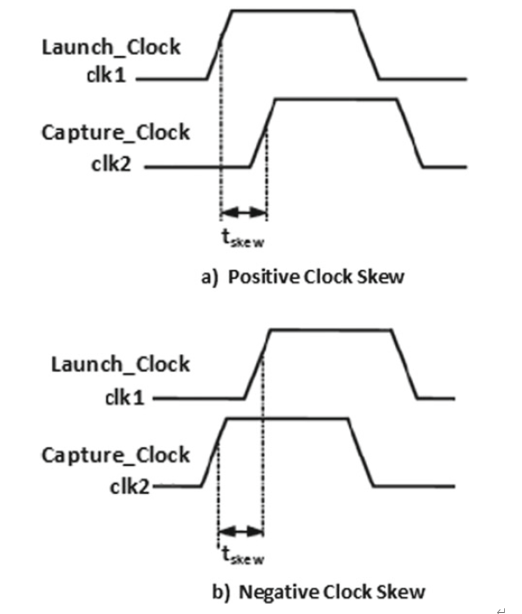

在实际的专用集成电路设计中,我们经历了两种不同类型的偏置,如图5所示。

正时钟偏移:表示先触发发射时钟clk1,再到达捕获时钟clk2。如图中tskew,它是clk1和clk2到达时间的差值。换句话说,我们可以想象正时钟偏斜是数据和时钟在相同的方向上运行,正时钟偏斜有利于建立时间,但对保持时间不好,因为有正的margin来管理。

负时钟偏移:最后触发发射时钟clk1,第一个触发捕获时钟clk2。如图中tskew,它是clk1和clk2到达时间的差值。换句话说,我们可以想象负时钟偏移是数据和时钟在相反的方向上运行,负时钟偏移对保持时间更好,但对建立时间不好。

图5 设计中的偏移

在ASIC设计中,我们总是会遇到由于抖动或互连(即线延迟)而产生的时钟偏斜,下面是我们应该知道的要点。

- 正时钟偏斜有利于建立时间,但不利于保持时间。

- 负时钟偏斜有利于保持时间,但不利于建立时间。

正时钟偏斜(positive clock skew)

如前面所讨论的,正时钟倾斜发射触发器首先被触发,然后在捕获触发器被捕获。在发射时钟和捕获时钟之间有缓冲延迟的裕度,可以用来提高设计所需的频率。

图6显示了时钟正向斜向的同步设计,clk1和clk2之间的偏斜是tbuffer。

图6 正时钟偏斜

让我们找出所需的数据时间和数据到达时间。

Data Arrival Time(AT)=tpff1+tcombo

Dara Required Time(RT)=Tclk+tbuffer-tsu

其中,Tclk是时钟周期或时钟到q端的延时。tbuffer是缓冲延时,tsu是触发器建立时间,tpff1是触发器传播延时,tcombo是组合逻辑延时。

建立裕量(setup slack)是数据所需时间和数据到达时间之间的差值,应该为正。正的建立时间裕量表明设计中不存在任何建立违例。为了避免设计中的建立违例 ,设计应该具有快速数据、快速启动时钟(clk1)和慢捕获时钟(clk2)。也就是说,与所需的数据时间相比,数据的实际到达应该更快。(如图7所示)

图7 触发和捕获时钟之间的关系为正时钟偏斜

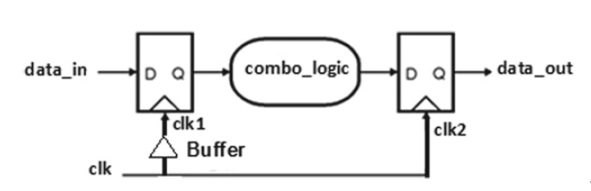

负时钟偏斜(negative clock skew)

如前面所讨论的,负时钟偏斜,在发射触发器最后触发和捕获触发器首先被触发。由于在触发时钟和捕获时钟之间有缓冲延迟的裕度,这降低了设计的最大频率。

图8显示了负时钟偏移的同步设计,clk1和clk2之间的偏移是tbuffer。

让我们找出所需的数据时间和数据到达时间。

**Data Arrival Time(AT)=tbuffer+tpff1+tcombo

**

Dara Required Time(RT)=Tclk-tsu

图8 负时钟偏斜

图9 触发和捕获时钟之间的关系为负时钟偏斜

04 裕量(slack)

在ASIC设计中,有两个术语用于描述裕量,即建立裕量(setup slack)和保持裕量(hold slack)。

图10 同步设计中的寄存器到寄存器路径

建立裕量(setup slack)

建立裕量是数据所需时间和数据到达时间之间的差值,应该为正。正的建立裕量表明设计中不存在任何建立违例。

**Data Arrival Time(AT)=tbuffer+tpff1+tcombo

**

Dara Required Time(RT)=Tclk-tsu

Setup Slack=RT-AT

保持裕量(hold slack)

保持裕量是数据到达时间和数据需要时间之间的差值,应该是正的。正保持裕量表明在设计中没有任何保持违例。

05 时钟延迟

时钟由锁相环产生,用于单时钟域设计,对于多个时钟域,我们可能需要多个锁相环。

时钟网络引入了延迟,它实际上是时钟到达芯片所需的时间,时钟延迟是由时钟分布过程中的时钟网络延迟造成的。

图11 时钟网络延迟

06 设计的面积

ASIC的总面积是由标准单元、宏和IP核组成的。在集成电路的百万或亿门设计中,面积的限制和更好的布局规划对获得预期性能起着重要的作用。我们可以在不同的设计阶段考虑面积优化,例如:

- 在体系结构设计过程中,通过不同功能块交互描述,获取更好的策略。

- 在RTL设计过程中,使用基于工具的指令和命令,并使用资源共享技术。

- 在版图阶段的物理设计中,通过策略来放置功能块,最小化由于布线延迟和布线资源使用而造成的面积消耗。

07 速度要求

在ASIC设计中,速度是另一个重要的考虑因素。采用不同的速度改进技术可以提高专用集成电路的性能。例如,考虑到处理器设计工作在500MHz的工作频率,我们面临着提高设计频率的挑战。在这种情况下,ASIC设计周期中可以使用各种策略,但可能很少使用:

- 在体系结构和微体系结构设计时,具有较好的顺序边界划分。

- 在初始版图中,相互依赖的块可以彼此靠近地放置,以最小化面积,从而减少布线延迟,并提高速度。

- 在RTL设计阶段,使用平衡寄存器和寄存器复制、优化命令来提高设计性能。但它们可能会影响逻辑面积。

- 在RTL设计过程中,使用寄存器的输入和输出,使设计具有更好的性能。

- 只要可行,就使用流水线的概念和体系结构。

- 如果需要在设计中使用FSM设计和控制器,则尝试在控制和数据路径综合方面进行工作,以获得干净的时序和更好的性能。

- 尽量使用同步设计,因为它们比异步设计更快。

- 尽量避免内部时钟发生器;相反,考虑时钟树并在CTS期间优化时钟树。

- 在布线阶段,尝试使用基于工具的改进技术,因为启用工具指令可以在平衡时钟偏斜方面发挥特别重要的作用。

08 功耗要求

对于任何类型的ASIC或SOC设计,重要的考虑是功率,设计团队的目标是减少泄漏和动态功耗。在物理设计过程中考虑功率约束进行功率规划。在ASIC设计流程的不同阶段,应采用功率优化技术。

- 具有低功耗感知的ASIC架构。

- 在不同的设计级别使用UPF。

- 在RTL期间,为了最小化动态功率,使用专用的时钟门控单元。

- 通过避免不必要的数据值分配和切换,还可以在RTL阶段优化功率。

- 在物理设计过程中,对多个功率域有更好的功率规划和功率排序。

- 在物理设计过程中有较好的断电策略。

09 设计约束

设计约束基本上是设计规则约束和优化约束。我们可以将这些约束考虑为模块级约束、顶层约束和芯片级约束。

设计规则约束(DRC):我们可以将这些约束视为芯片制造商的规则,并应予以满足。在物理设计过程中,我们将进行芯片制造商的所有DRC检查规则是否满足。Layout is clean表示没有DRC违规。这些约束主要是:

- Transition

- Fanout

- Capacitance

优化约束:这些约束在设计和优化阶段使用。这些约束主要是

- Area

- Speed

- Power

主要使用Synopsys DC,我们将利用面积和速度约束,并将在各个优化阶段尝试优化设计。

物理设计工具,如Synopsys IC Compiler,利用面积、速度、功率的约束来满足最终的约束,实现干净的芯片布局。

-----END-----

来源: FPGA算法工程师

作者: Duoqiang Liu

原文链接:FPGA算法工程师

推荐阅读

更多IC设计技术干货请关注FPGA的逻辑技术专栏。