PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

Version 4.3

©2007 - 2014 Intel Corporation—All rights reserved.

3 PHY/MAC interface

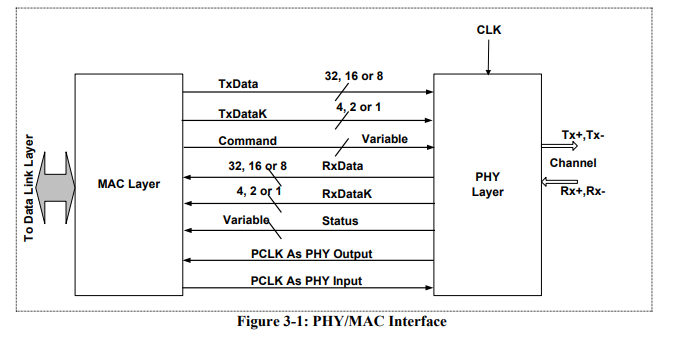

图 3-1 展示了 PHY 和 MAC 层模块之间的数据以及逻辑命令/状态信号。本文档的第 5 节将会讨论这些信号。支持 PCI Express, SATA, 以及 USB 等总线模式的 PIPE 信号有一些区别,具体哪些模式会用到哪些信号,可以参阅文档的第 6 节详细列表。

图 3-1 PHY/MAC 之间的接口

PIPE 协议支持多种不同的 PHY/MAC 间接口配置,以支持不同的信号速率。

3.1 PCI Express 与 USB 配置

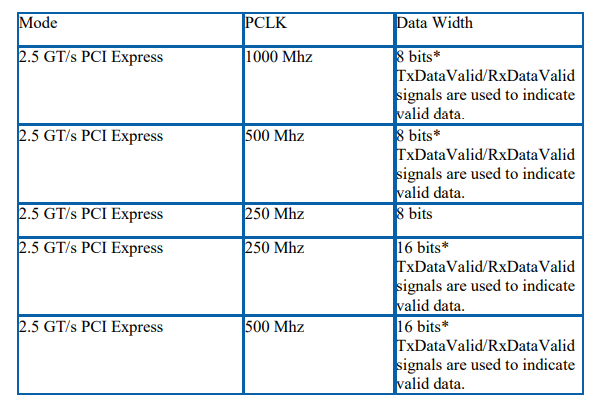

对于 2.5 GT/s 速率的 PCIe 模式,实现可以将数据通道位宽设置为 16 bit,PCLK 时钟频率设置为 125 MHz,或者将数据通道位宽设置为 8 bit,PCLK 时钟频率设置为 250 MHz。

对于支持 2.5 GT/s 以及 5.0 GT/s 两种速率的 PCIe 模式,运行过程中速率可以在两者之间切换,实现中可以选择多种不同的数据位宽和时钟频率组合。

首先,可以将时钟速率固定为 250MHz, 速率为 2.5 GT/s 时使用 8 bit 数据位宽,而在 5.0 GT/s 速率下使用 16 bit 数据位宽。

另一种实现方案是固定数据位宽,根据不同的数据速率来调整 PCLK 的频率。在这种情况下,数据通路位宽固定为 8 bit 的实现中, 速率为 2.5 GT/s 时 PCLK 工作在 250MHz,而在 5.0 GT/s 速率下 PCLK 频率提升为 500MHz。

类似的,如果数据通路固定为 16 bit,速率为 2.5 GT/s 时 PCLK 工作在 125MHz,而在 5.0 GT/s 速率下 PCLK 频率提升为 250MHz。

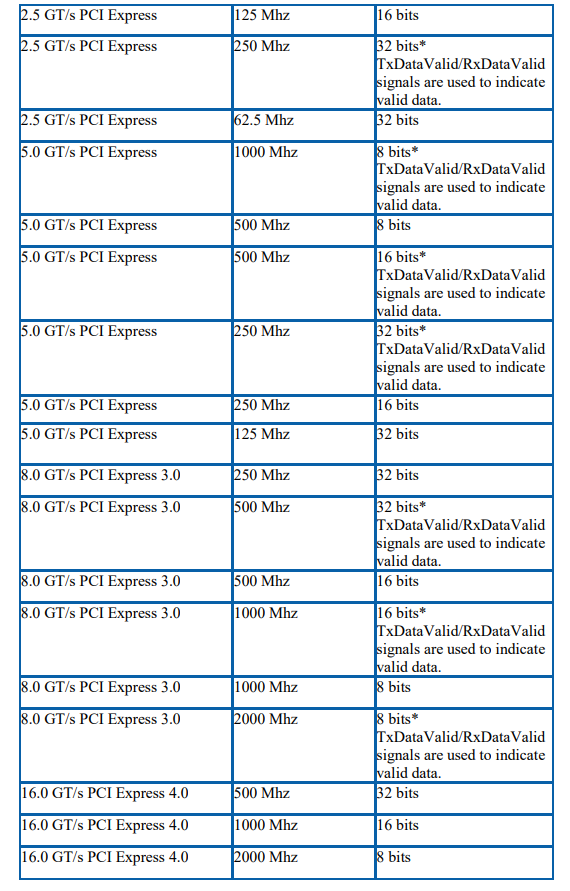

每种速率模式下 PCLK 频率与数据位宽的组合,总结为表 3-2 所示

表 3-2 PCIe 各速率模式下,可选的时钟频率与数据位宽组合

一组兼容 PIPE 协议的 MAC 和 PHY 之间的接口,仅需为每种 PCIe 速率支持一种实现方案即可。

3.2 USB 配置

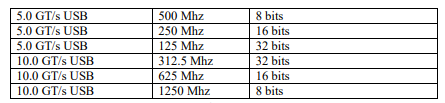

同样的,对于支持 5 GT/s 以及 10 GT/s 速率 USB 总线的 PIPE 实现,可以从表 3-3 选择一组时钟频率和数据位宽的方案。

表 3-3 USB 各速率模式下,可选的时钟频率与数据位宽组合

一组兼容 PIPE 协议的 MAC 和 PHY 之间的接口,仅需为每种 USB 速率支持一种实现方案即可。

3.3 SATA 配置

翻译暂略

3.4 其他规则

注意:当 MAC 实现了 TxDataValid 信号,而当前模式无需 TxDataValid 信号来指示有效数据时,MAC 需要始终保持 TxDataValid 高电平有效。

同样地,当 PHY 实现了 RxDataValid 信号,而当前模式无需 RxDataValid 信号来指示有效数据时,MAC 需要始终保持 RxDataValid 高电平有效。

可能有一些 PIPE 实现方案会支持上述表格中提到的多项配置方案。以下是关于支持多方案实现的一些规则。

如果 PHY 支持同一速率下的多种数据位宽和时钟频率配置方案,那么 PHY 也必须实现数据位宽(Width)和 PCLK 频率(rate)两项 PIPE 接口控制信号,用于位宽和速率的选择。

如果 PHY 支持 PCI Express 模式或者 SATA 模式或者 USB 模式中的多种数据速率,那么 PHY 需要支持所有其所支持的速率下,基于该固定 PCLK 频率的配置,或者所有速率下基于该固定数据位宽的配置。

译注:比如 PHY 支持 PCIe 2.5/5/8 GT/s 速率,如果其实现了 250 MHz@32bit(8GT/s),那么 PHY 也需要支持 250 MHz@16bit(5GT/s)以及 250 MHz@8bit(2.5GT/s),即所有的 250MHz 方案。

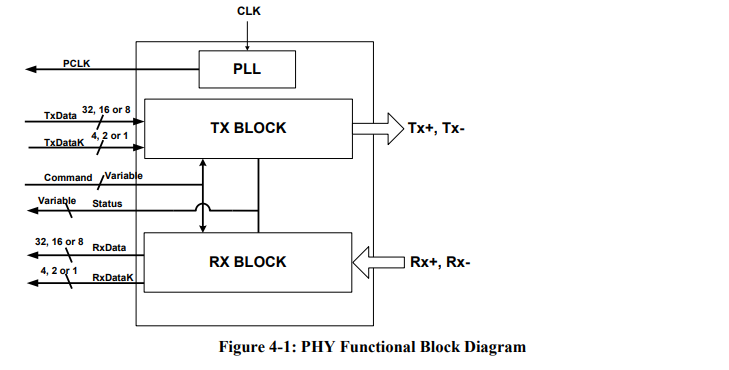

4 PCI Express and USB PHY Functionality

图 4-1 展示了 PHY 的功能结构图。功能结构图的主要目的不是为了定义 PHY 内部的设计细节,主要是为了清晰地表现 PIPE 信号的分组,可以分为时钟、发送接收数据、命令、状态以及收发串行信号。

图 4-1 PHY 功能结构示意图

本章的后几节为图 4-1 中各个子模块提供了更详细的描述。这些子模块代表了 PHY 需要实现的各功能。描述和图表只是描述了通用的结构和行为级的特性,具体功能结构以实现为准。

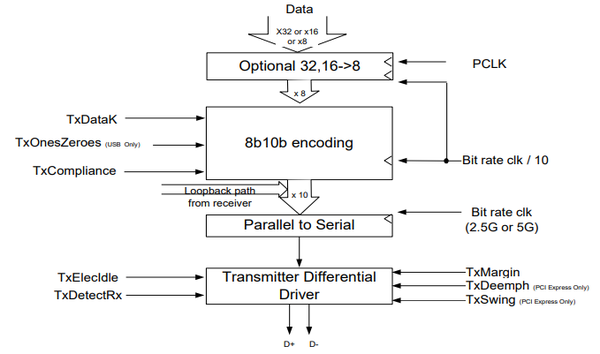

4.1 Transmitter Block Diagram (2.5 and 5.0 GT/s)

图 4-2 发送模块原理图

4.2 Transmitter Block Diagram (8.0/10 GT/s)

图 4-3 发送模块原理图 (8.0/10 GT/s)

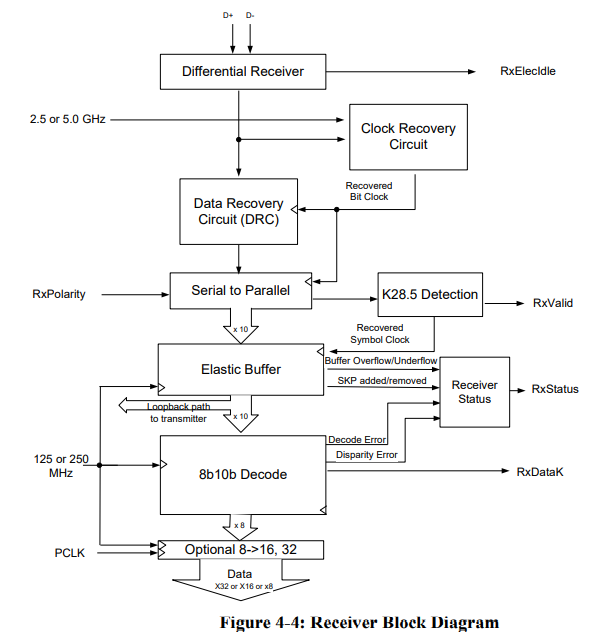

4.3 Receiver Block Diagram (2.5 and 5.0 GT/s)

图 4-4 接收模块原理图

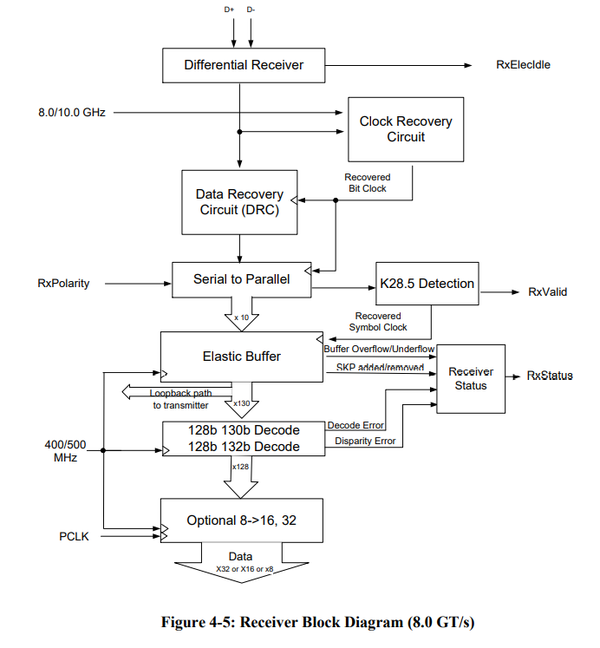

4.4 Receiver Block Diagram (8.0/10.0 GT/s)

图 4-5 发送模块原理图 (8.0/10 GT/s)

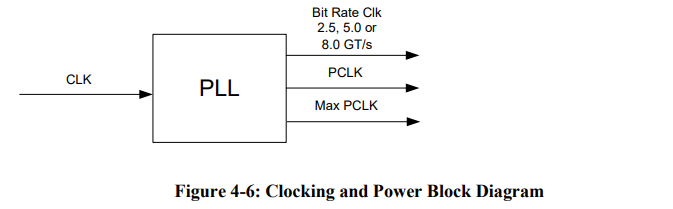

4.5 Clocking

图 4-6 时钟与电源结构原理图

原文: Mindshare

译者: Michael ZZY

校对: LJGibbs

文章来源:https://zhuanlan.zhihu.com/p/512366155

《PCI Express Technology 3.0》翻译系列

- PHY Interface 协议翻译: 2 Introduction

- PCI Express Technology 3.0 Chapter 6 流量控制 5-7 节

- PCI Express Technology 3.0:Chapter 6 流量控制 1-4 节

- 《PCI Express Technology 3.0 》Chapter 5 第3 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3 节(完)

- PCI Express Technology 3.0:PCIe配置概述 3.1-3.7 节

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。