之前介绍过一个细思极恐的事情,ISO 26262从业人员一声一声FMEDA、FMEDA叫的那么亲近,而ISO 26262通篇却没提FMEDA一下,想想都可怕。不过FMEDA作为计算单点故障,潜伏故障诊断覆盖率的技术,该用还是要用的。

芯片的失效模式不像电阻电容的失效模式那样直观,有必要单独拎出来说说。

ISO 26262 2011版没有对芯片的失效做过多的描述,为了填补这一空白,ISO 26262 2018版专门为半导体准备了一章part11,其中涵盖IP核、芯片基础失效率、芯片DFA分析、芯片级别故障注入测试、数字器件、模拟混合器件、可编程逻辑器件、多核技术等等,内容极其丰富。

言归正传。

经常问不同公司的功能安全从业人员,你们的FMEDA中芯片的失效精确到哪个层级了,回答各个层级的都有。

那么ISO 26262是怎么建议的呢?

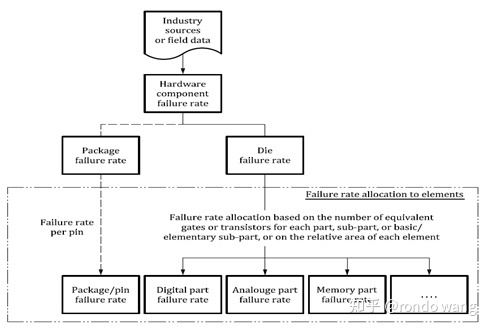

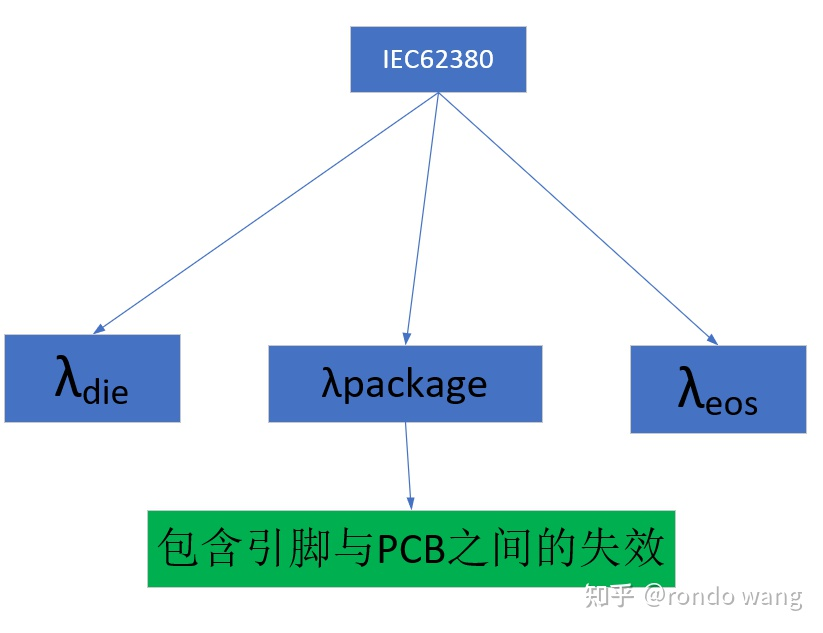

请看下图的芯片失效分布框图,一个芯片的失效分为package/pin失效和die失效,package/pin失效说白了就是芯片的PIN脚连接失效,die失效就是裸片失效,die失效继续分为数字部分失效、模拟部分失效、存储单元失效、时钟单元失效、逻辑单元失效等等,关于die失效的具体分布芯片厂商的芯片FMEDA会进一步提供。

芯片失效率分布

着重强调一下package失效,package失效包含2部分,一部分是芯片PIN脚在芯片自身层面与die的连接失效,另外一部分是PIN脚与PCB板之间的失效,这两种失效都要考虑。

关于失效率怎么计算?

芯片厂商一般会基于SN29500或者 IEC62380提供一系列温度下的芯片基础失效率,有经验的芯片厂商会同时提供基于SN29600, IEC62380, HTOL加速老化测试JESD85A(基于一定的置信水平)等失效率数据,这是为了满足不同客户的不同口味。

然而不幸的是这些温度可能会与系统的mission profile对应不上。

这时候需要根据SN29500或者IEC62380的失效率预估公式反推出目标温度下的失效率。

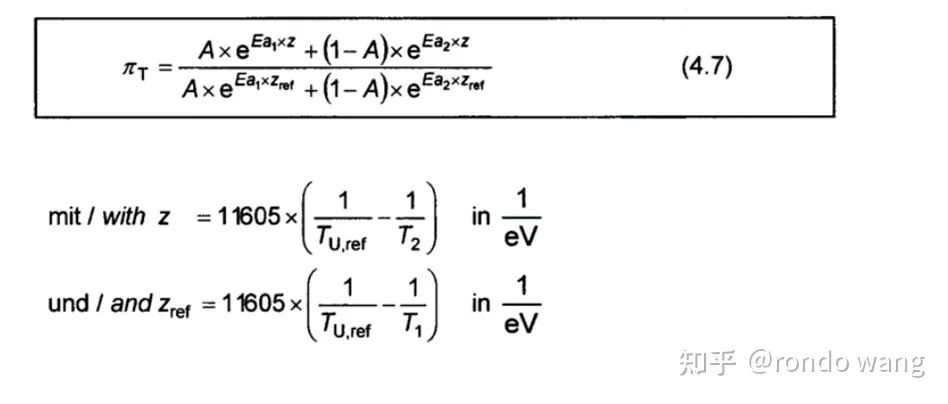

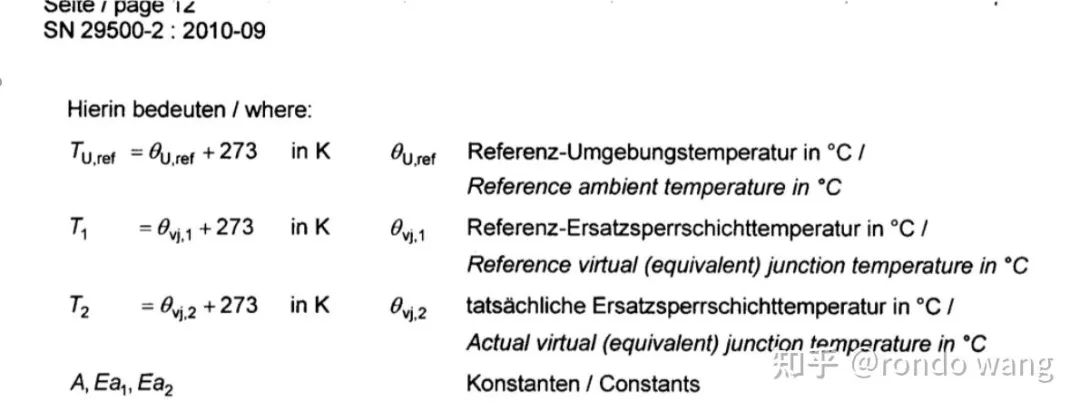

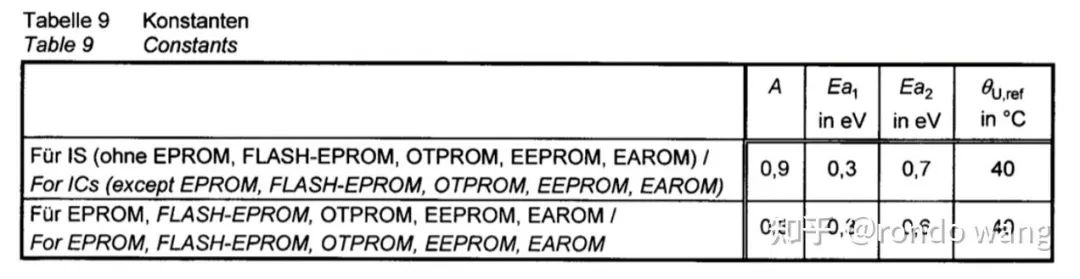

SN29500计算芯片失效率公式

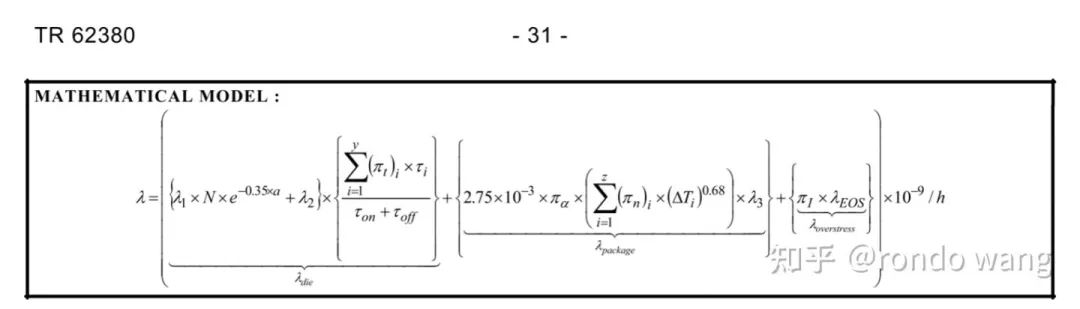

IEC62380计算芯片失效率公式

反推的好处是不需要了解芯片内部有多少门电路,是CMOS还是Bipolar或者其他类型的。

笔者专门做了一个Excel表格来进行失效率的反推。

需要特别注意的是,SN29500和IEC62380计算出来的失效率包含的内容不一样。

区别如下:

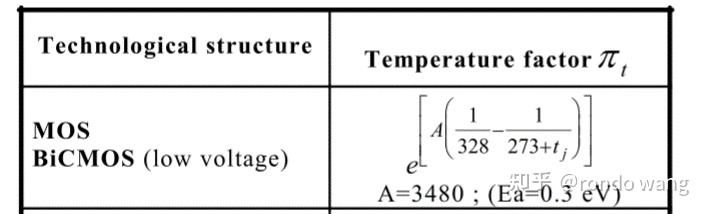

SN 29500算出来失效率是一个总体,没有分成die和package失效,并且不包含引脚与PCB之间的失效。

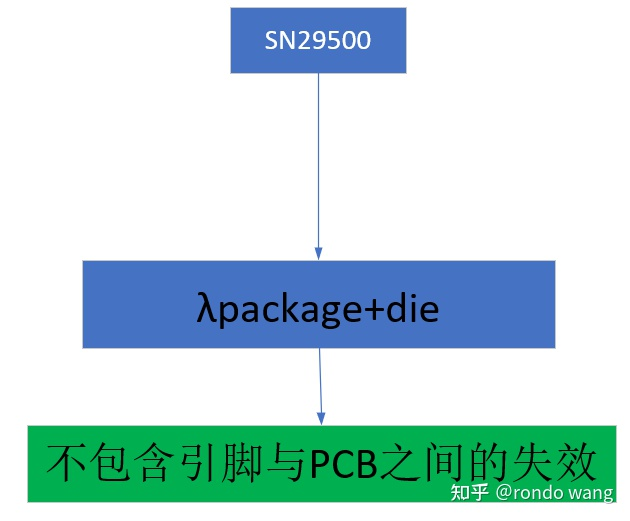

IEC 62380算出来的失效率可以直接拆分成die,package的失效率,并且package那一部分失效率已经包含了引脚与PCB之间的失效率。

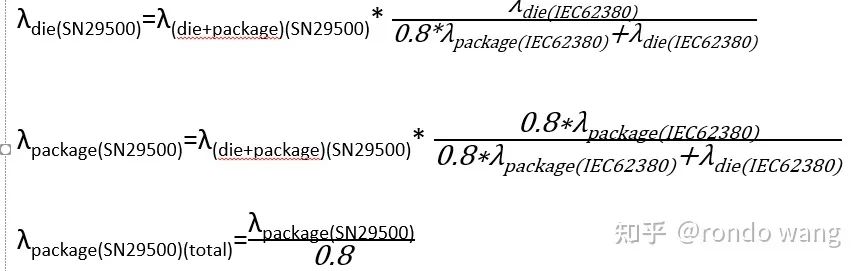

那么如果一个项目的FMEDA是基于SN29500做的,那么怎么把用SN29500得到的失效率分成λdie+λpackage呢?

首先提一点:基于IEC 62380得到的package的失效率其中大约80%是芯片内部的裸片到引脚的连接失效,大约20%的失效是芯片引脚与PCB之间的连接失效。

分解的原则就是按照其他失效率来源的die和package的失效占比来分解SN29500。

基于IEC62380分解的具体公式如下。

最后再根据IEC61709, 分配一下Package的失效模式:5% Short to Vcc, 5% Short to Gnd, 90% Open。

保守一点,再增加5%的芯片相邻引脚的短路失效。

至此,FMEDA中如何考虑芯片的失效完成,精确到芯片引脚失效,无懈可击。

这么细的FMEDA估计客户或者功能安全评估人员也不会看,但请记住做到这里会很踏实,不怕别人的challenge。

作者:rondo wang

来源:汽车电子与软件

微信公众号:

推荐阅读:

更多汽车电子干货请关注汽车电子与软件专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。