在ARM架构最开始开发出来的时候,处理器的时钟速度和内存的访问速度差不多。如今处理器内核越来越复杂,时钟频率提高了好几个数量级。然而,处理器内核外部总线和存储器的频率并没有同步得到提升。

虽然我们可以集成片上的SRAM以实现和处理器速度相同的内存访问,但与DRAM 相比,SRAM 太太贵了。

简单来说,目前的处理器设计存在这样的事实需要接受:外部处理器的访问速度跟不上处理器内核的速度,需要数十甚至数百个内核周期。

cache结构概述

高速缓存(cache)

高速缓存(cache)是位于内核和主存之间的小而快的memory,用于保存主存中经常被使用到的数据的副本。

对cache的访问比对主存的访问要快得多,每当内核读写特定地址时,首先在cache中查找,即hit-miss check。

cache如何提升性能

如果在cache中找到该地址,就可以使用cache中的数据,而不是对主存进行访问。这样就可以减少对外部存储器的访问,即提高了系统的性能,又降低了系统的功耗。

cache的层次结构

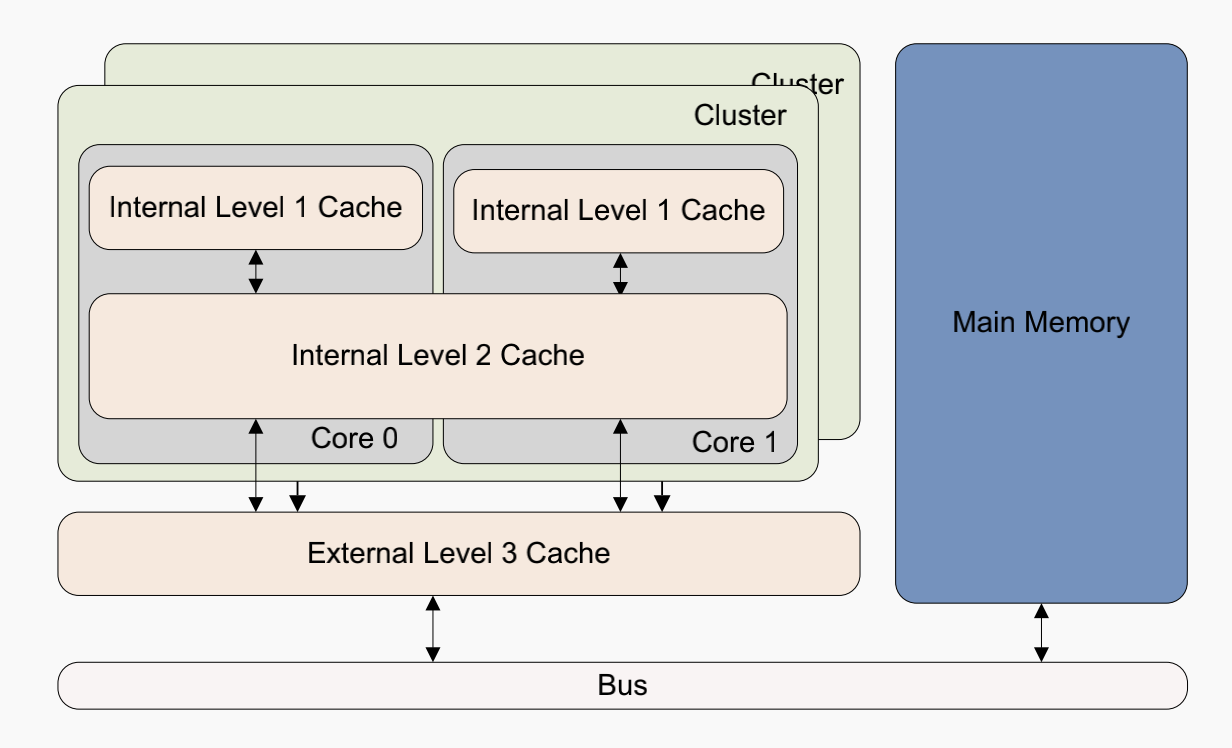

例如ARMv8-A 架构的处理器通常使用两级或多级cache,通常处理器的每个内核都有L1 指令cache和数据cache,以及更大的L2 cache,在同一个cluster中的多个内核之间共享,同时可以保存指令和数据。此外,还可以有一个外部L3 cache,在cluster之间共享。至于这个cluster如何定义要视具体情况而定。

cache的初始访问并不比正常内存访问速度快,性能的提升来自于对该缓存数据的后续hit访问。

Cache 只保存主存的一个子集,所以需要一种方法来快速确定你要查找的地址是否在cache中。另外不同内部具有不同的属性,例如外设通常是non-cacheable必须要在memory系统中使用页表等方式区分。

cache的一致性问题(coherency)

有时cache中的数据和主存中的数据可能不一样,这是因为处理器可能更新cache中数据,但是没有及时写回(write back)到主存中。或者某个内核修改了主存而导致另外的核心中cache数据副本无效。

一些cache相关的术语

冯-诺依曼架构中,指令cache和数据cache是同一个,在优化后的哈弗架构中使用独立的指令cache(I-cache)和数据cache(D-cache),即可以同时访问指令和数据。

在ARMv8处理器中,L1 cache区分指令cache和数据cache,但是L2 cache还是统一的,即折中冯诺依曼架构和哈弗架构。

cache需要保存地址、数据和一些状态信息。

以下是一些cache中经常会用到的术语。

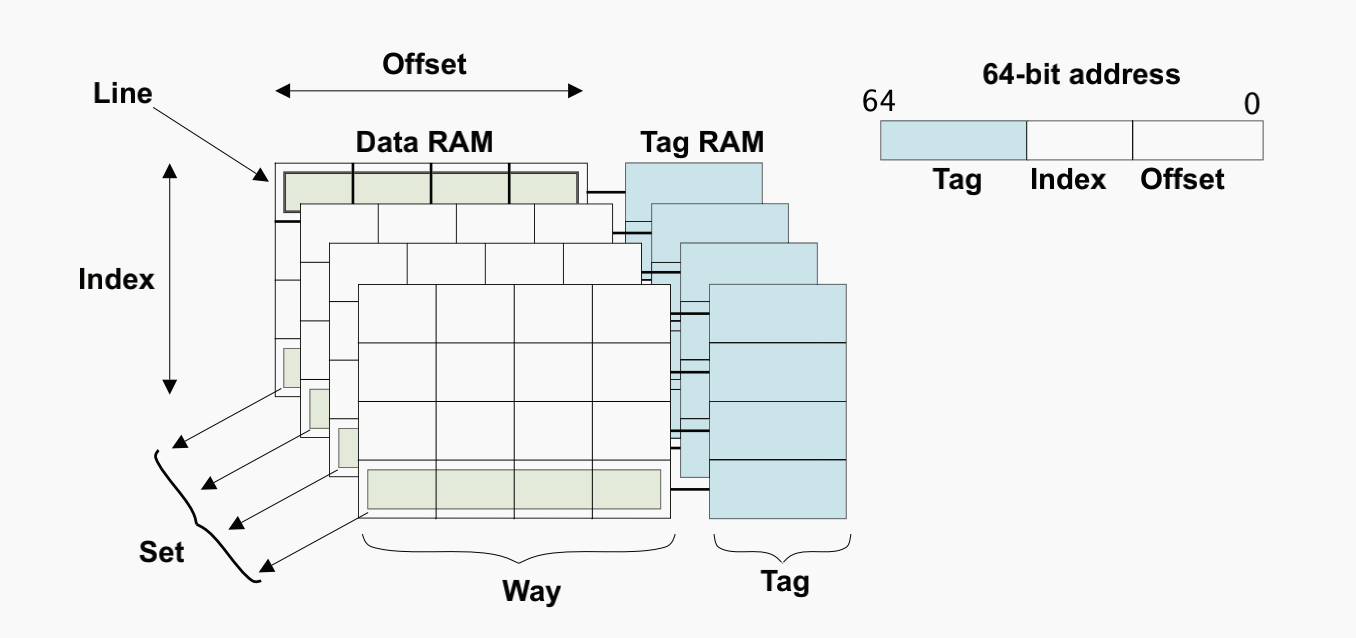

- tag是内存地址的高位部分,存储在cache中用于标识相应的数据。一般来说cache的大小指的是所保存的数据规模,并不包括其中需要储存tag的物理空间。

- 很多时候并不是一个tag对应一个数据,而是对应一组数据,这一组数据块称为cache line,即cache读写的最小的粒度。

cacheline是主存的连续空间数据。 - 当某个cacheline包含有效的数据时,称为valid状态位,否则称为invalid状态。每一个cacheline都会有多个状态位。除了前面提到的valid/invalid,还有dirty状态位,表明cache中的数据是否与主存中的数据相同,以决定是否更新主存(多个dirty位可以更细粒度地表示cacheline中每个数据的状态)。

- index是内存地址的一部分,以决定在哪些cacheline中搜索tag。

way是将cache进行划分成几个相同大小的部分,每几个way对应一个相同的index(set)。

- set就是由一组相同index的cacheline组成。

set、way涉及cache的映射方式,直接相连、组相连和全相连,后面会详细介绍。

- offset,前面我们提到过,一个cache line由多个数据组成,有时候你不需要整个cacheline数据,这个时候可以根据其中的地址低位作为offset进行索引cacheline中各个数据。

作者:验证哥布林

来源:芯片验证工程师

https://mp.weixin.qq.com/s/Lw72N3eirYvZenYE8mgNTw

https://mp.weixin.qq.com/s/b5s0bFdfKNv0Gg8Dt6hJ3w

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。添加极术小姐姐(微信:aijishu20)微信可申请加入IC设计交流群。