今天开始将会通过4~5篇文章介绍FPGA和USB3.0通信的相关知识,这其实是《FPGA和外围接口(继续更新)基于FPGA的网口通信设计》后续。PCIe也在筹备中。

完成后也是《Xilinx 7系列FPGA入门级图像处理-完整版V1》初、中级篇的开始,图像处理部分也会通过摄像头前端算法(主要ISP)和后端算法组成,最后应该会形成一个初级工业UVC摄像头和IPC,平台还没选定(不知道有没有赞助,哈哈),算法基本验证完毕。

整个FPGA和USB3.0通信的知识大约如下图所示:

USB3.0介绍

总线、接口和协议

这里首先提几个概念,大家应该常见到:

- USB3.0协议

- USB3.0接口

- USB3.0总线

是不是很懵逼?

其实理解了这几个概念,对于USB的具体协议就可以有得放矢,不需要看整个复杂又冗长的协议,针对自己的岗位去选择。

总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。接口是一种连接标准,又常常被称之为物理接口。协议就是传输数据的规则。

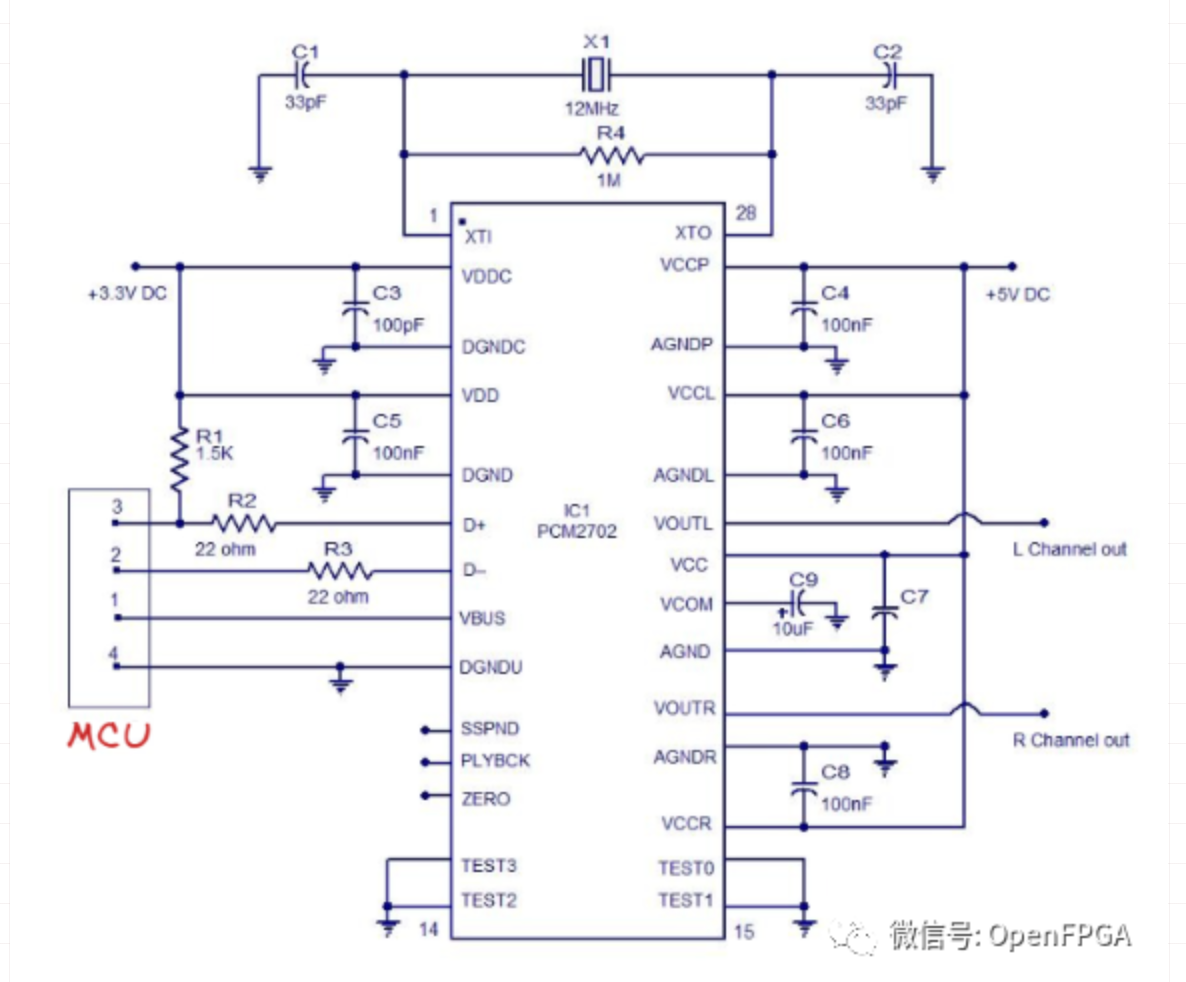

我们通常说的USB,既可以是USB信号,也可以是USB接口、USB总线,还可以是USB协议。之所以这么复杂,主要原因就是每个人对概念认知的差异。举个简单的例子,USB总线说的是一组传输通道,而USB接口是一种连接标准,两者之间的关系就是USB接口的设备都要通过USB总线来进行通信,而USB总线上走的设备并不全是USB接口的,像集成USB声卡,走的就是USB总线,但是没有走USB接口。在这里USB总线提供了一种通道,这个通道上可以有不同的符合这种通道要求的接口设备或信号(USB信号或Audio信号)。

USB外置声卡

USB板载声卡

对于USB声卡,外置声卡时走的就是USB接口,板载声卡时时走的USB总线而不包含USB接口(物理层满足要求即可)。

所以总结一下:

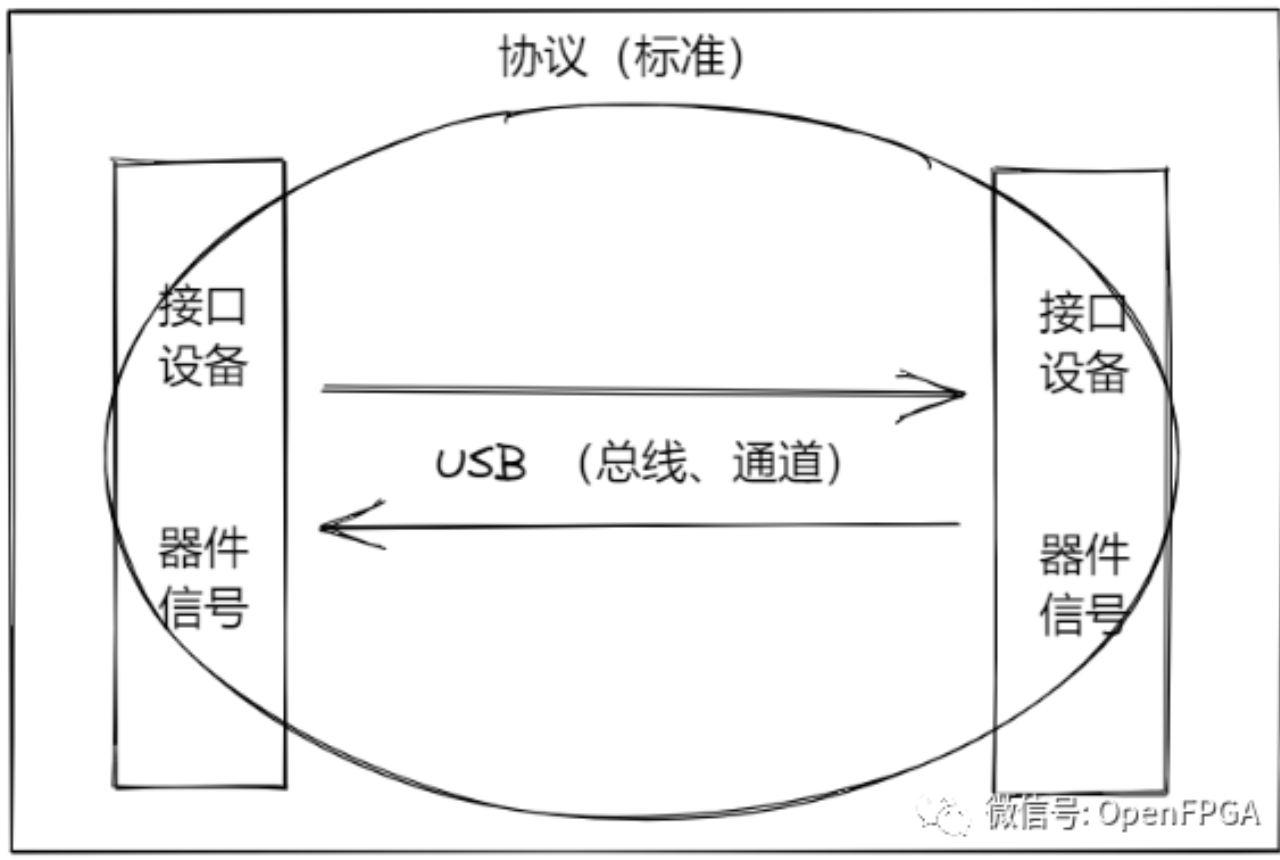

协议即总体框架,定义接口设备、器件及信号、总线及通道之间需要满足的关系,即要实现信号的传输,所有这些组成成员必须通力合作,各自满足协议要求的各种必要条件。

对于USB,下图可以说明这三者关系:

通过上面的分析,后面会在简单介绍USB3.0中规定的几个重要方面。

USB3.0的分层机制

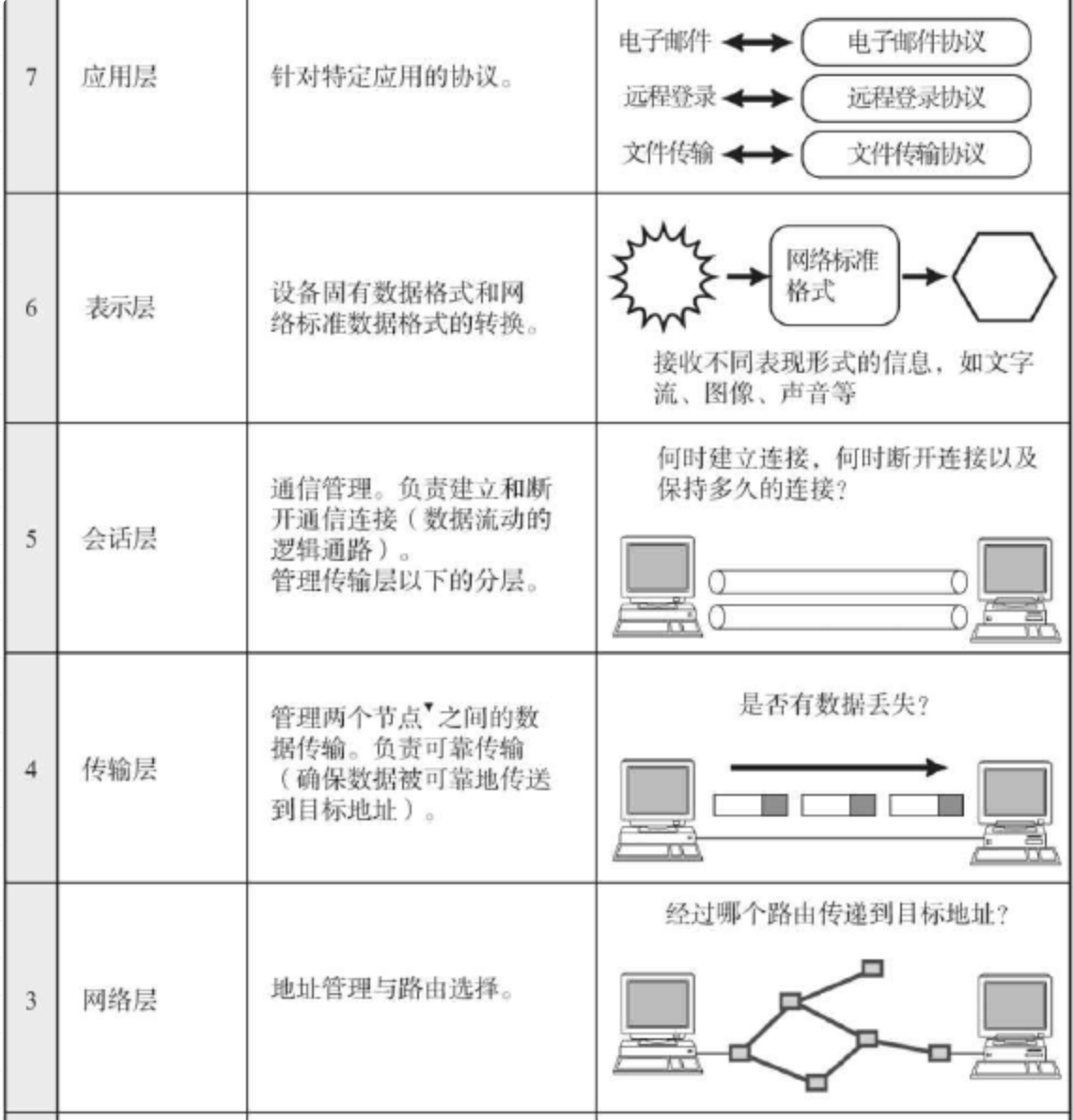

大家都知道PCIe具有三层结构(事务层(Transaction Layer),数据链路层(Data Link Layer)和物理层(Physical Layer)),TCP/IP五层结构(物理层、数据链路层、网络层、传输层、应用层),为什么复杂协议都具有分层结构呢?

这个由来主要来源于OSI五层参考模型(例说七层OSI参考模型)。

即使简单的RS232也是遵守上面的分层结构,只不过RS232只规定了物理层,所以现实中很少有人用分层结构进行分析。

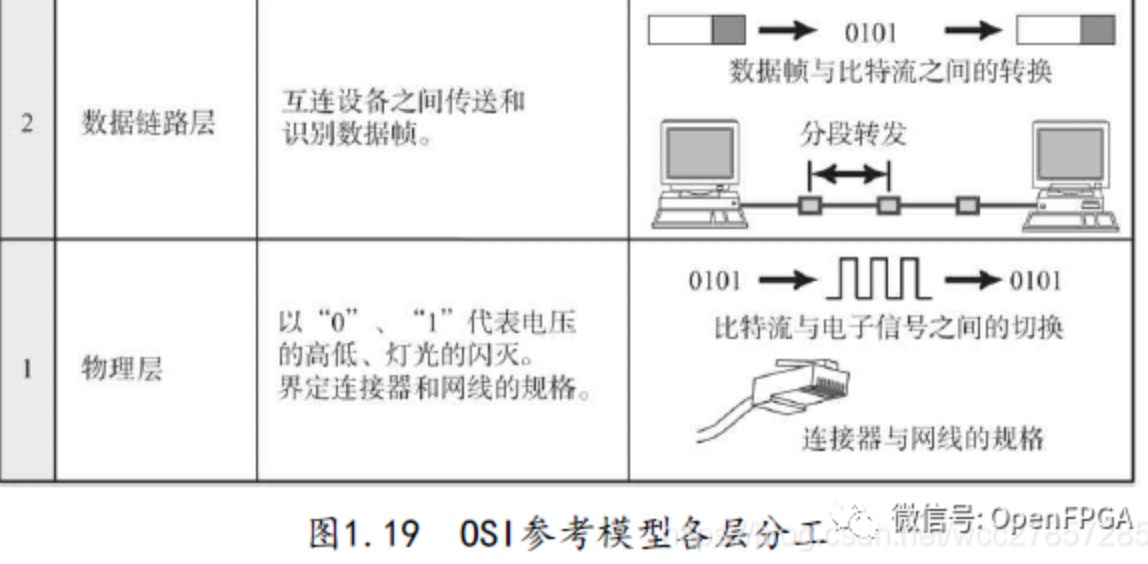

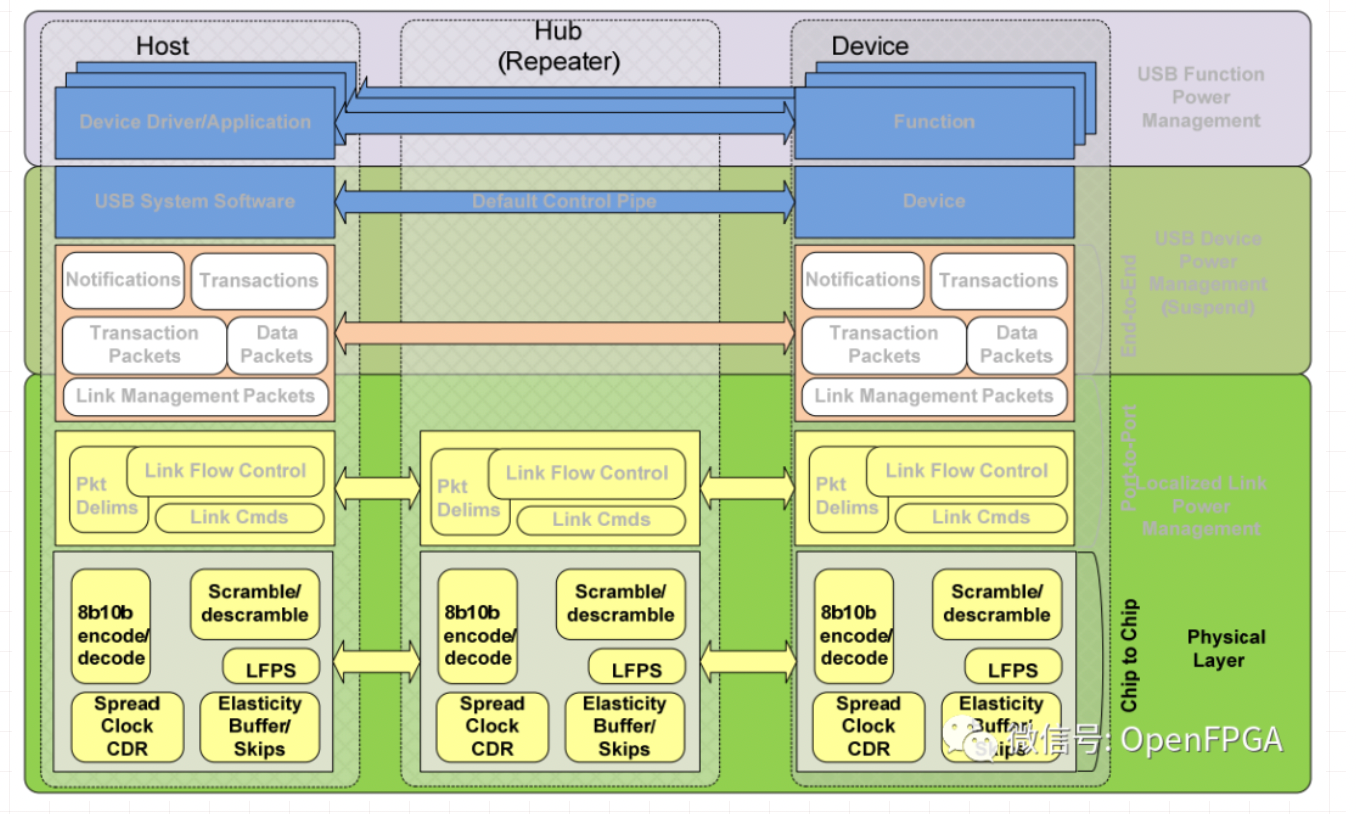

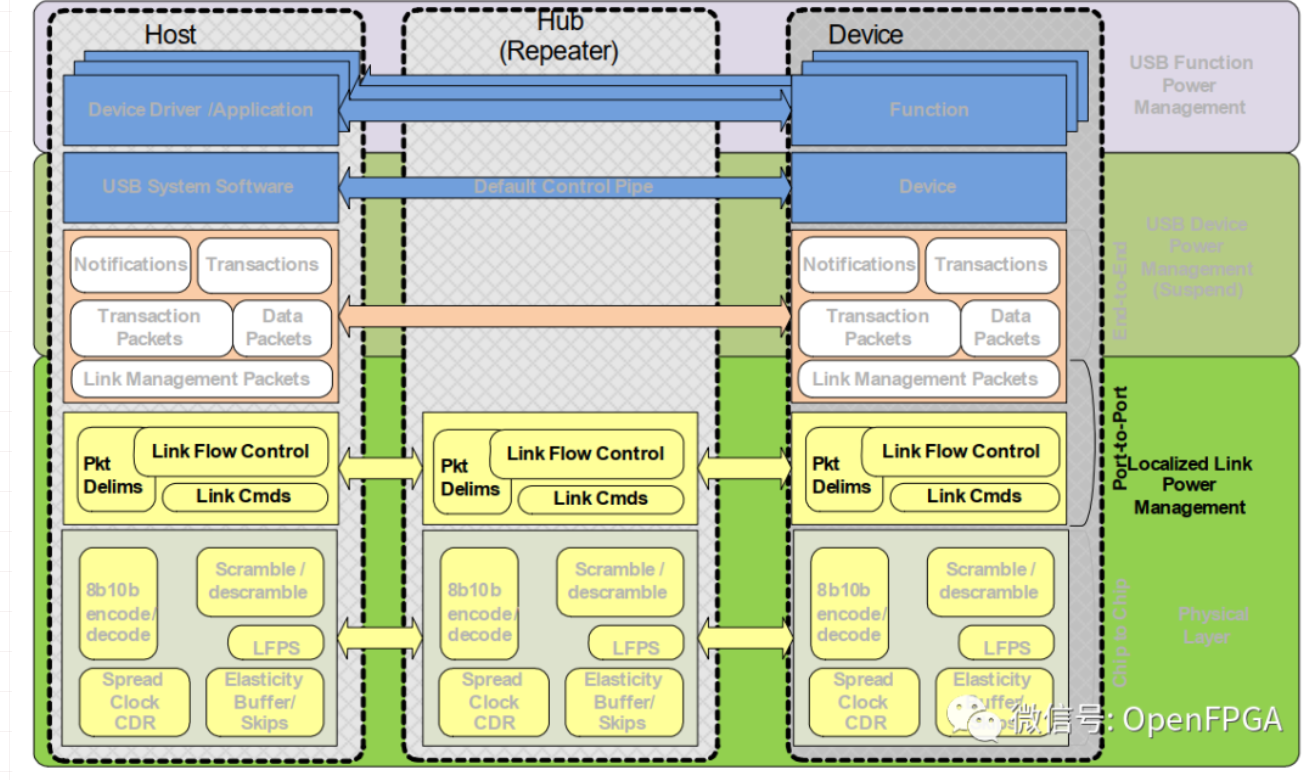

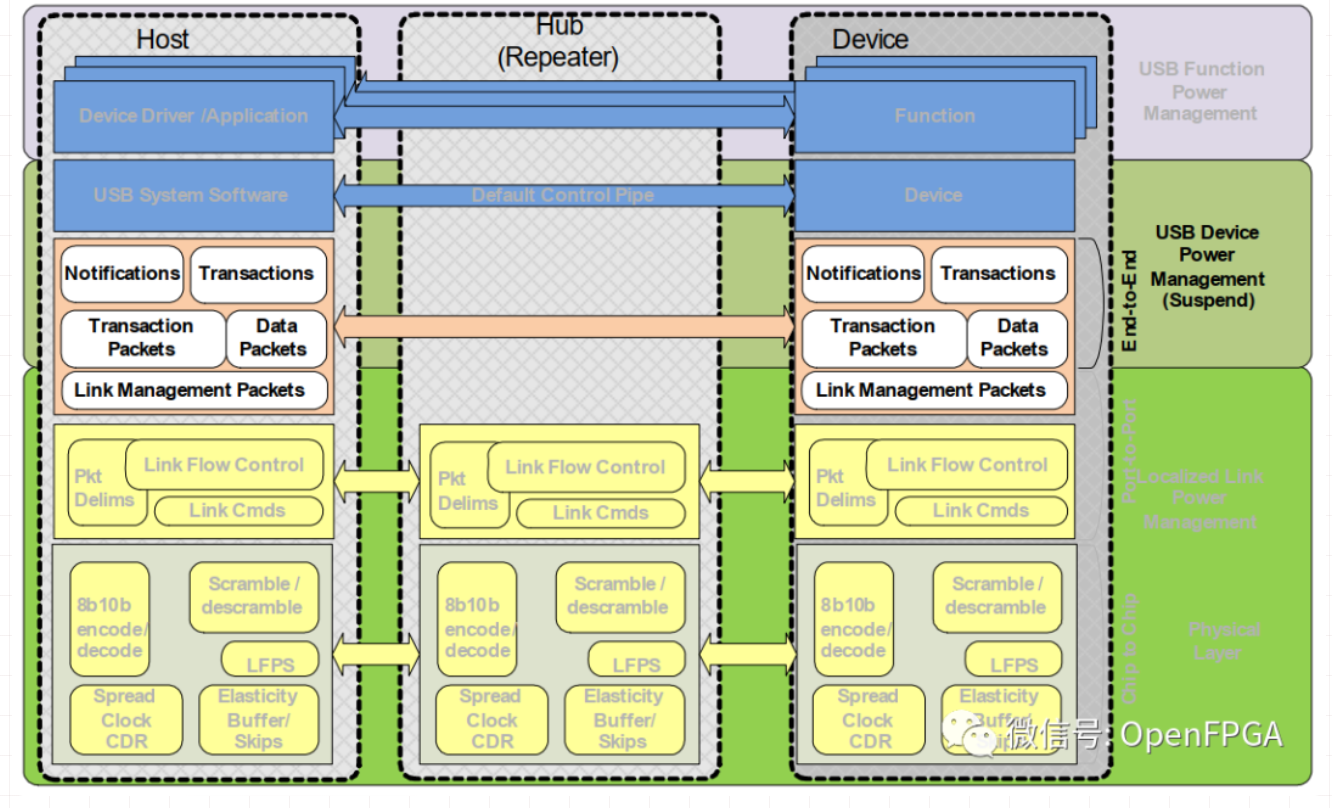

USB3.0的分层机制其实和PCIe类似(协议层(Protocol Layer),链路层(Link Layer)和物理层(Physical Layer)),从某种意义上看,可以把USB3.0看做是PCIe变形版本。下图是分层的通讯结构:

这种分层结构即方便标准化,又方便扩展,所以现今大部分协议都遵循OSI参考模型,希望大家可以理解一下这个模型(推荐的文章中有很多形象的解释)。

以上部分解释包含了个人理解,为了通俗易懂,有些表述不是很准确,希望大家留言交流,下面就很俗套的简单讲解官方的文档了。

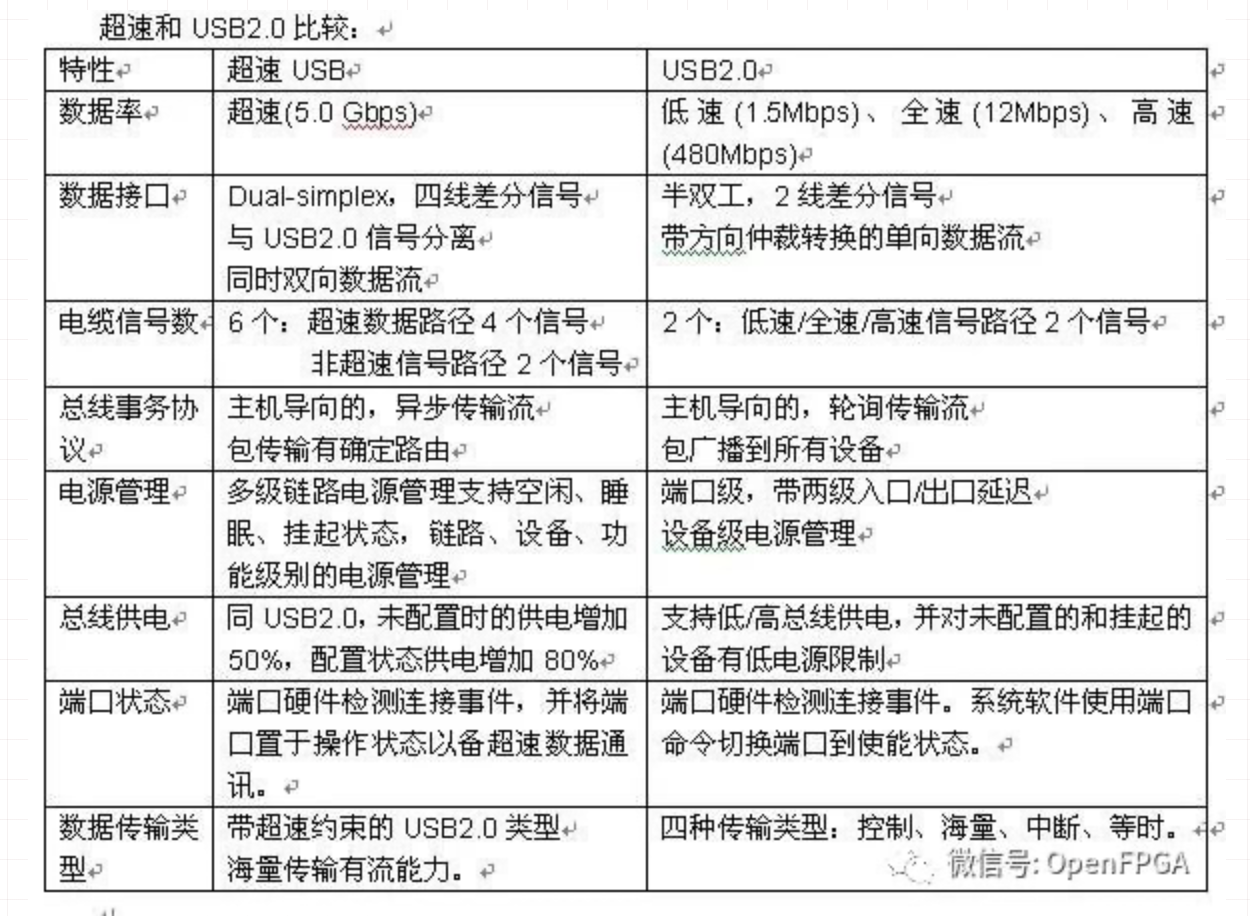

USB3.0 与USB2.0的特性比较

硬件接口

物理层

高亮显示部分:

本层主要定义了高速组件之间互操作性所需的电气层参数。

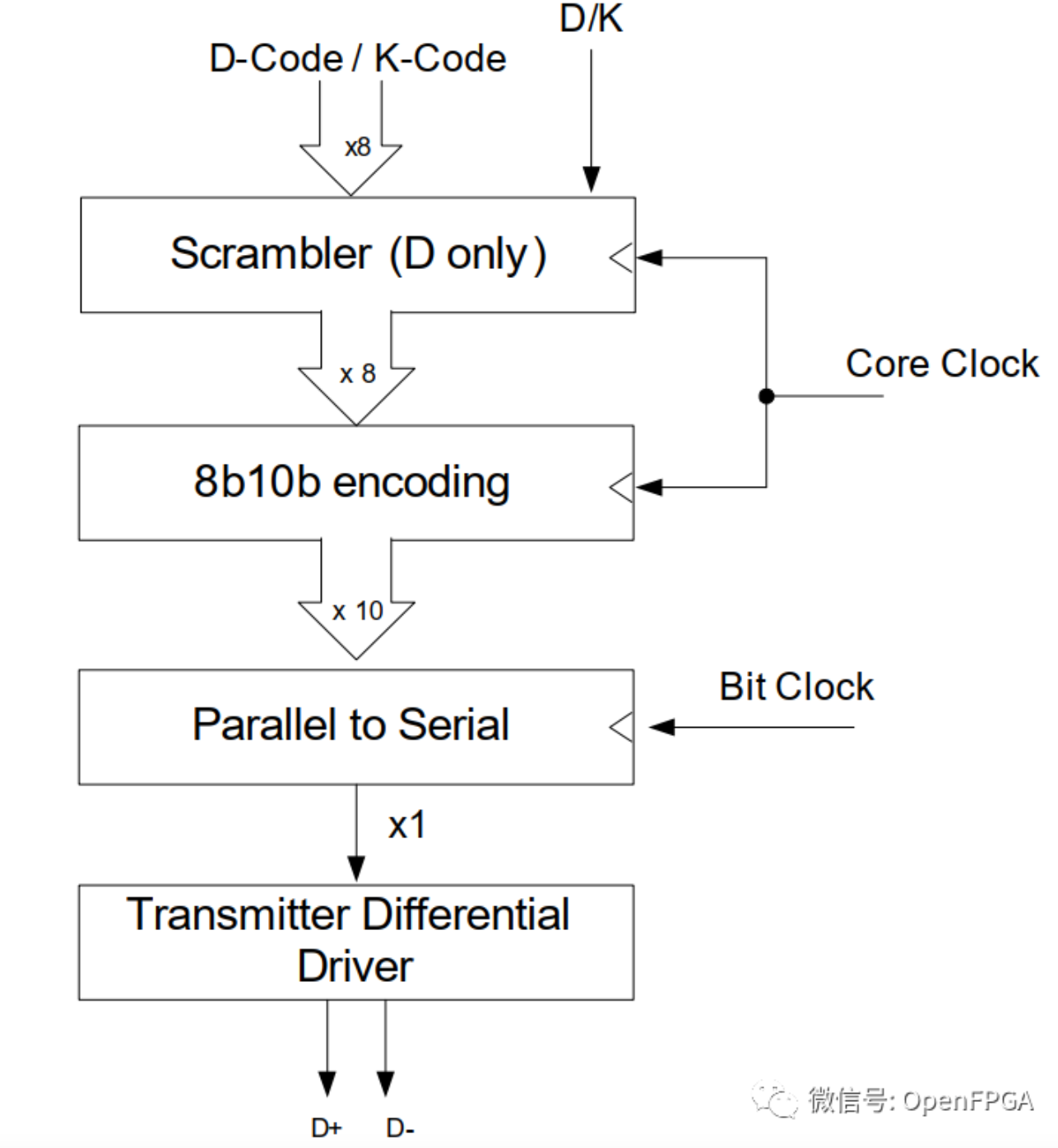

物理层Tx框图

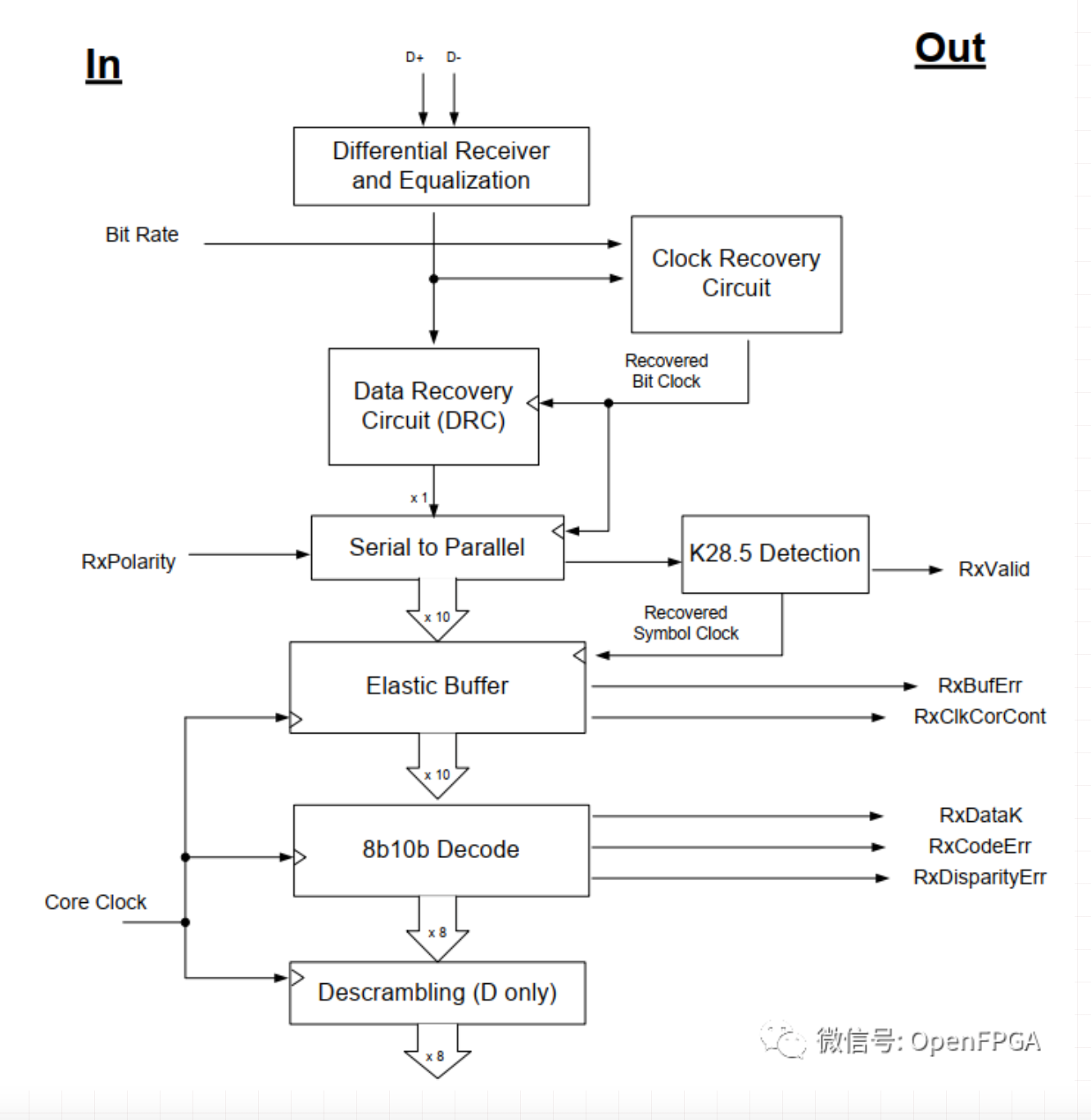

物理层Rx框图

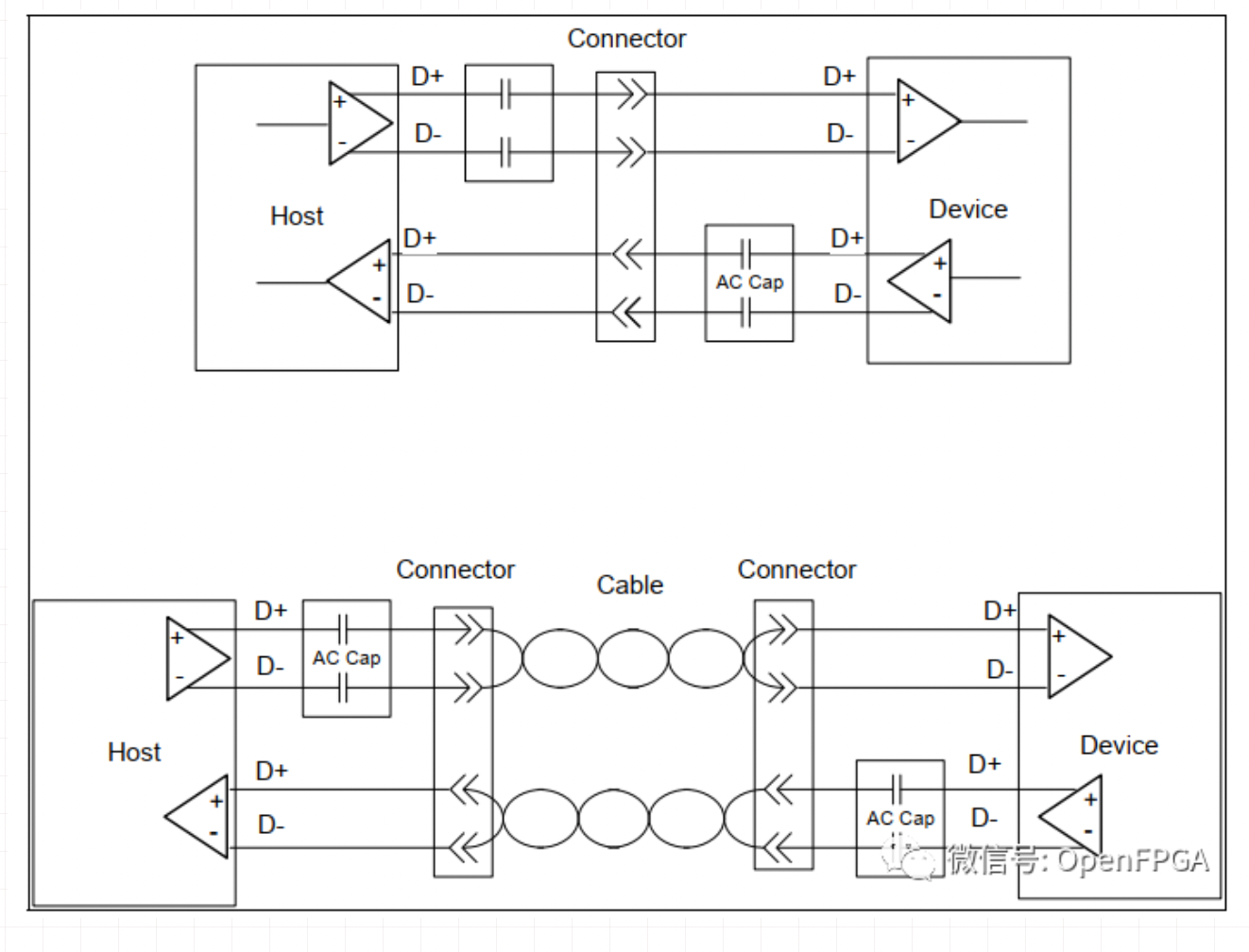

不带电缆(顶部)和带电缆(底部)的通道示意图

USB3.0使用8b/10b传输代码。该传输代码的定义与ANSI X3.230-1994(也称为ANSI INCITS 230-1994)第11条中规定的定义相同。

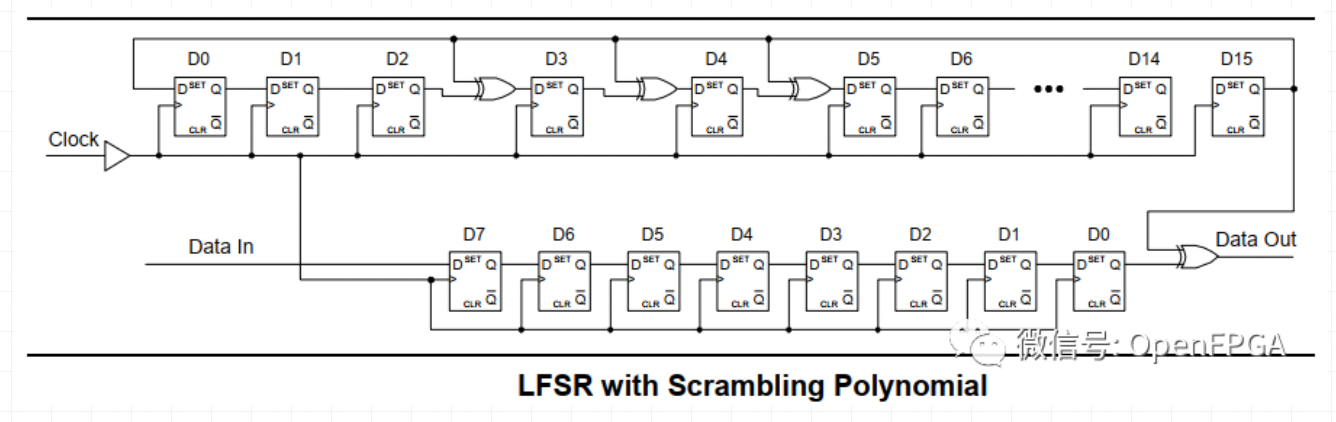

加扰功能使用线性反馈移位寄存器(LFSR)实现。在发送端,加扰应用于8b/10b编码之前的字符。在接收端,对8b/10b解码后的字符应用解扰。无论何时发送或接收COM符号,LFSR都会重置。

以上就是物理层大致的规定,详情请见《USB3.0协议规范(英文完整版)(第六节)》。

Link Layer链路层

高亮显示部分:

Link Layer链路层主要包括:

•数据包帧

•链路命令

•链路管理和流量控制

•链路错误规则/恢复

•重置

•链路状态机描述

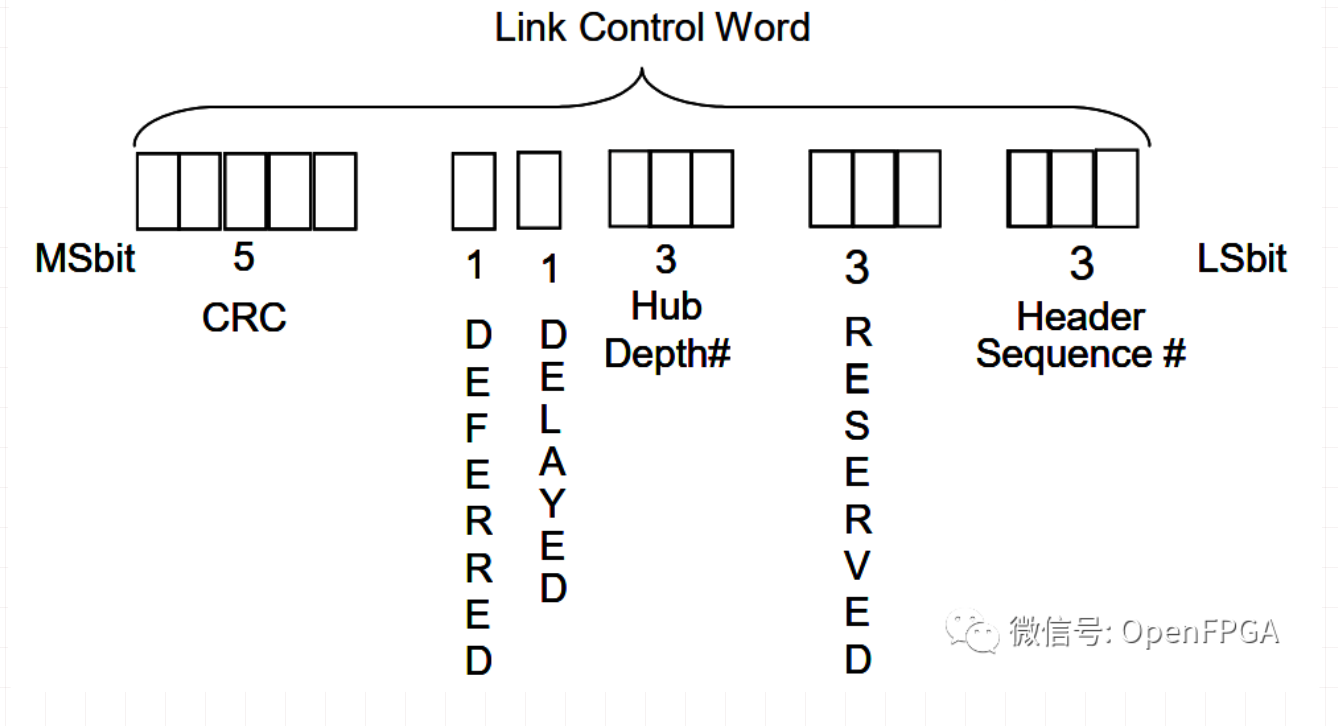

具有帧符号、CRC-16和链路控制字的分组报头

链接控制字

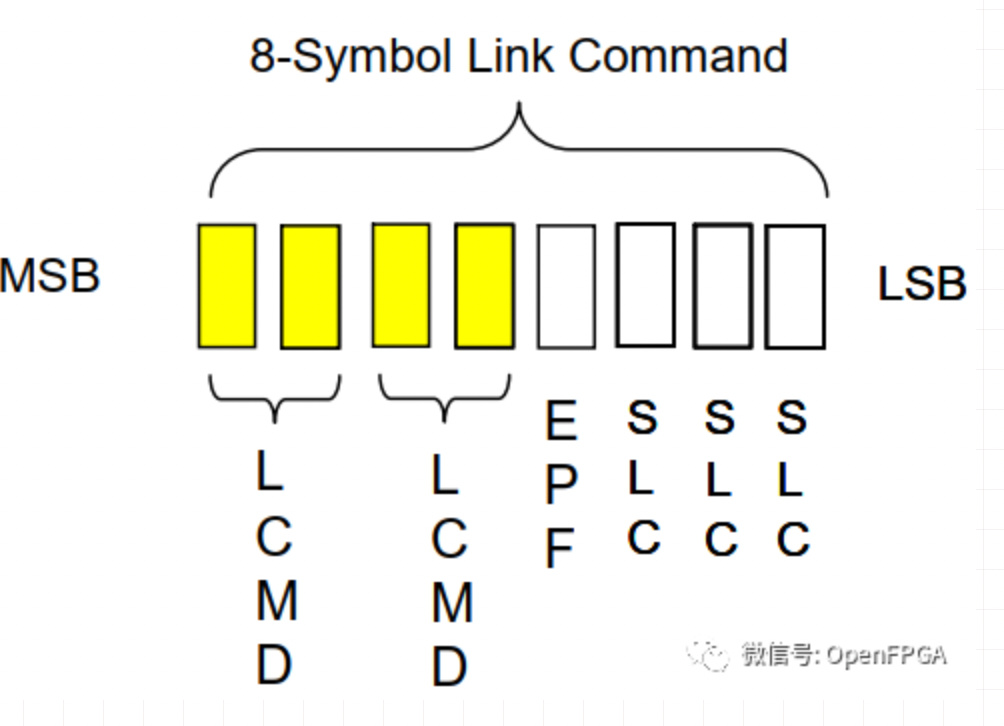

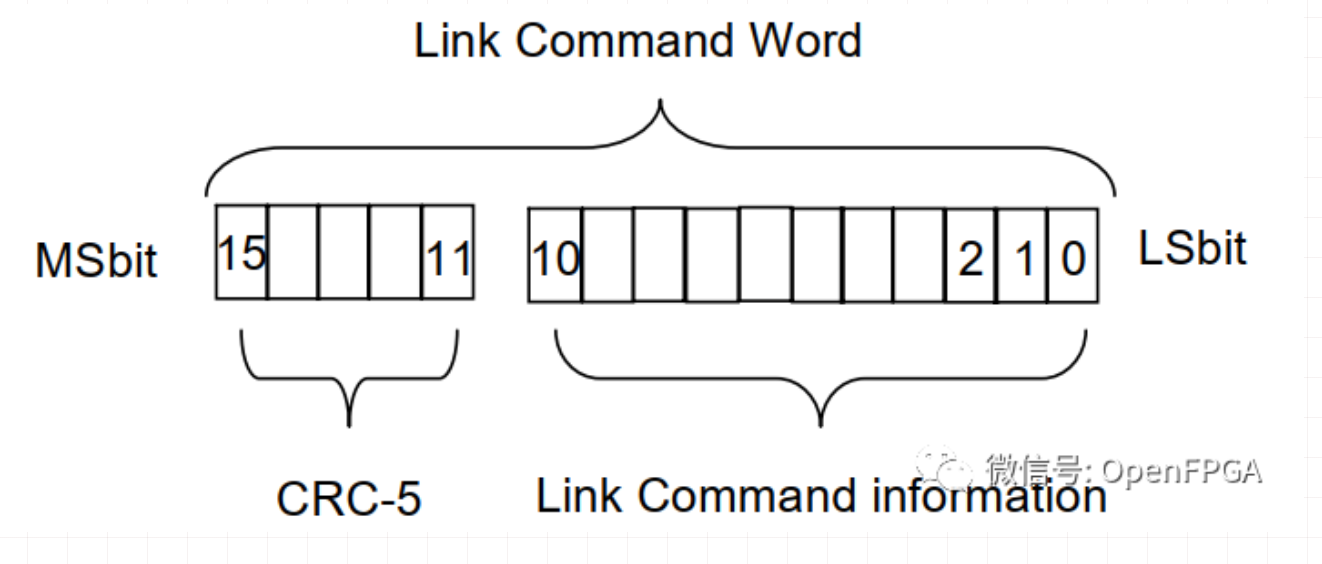

链接命令结构

链接命令字结构

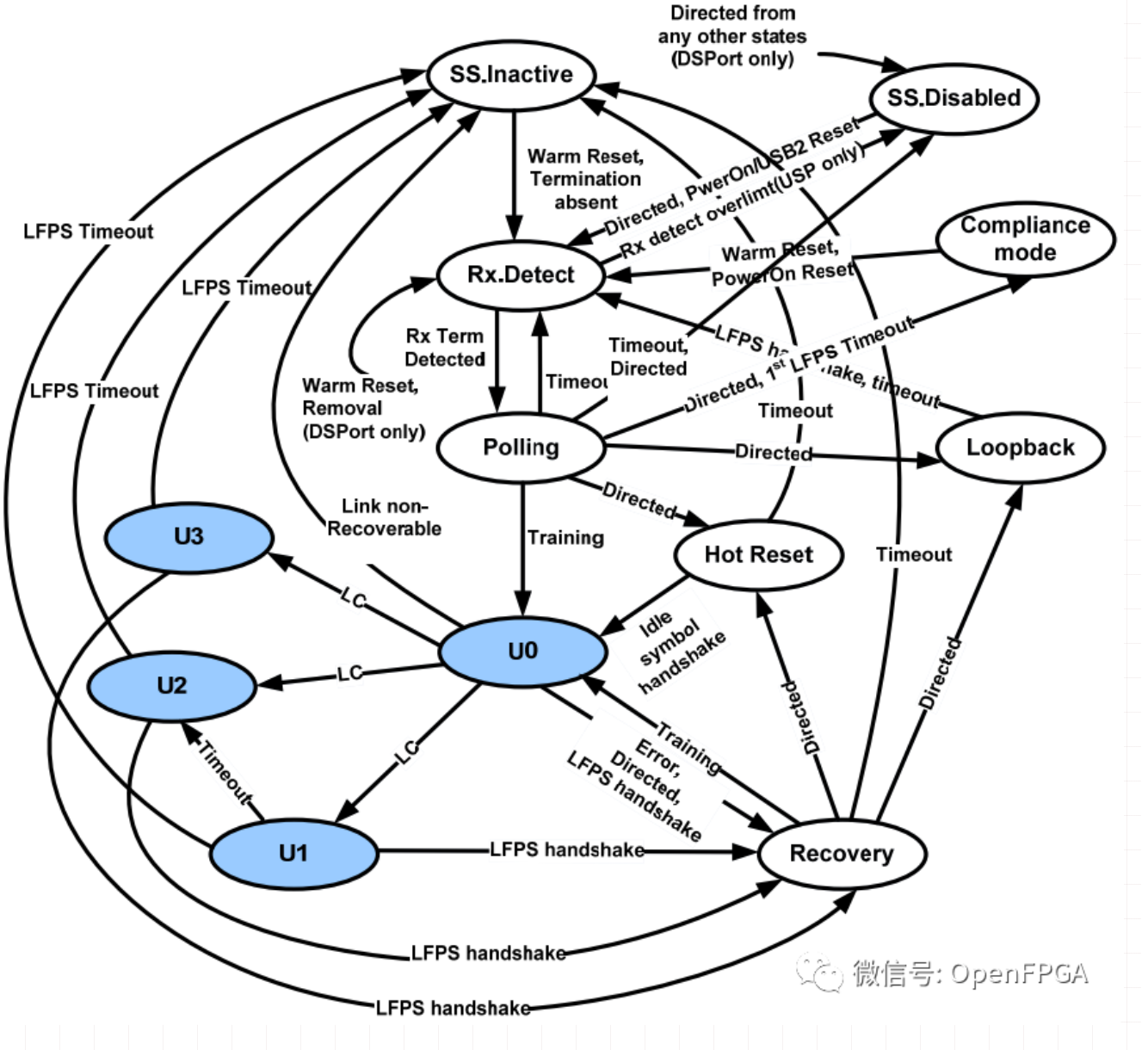

链路训练和状态机的状态图

协议层

高亮显示部分:

协议层主要包括:

•数据包类型

•数据包的格式

•对主机和设备发送的数据包的预期响应

•描述了四种USB 3.0事务类型

•支持批量传输类型的流式传输支持

•设备/主机可能接收/发送的各种响应和数据包的定时参数

整个协议层非常复杂,数据包就差不多十几种类型,所以这里就不过多介绍了。

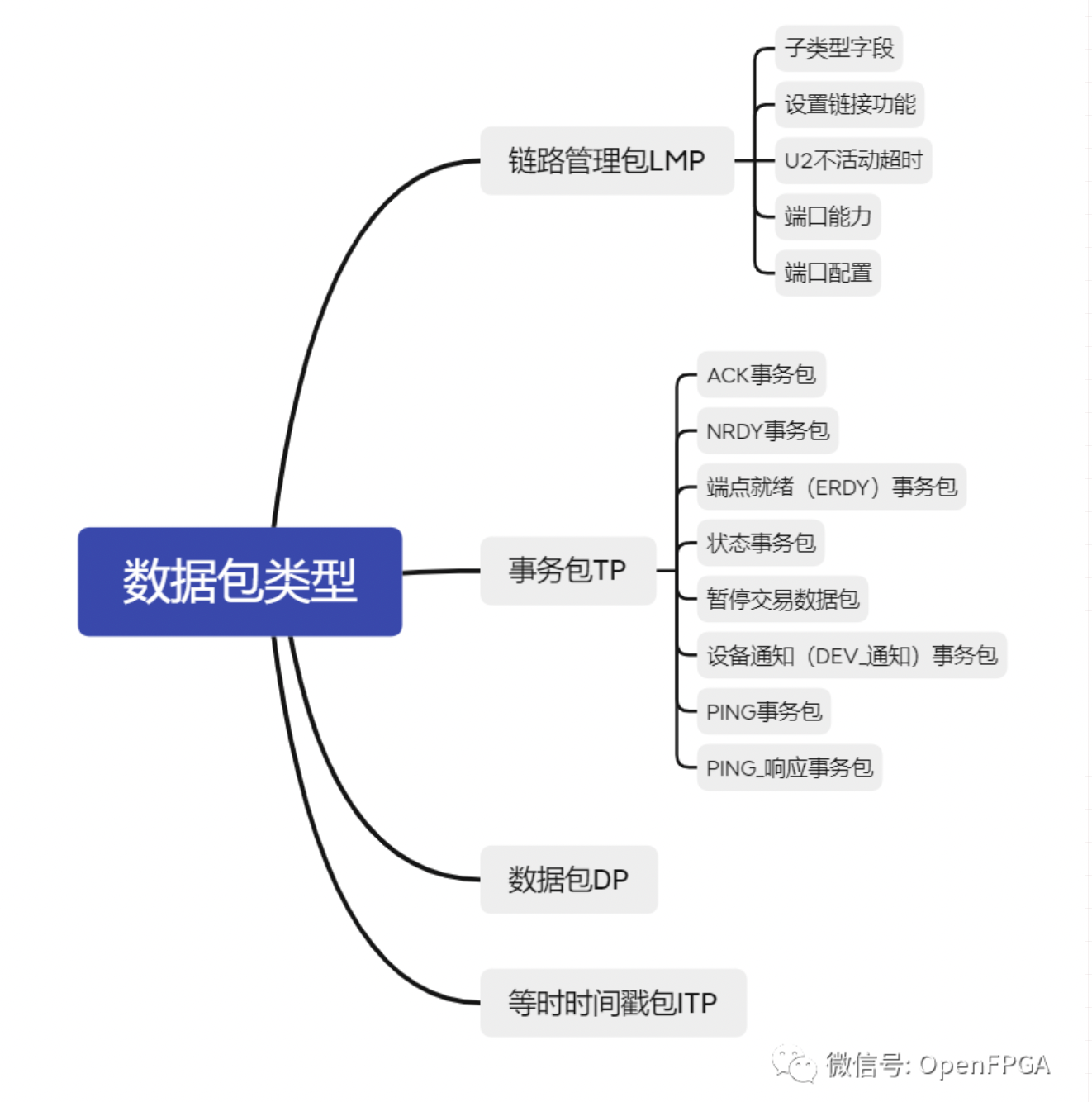

下面的导图可以有助于大家去阅读:

文档资料

和彩云永久链接

链接:https://caiyun.139.com/m/i?1B5C6LLUwJJhx 提取码:oJwK

小程序查看

PS

大家可以思考几个常见的概念:UART、RS232、RS485及I2C、SMBUS、MDIO、IPMB之间的区别和联系,最好结合实际使用情况去理解。

最后,很多人问我怎么实现一个USB IP,这里我只说下我自己的建议,第一USB协议很复杂,实现起来难度很大,2.0是有开源IP的,3.0的目前还没发现。第二商业IP很贵,个人不建议购买。第三USB PHY的价格及应用还是很诱人的,你只需要一个状态机读取FIFO就可以简单和上位机实现通信。以上几点总结起来就是接下来我们会介绍USB PHY而不会过多纠结于协议相关的知识。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。