来源:内容由「网络交换FPGA」编译自「eejournal」,作者:Kevin Morris,谢谢。

在本系列的第1部分中,我们研究了Achronix,Intel和Xilinx的新型高端FPGA系列。我们比较了底层半导体工艺,可编程逻辑LUT架构的类型和数量,DSP /算术资源的类型和数量以及它们在AI推理加速任务中的适用性,声称的TOPS / FLOPS性能能力以及片上互连(例如FPGA路由资源和片上网络(NOC)。从这些比较中可以明显看出,这些供应商提供的每项产品都具有独特而有趣的功能,这些功能将使它们在特定的应用领域脱颖而出。我们也无意中强调了对这种复杂的半导体器件进行有意义的分析有多么困难。

Xilinx,Intel和Achronix这三个供应商都与我们讨论了我们的假设和分析,并提供了对该系列的宝贵见解。

本周,我们将讨论存储器架构、封装内集成架构和高速串行IO能力。在这里,我们将再次看到,这一代FPGA远远超过了它们的前辈,我们将进一步证明这些可能是有史以来最复杂的芯片。我们正处于半导体演进史上一个迷人的时代,摩尔定律即将结束,新一代的人工智能技术和应用需要一种全新的计算方式,而巨大的竞争态势也在为这些惊人的器件打开了巨大的新市场。

FPGA的实际性能与计算资源和内部带宽一样,都取决于内存架构。在今天的计算环境中,数据就是东西--而在计算流中有效地移动、处理和存储这些数据是关键。今天,全球的数据基础设施描绘出一幅壮观的愿景,从充满传感器的小型端点到网络边缘、本地存储和计算,再回到拥有庞大计算和存储资源的云数据中心,然后再通过整个事情再回到边缘。FPGA在这一环中的作用是巨大的--FPGA在存储、网络、内存和计算方面贡献巨大。

ACAP不是FPGA

我们应该指出的是,Xilinx坚持认为他们的Versal ACAP系列器件是一个独立于FPGA的类别--他们将其命名为 "ACAP",意为 "自适应计算加速平台"。根据我们的理解,这一说法的关键在于Versal针对的是不同于传统FPGA的受众---应用开发人员可能不具备FPGA专业知识,他们需要的交互模型并不是从配置FPGA结构的bit流开始。事实上,他们指出,Versal可以在完全不配置FPGA结构的情况下启动和操作。这一点,加上矢量处理引擎和片上网络(NoC)等特性,是他们认为Versal器件是 "ACAP "而不是 "FPGA "的论点的基础。

但是,出于本文的目的,我们将继续针对这些其他非常相似的FPGA系列评估Versal ACAP。我们相信这三种产品将经常争夺相同的插座。此外,我们的读者总是有一大批FPGA设计专家,这些专家可以追溯到2009年之前,当时我们被称为“FPGA Journal”。我们了解Xilinx的市场地位背后的动机。他们想吸引一个新的市场,对于客户,“ FPGA”可能是一个令人生畏或令人困惑的标签。赛灵思针对其“ Zynq”系列设备采取了类似的策略-将其称为“ SoC”而不是“FPGA”。但是,“ ACAP”很难销售,因为SoC类别已经存在,并且具有大量竞争产品。创建一个新的类别是一项艰巨的任务。我们将看看它是否流行起来。

这些竞争产品家族中的每一个在针对他们设想的目标应用程序优化内存体系结构方面都采取了不同而有趣的尝试。与传统的CPU或GPU架构不同,FPGA独特地允许重新配置存储器层次结构以匹配手头的任务。这可能对最终应用程序的吞吐量,延迟和功率效率产生巨大影响。FPGA存储器架构使我们能够划分应用程序,以便每次使用存储器时都可以在局部性/带宽和密度之间取得最佳平衡。

FPGA的存储资源

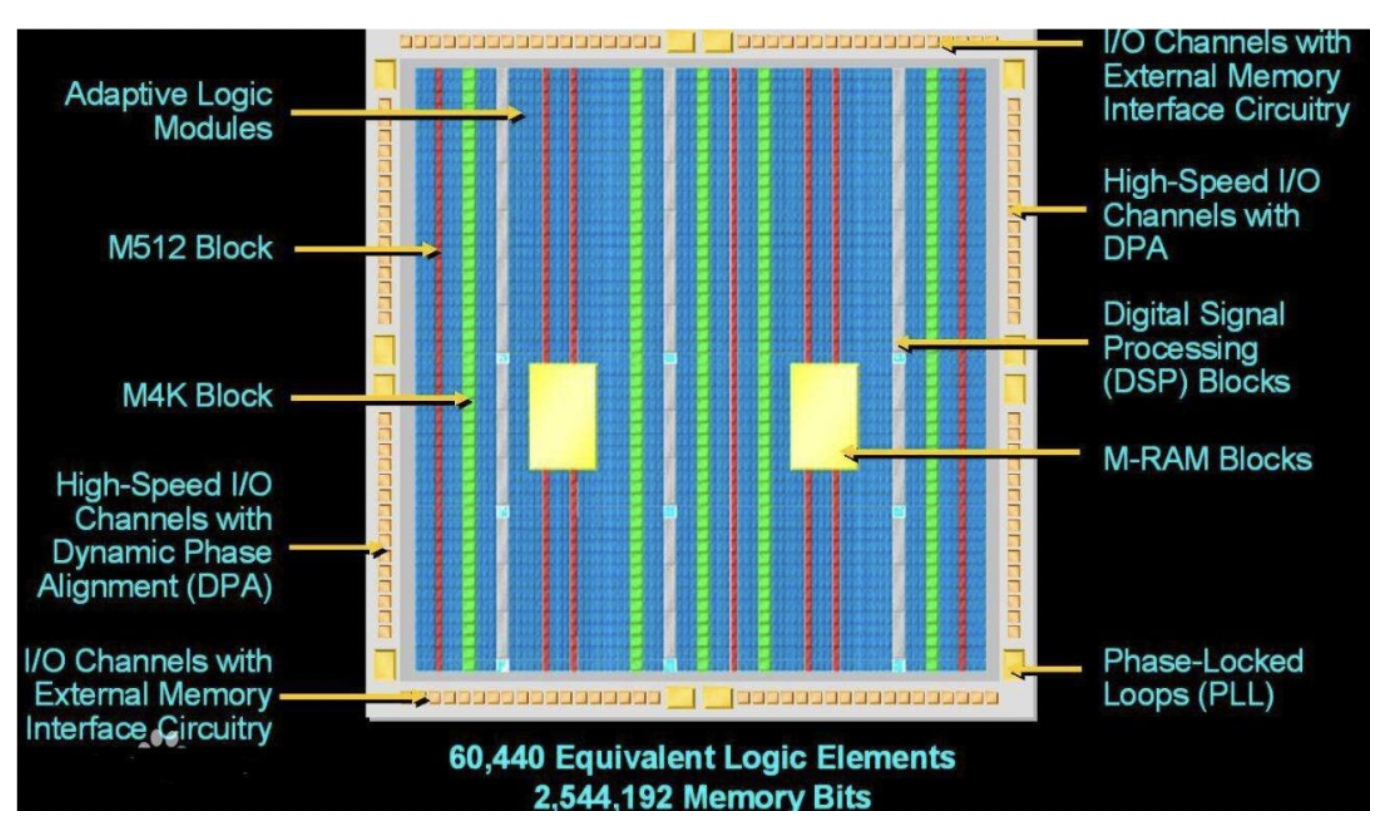

从密度最低但带宽最高的是LUT本身内部的内存资源开始。在那里,逻辑可以直接以硬接线方式访问少量的存储数据,为数据流创造了最有效的路径。所有的FPGA架构都有基于LUT的存储器作为核心特性。LUT存储器的数量与LUT计数大致成正比,这一点我们在上周讨论过。虽然这种存储是超本地存储,并为相关逻辑提供了基本上最佳的带宽,但大多数应用的内存需求远远超过了微薄但宝贵的LUT内存资源。(LUT资源也是另外一种形式的存储资源,在极端情况下也可以作为存储资源来使用。SLICEM的LUT可以被配置为位宽为1bit、深度为64bit的RAM。可参看本公众号之前文章《手把手教你动态编辑Xilinx FPGA内LUT内容》)

在密度上提高一级而在带宽上降低一级,那么,我们就有各种架构可用于FPGA架构中的“块”存储器。顾名思义,块结构是FPGA架构内专用的硬化存储区,需要数据路径来跨越更多FPGA互连。每个供应商都有自己的策略来划分这些片上存储器资源。他们对各种类型的应用程序及其内存需求进行了详尽的建模,权衡了分布和密度之间的折中,并提出了一种分层的方法,使他们觉得最能解决最广泛的问题,尤其是针对主要目标应用程序类型。

从Achronix开始,Speedster 7t提供高达385Mb的嵌入式内存,分为LRAM2k,BRAM72k和MLP模块。英特尔Agilex在三种类型的块式嵌入式存储器(MLAB,M20K块和eSRAM存储器块)之间提供了300 Mb的嵌入式RAM。Xilinx Versal提供块RAM,“ UltraRAM”和Accelerator RAM –在其最大的“ AI Core”设备中,总容量高达294 Mb。这些架构中的每一种都是供应商的最佳选择,它认为在各种目标应用程序中,什么大小的块以及与其他资源的接近程度将提供最佳性能。

FPGA采用多芯片封装技术

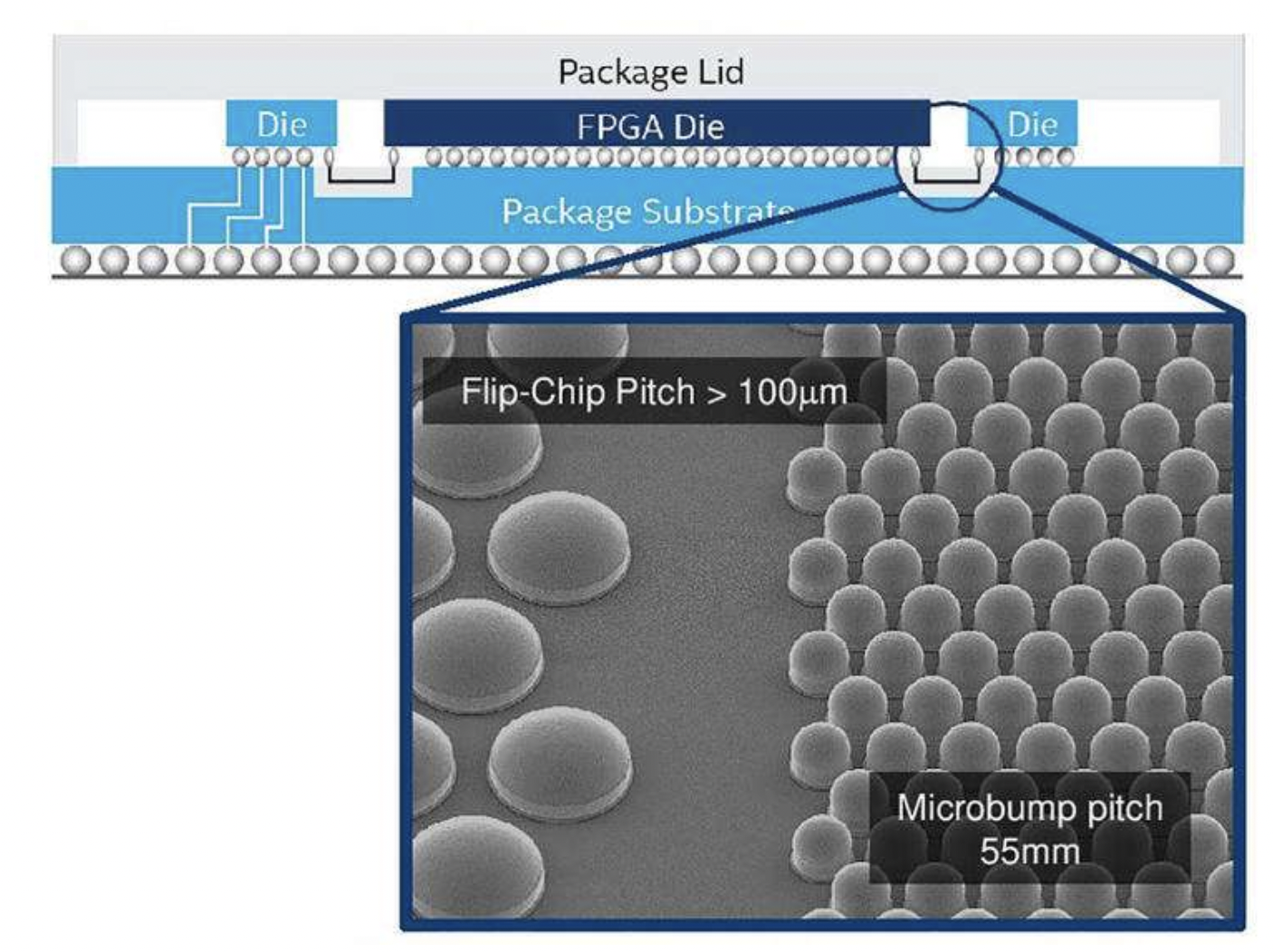

再往上一层,我们就有了包含在FPGA封装中的存储器。这一般是在高密度、高带宽、高带宽、高成本的技术中实现,比如HBM。由于我们是通过芯片外的方式来实现(通过互插器或EMIB或其他封装链路),所以延迟和带宽比嵌入式存储器要低,但比通过传统的存储器接口(我们稍后会讲到)在PCB上的芯片外实现要好。

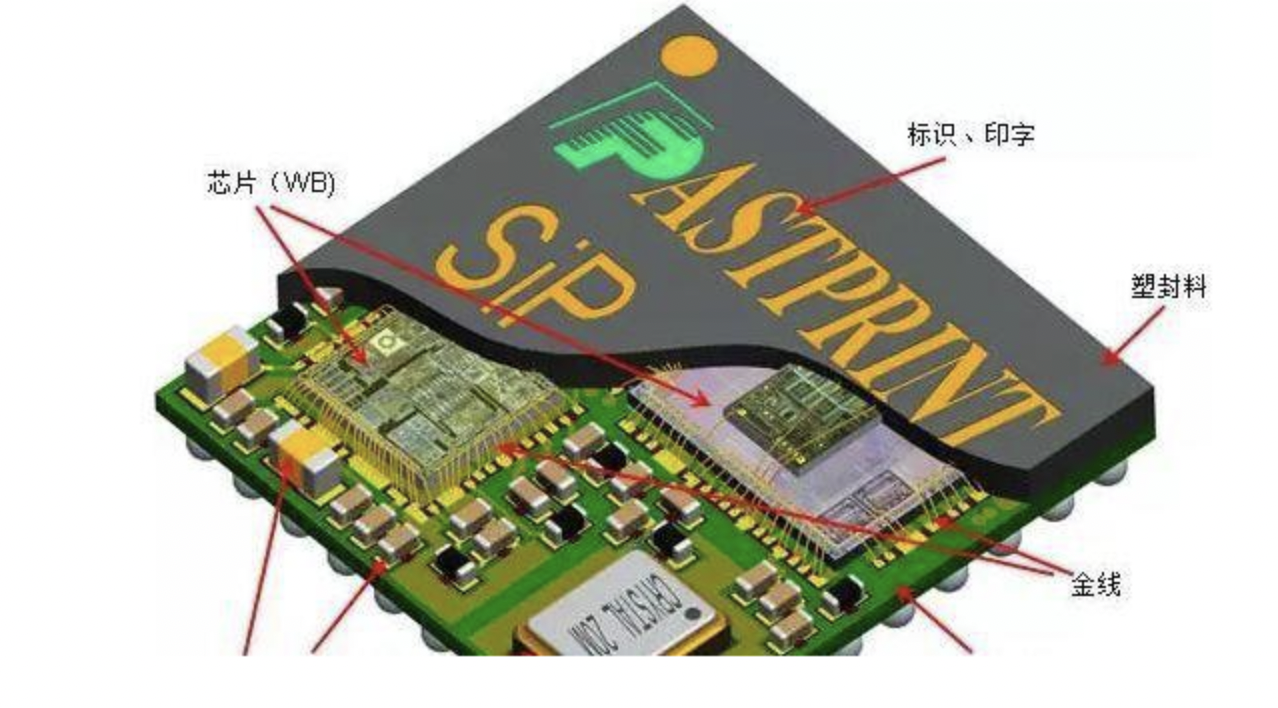

然而,在讨论封装内存储器之前,我们应该先谈谈三家厂商在封装层面的集成方式的根本区别。在这里,我们将以最小的终端用户投资获得英特尔Agilex的最大灵活性。英特尔的Agilex从一开始就为封装内集成的灵活性而设计。英特尔使用了一种名为EMIB(嵌入式多模互连桥)的专有技术来连接封装内的芯片组。FPGA结构本身是一个芯片组,SerDes收发器是另一个芯片组,封装内存储器(如HBM等)是另一个芯片组,还有其他可选的外设。这些外设都可以用不同的工艺技术来实现,这意味着英特尔可以随时更新或刷新任何芯片组,而无需重新设计整个FPGA(就像他们用单片机方法一样)。英特尔在这里的额外优势是他们能够基于最近获得的eASIC技术夹带定制芯片组。这意味着用户的定制逻辑可以添加到FPGA的封装中,只需最小的NRE和设计开销就可以实现。

Achronix已经宣布了Speedster 7t作为一个独立的芯片系列,但也有一个Speedcore嵌入式FPGA版本,它包含了与Speedster7t相同的资源,但也可以包含自定义指令,以进一步优化特定类别的应用;这些可能是专用的数据包处理、TCAM或信号处理功能。在这种情况下,在芯片与封装之间的集成决定,以及在FPGA结构的同一块硅片中包含哪些硬化IP,完全由客户的设计团队决定。这种方法为最终用户提供了最大的灵活性和控制权,但对客户端的成本、风险和设计专业技术要求更高。

Achronix也从事Chiplet(芯粒)业务,并参与开放计算项目(OCP)的开放域专用架构(ODSA)计划。ODSA正在努力建立标准,以驱动开放的Chiplet(芯粒)生态系统,这将有助于创建混合并匹配来自多个供应商的小芯片的SiP。这将允许与英特尔类似的封装级定制,但不能使用英特尔专有的EMIB互连技术。Achronix的观点是,设计团队通常最初会使用独立的FPGA解决方案,一旦设计通过验证,便会进行降低成本的回合,其中可能包括将一些逻辑强化到也包含可编程FPGA IP模块的标准单元ASIC设计中,或者使用Chiplet(芯粒)构建自定义SiP。

Xilinx在这三种设备中提供最少的设备自定义灵活性,但迄今为止却提供了最多的“开箱即用”选项。赛灵思(Xilinx)是FPGA多管芯集成的先驱,它使用插入器将多个小芯片拼接在一起,形成了三代产品。有趣的是,Xilinx在其他人推动该战略的同时也放弃了该战略。Xilinx现在将其设备的更多功能构建到一个整体式芯片中。这带来了速度,成本和可靠性方面的优势,但降低了混合匹配Chiplet(芯粒)以定制封装内集成的能力。为此,Xilinx正在计划提供大量的Versal系列产品,以期提供具有适当资源集以匹配各种类型应用程序的现成设备。

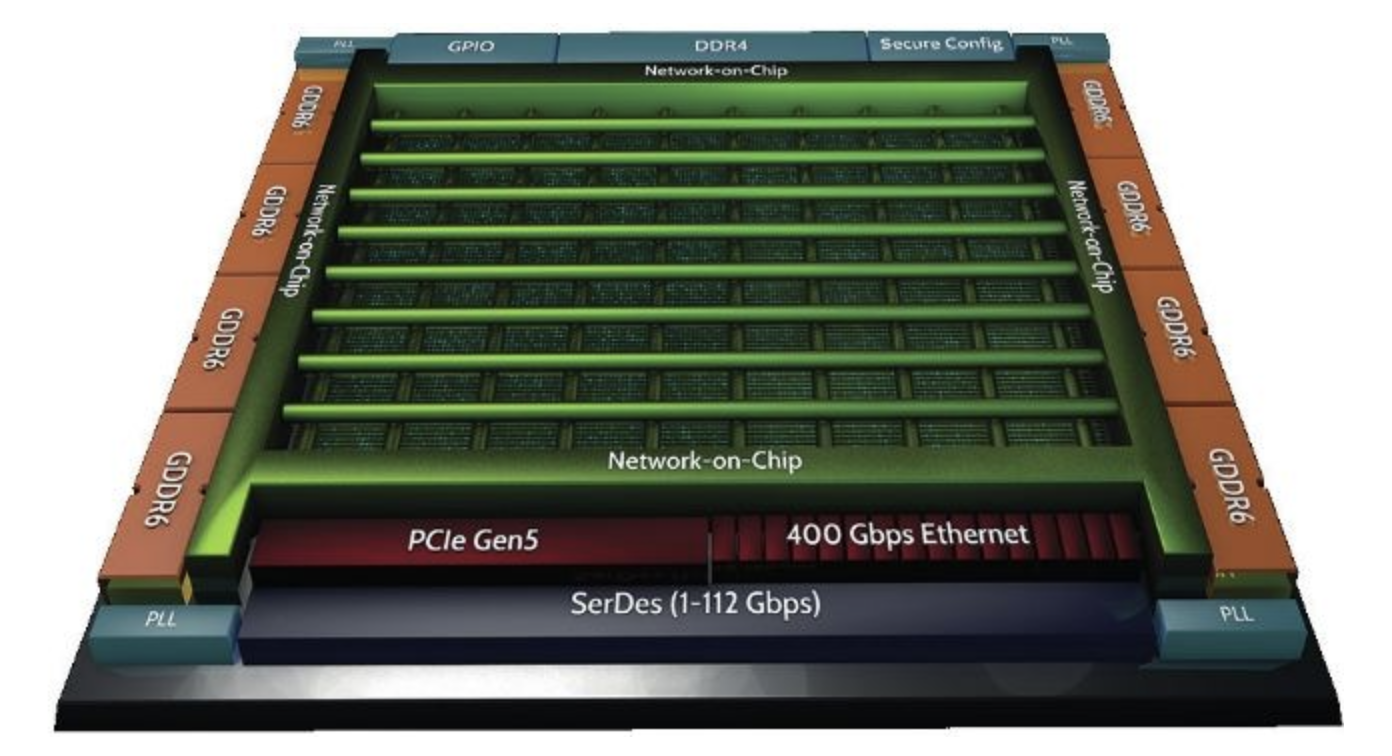

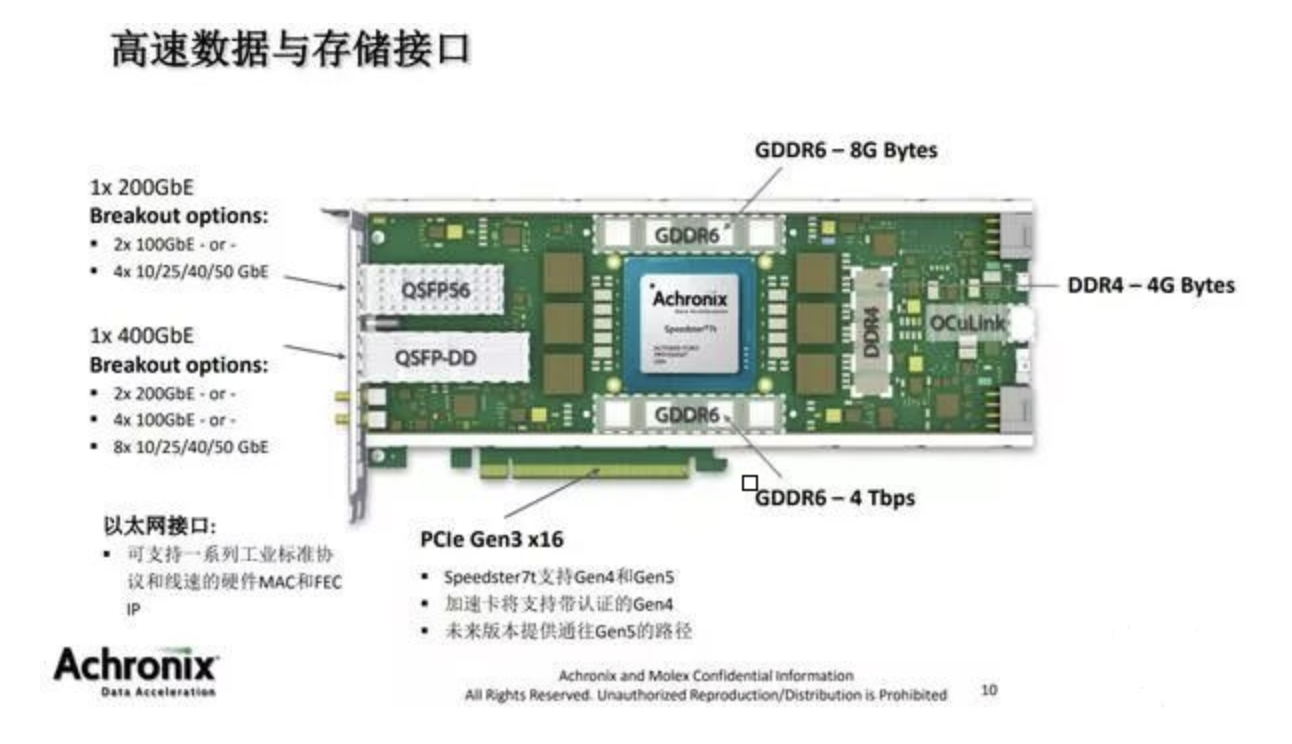

说回内置内存,那么,据我们所知,Xilinx和Intel都提供了类似的内置HBM堆栈。Xilinx表示会有Versal HBM系列,但还没有正式公布具体的细节,但我们可以根据他们在其他系列的支持来推测。通过Agilex,英特尔提供了最大16GB的HBM2,以及其他类型的内存资源放入包内的能力。Achronix 并没有提供内置内存选项,而是声称他们使用了8个GDDR6内存控制器,每个控制器可以支持512Gbps的带宽,给他们的设备提供了4Tbps的GDDR6带宽,这与其他厂商提供的HBM选项相当,但成本更低。与HBM相比,其代价是更多的功耗和PCB设计的复杂性。GDDR6的出现可能会更直接(考虑到图形子系统的目标市场),而HBM2还需要一些时间来实现量产。

寻找对板载内存的支持,所有供应商都支持DDR4,并将支持DDR5。

英特尔Agilex继续他们的方法,即提供带有加固的DDRx内存控制器(HMC,但不提供“混合内存立方体”)的加固的内存控制器。英特尔进入HMC已有多年历史,其历史可追溯至28纳米的Altera Arria 5系列。英特尔表示,他们的FPGA集成式硬存储器控制器有助于在硬PHY中实现从内核到外围的紧密传输以及从外围到内核的时序传输,有效地保证了时序收敛并减少了编译时间,并减少了半速率模式下的读写存储器延迟。英特尔还支持其非易失性Optane持久性内存,该内存通过非易失性技术提供类似于RAM的性能。

Xilinx Versal AI Core系列(也使用加固的内存控制器)可提供高达1.2 Tbps的DDR4带宽和高达1.6 Tbps的LPDDR4带宽,并支持CCIX。(缓存一致性的加速器互联,即CCIX™(读成“see 6”)是一种能够将两个或两个以上器件通过缓存一致性的方式来共享数据的片间互联。CCIX规范的最大优势之一是它建立在PCI Express规范的基础之上。CCIX的一致性协议只需很少修改或者无需修改就可以通过PCI Express链路传递。)

有趣的是,英特尔还通过UPI / CXL协议支持对英特尔至强可扩展处理器的低延迟/一致性存储器层次结构访问。在以后的部分中,我们将与其他供应商讨论更多有关集成到异构计算环境中的问题,并与其他供应商进行讨论。

如上所述,Achronix(还利用了硬化的内存控制器)还支持GDDR6。在外部存储器中,端口数量是许多应用程序的关键考虑因素,因为能够从共享内存资源同时执行多个读/写操作的能力可以消除与内存带宽相关的性能瓶颈。

FPGA的高速I/O

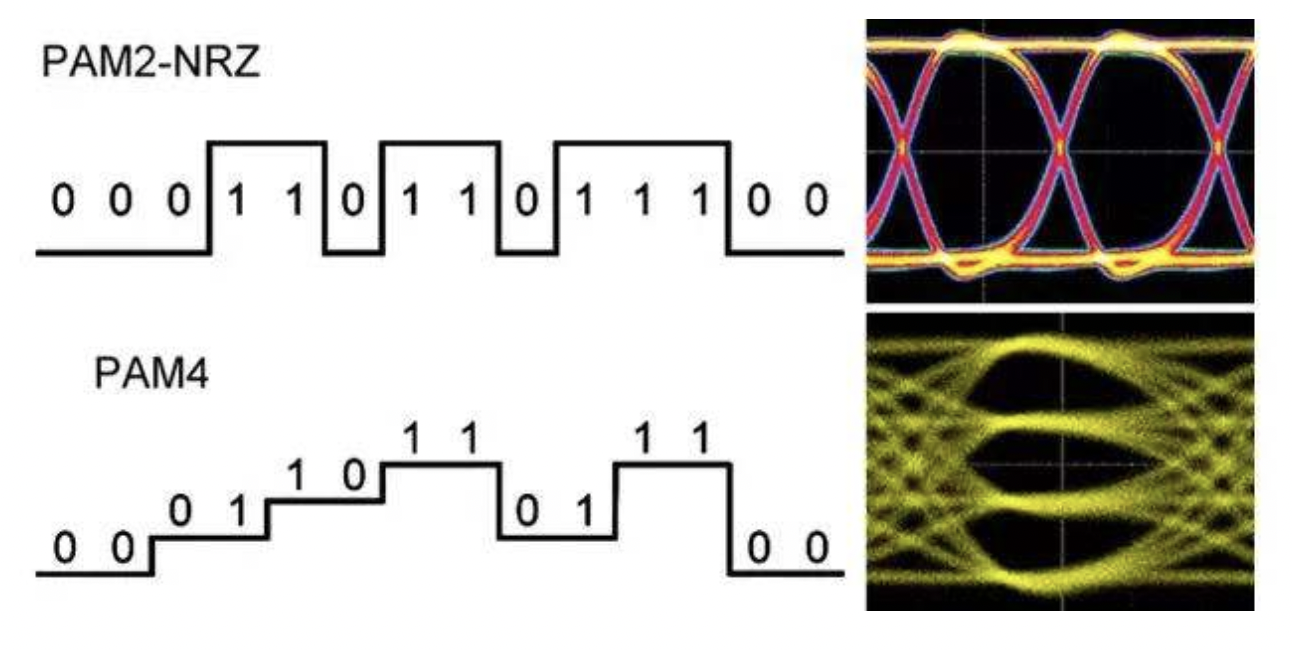

当然,除非能够有效地将数据移入或移出,否则出色的芯片就无法完成出色的工作。在数据移动方面,FPGA是无可争议的王者-数十年来,他们凭借灵活的逻辑和高速IO功能在不同的系统和协议之间桥接,移动和路由大量数据,从而生存了数十年。现在,所有这些供应商已将其最快的高速串行IO收发器转移到更高吞吐量的PAM4技术。PAM4为逻辑定义了四个电压电平,而不是通常的两个电压电平,在每个时钟周期中将数据打包两次。

Xilinx Versal ACAP支持多达44个GTY收发器(32.75Gb / s),以及多达52个GTM收发器(58Gb / s),总IO带宽总计高达约1.31 Tbps。英特尔的Agilex系列产品可以包含一系列令人困惑的选项,因为SerDes收发器包含在不同的“ Tile”小芯片中,这些小芯片随应用领域的不同而变化,最高可达8x PAM4 112 Gbps,最高48x PAM4 58 Gpbs。Achronix Speedster 7t提供了惊人的72x PAM4 112 Gbps收发器。所有这些都是令人印象深刻的数字,但请记住,SerDes收发器带来了一些最艰巨的设计挑战,包括板级和系统级信号完整性。它们也是芯片成本的巨大贡献者,因此选择带有一组能够满足您的应用需求的收发器的设备值得仔细考虑。(可参考文章:Xilinx公司发布了单通道112Gbps的高速串口)

对于疯狂的快速以太网,Xilinx Versal ACAP首次推出了该公司内部开发的新型多速率MAC,该MAC可处理多种配置,包括4x10GE,1x40GE,4x25GE,2x50GE或1x100GE。Versal Prime ACAP设备最多包括这些多速率MAC中的四个。英特尔Agilex包括具有PCS的硬以太网MAC和支持16 x 10 / 25GE,8 x 50GE,4 x 100GE,2 x 200GE,1 x 400GE的FEC。这样最多可实现4 x 400Gb以太网网络接口连接。Achronix Speedster 7t在其7t1500中具有16个以太网通道,在7t6000中具有32个以太网通道。这分别提供了四个和八个400Gb以太网连接,并支持较低的速率。

对于PCIe,Xilinx Versal ACAP提供了1个用于加速器(CCIX)的Gen4 x16高速缓存一致性互连,该互连通过标准PCIe链路,最多4个Gen4 x8 PCIe和最多2个多速率以太网MAC进行操作。英特尔的Agilex提供PCIe Gen4 x16(每通道最高16 Gbps)和Gen5 x16(每通道最高32 Gbps)。Achronix Speedster最多支持2个PCIe Gen5 x16。

简而言之,所有这些系列都继承了FPGA的传统,即大规模、灵活的IO----而这个讨论仅仅是蜻蜓点水。我们可以用几篇文章来讨论这些器件上的高速接口的微妙但关键的细微差别,因此,请花点时间来了解你打算根据你的应用需求使用的任何系列的细节。考虑一下整体解决方案中哪些是硬性的,哪些需要在LUT结构中实现或支持。只购买你实际需要的带宽,因为如果你的应用不需要,就没有理由支付昂贵的高性能收发器。一般来说,法拉利跑车不是用来闲逛超市的。

在本系列的下一期中,我们将讨论处理子系统和与外部处理器的集成、使用这些设备的加速器卡等硬件生态系统,以及--也许最重要的是--设计和应用开发工具的支持,让我们从目标应用开发者的世界--无论是C/C++代码、TensorFlow、OpenCL、SystemVerilog还是其他语言或方言--变成能够利用这些设备的惊人力量的东西。

作者丨Kevin Morris

编译丨eejournal

原文链接:网络交换FPGA

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。