介绍

在FPGA上实现一个CPU是一个令人兴奋的事情,但是太复杂的CPU实现起来太难,而且不适合去了解计算机的架构,所以今天介绍一些小型的CPU,比如8051、MIPS、MSP430等~

关于RISC-V的项目,请查看《优秀的 Verilog/FPGA开源项目介绍(二)-RISC-V》

ZipCPU

http://zipcpu.com/about/zipcpu.html

项目介绍

ZipCPU是 Gisselquist Technology, LLC为 FPGA 环境构建的开源、功能齐全的 软核 CPU。

ZipCPU最初设计的唯一目的是在FPGA中创建一个简单的CPU,尤其是一个强大到足以运行 Linux的CPU 。

在项目中,ZipCPU是:

- 一个 32 位 CPU。所有寄存器都是 32 位宽,地址是 32 位宽,指令是 32 位宽,等等。

- 一个RISC CPU。它只实现了最少的指令集,比大多数其他“RISC”CPU 小得多。

- 加载/存储架构。只有加载和存储指令可以访问内存

- 符合 Wishbone 标准。所有外围设备都通过通用 Wishbone 总线上的内存映射 I/O进行访问。

- 冯诺依曼架构。指令和数据共享一个公共总线

- 流水线架构,具有预取、解码、读取操作数、执行和 回写阶段。执行阶段由以下四个模块之一实现:算术逻辑单元 (ALU)、 内存单元、 除法协处理器和浮点协处理器。

- 可配置的 CPU :可以选择CPU中的逻辑量 ,因此如果需要,可以用 LUT 换取速度。

下面是一些板卡实现的结果:

下图是最新实现的模块:

https://github.com/ZipCPU/openarty

是在Xilinx ARTY板卡上实现ZipCPU以及所有 Arty 外围设备的开源驱动程序。

ice-chips-verilog

https://github.com/TimRudy/ice-chips-verilog

我们知道CPU的核心就是各种逻辑资源,这个项目是使用Verilog实现74LS、74HC、74HCT 系列芯片(门、多路复用器、计数器、寄存器、加法器、乘法器等等)。

如果只是实现这些逻辑芯片也没有多大参考意义,这个项目是集成到Icestudio(Icestudio 提供可任意扩展的电路仿真(用于数字电路)),可以实现“虚拟面包板”功能,具体怎么使用项目有详细设计。

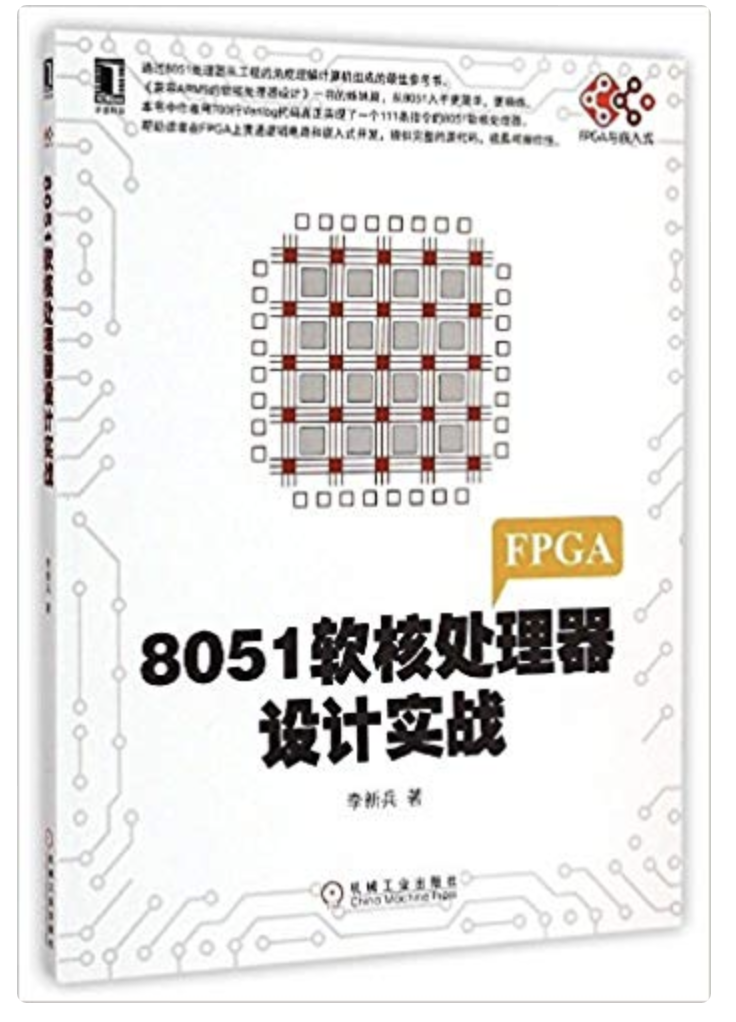

8051

一

https://github.com/risclite/R8051

上面这本书的源码,有中文参考书相信这个项目肯定不难实现。

书本的PDF:

链接:https://pan.baidu.com/s/1un2qtgekfKg8-_vLpnGm9g?pwd=open 提取码:open

二

https://github.com/freecores/8051

这个项目的详细设计文档:

https://github.com/freecores/8051/blob/master/doc/pdf/oc8051_spec.pdf

8051的项目很多很多,这里就不推荐太多了,因为实现的架构都差不多。

RP2040

https://github.com/lawrie/fpga_pio

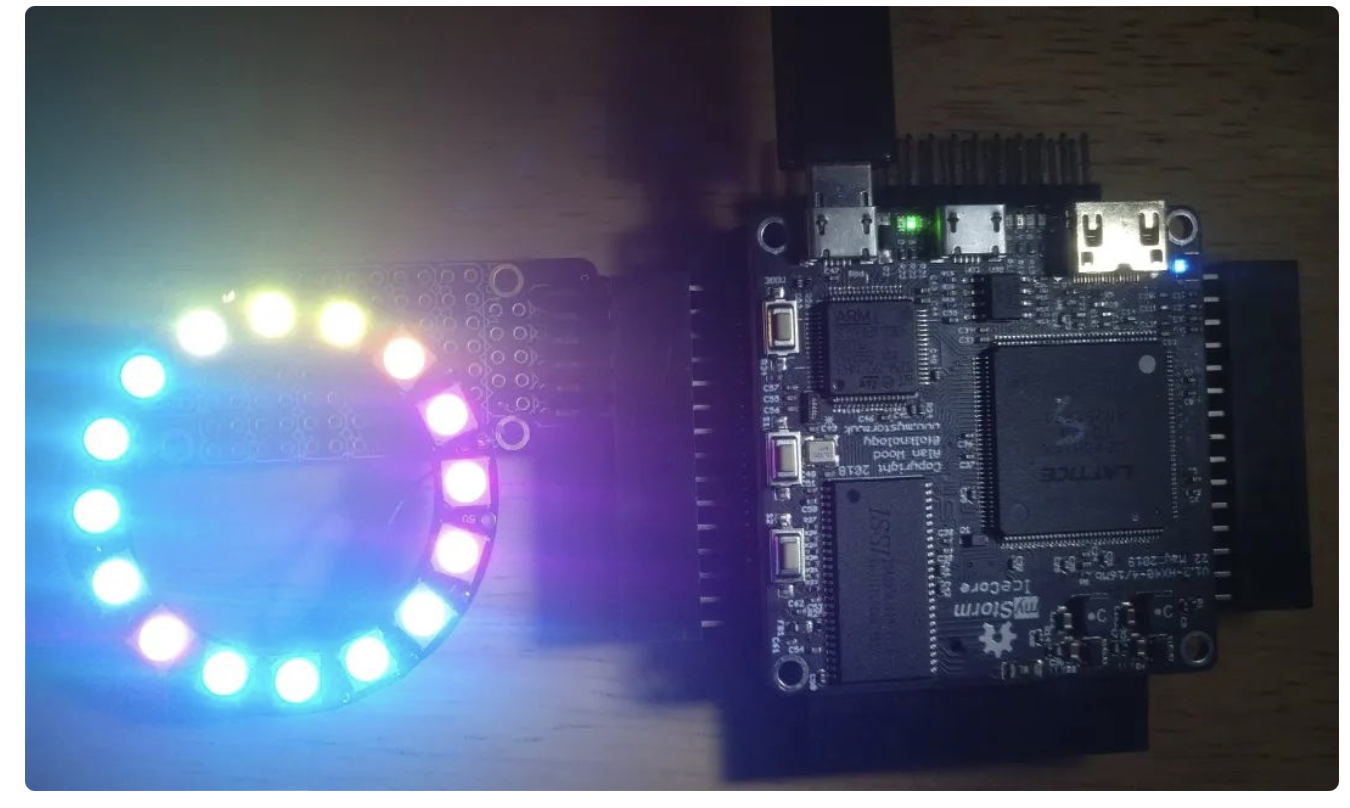

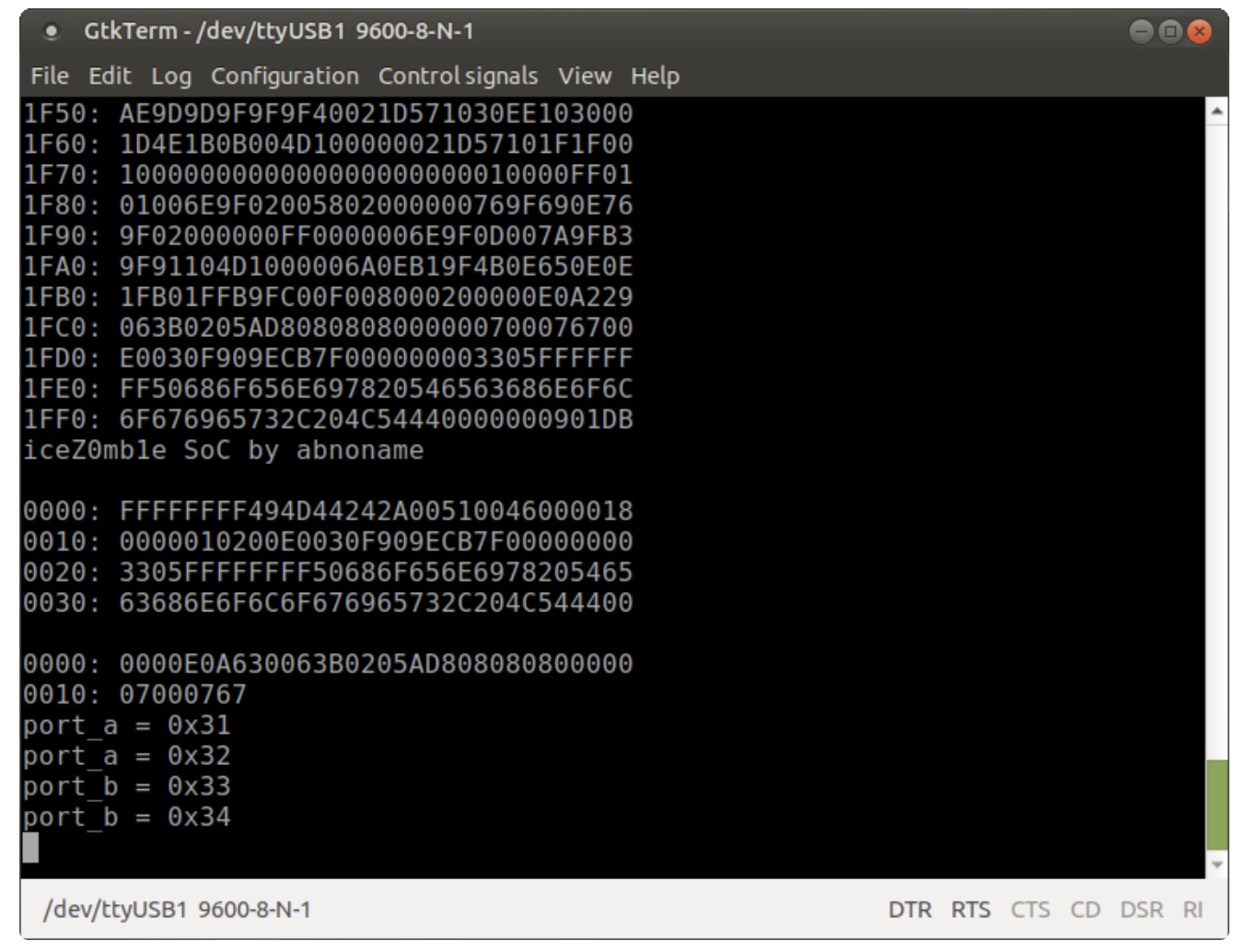

你能想象去年大火的单片机RP2040也能用FPGA实现吗~

是的,有大神已经实现了它,但是并不是整个SoC,而是RP2040中PIO 接口,PIO 即 Progammaable I/O,它是 RP2040 SoC 的一部分,它比 SPI、I2C、UART 等特定协议的硬件实现灵活得多。它可以实现所有这些协议和任何 GPIO 引脚。

同时,你可以尝试将这个项目集成到RISC-V SoC上,就自己实现了一个新的SoC。

TV80

用于 FPGA 的 8 位 TV80 SoC,使用 yosys 和 SDCC 的完整开源工具链。

MIPS

一

https://github.com/ljlin/MIPS48PipelineCPU

冯爱民老师《计算机组成原理A》课程设计

本实验通过工程化方法,使用 verilog 实现了一个支持 MIPS 指令集中48条指令,通过转发和阻塞支持冒险的 CPU。

其中48条指令如下:LB、LBU、LH、LHU、LW、SB、SH、SW、ADD、ADDU、 SUB、SUBU、MULT、MULTU、DIV、DIVU、SLL、SRL、SRA、SLLV、 SRLV、SRAV、AND、OR、XOR、NOR、ADDI、ADDIU、ANDI、ORI、 XORI、LUI、SLT、SLTI、SLTIU、SLTU、BEQ、BNE、BLEZ、BGTZ、 BLTZ、BGEZ、J、JAL、JALR、JR、MFHI、MFLO 。

src 文件夹内是一个 Sublime Text 工程,可以通过配置 iVerilog 编译,src/ljlin_Mips48 是编译好的脚本,可以通过 vvp 执行。testbench.vcd 是仿真生成的波形文件。

二

本仓库包含重庆大学由2017年开始实施的计算机组成原理课程改革实验内容,通过合理的梯度划分,一步一步由单独器件连接构成CPU,最后实现一个简单的MIPS五级流水CPU。

三

https://github.com/qing-2/CPU

xilinx fpga实现的mips。

MIPS的项目也多的数不胜数,这里只列出来两个,不是这两个项目做的优秀,而是都有相关的课程介绍,适合学习复现。

tinycpu

https://github.com/fallen/tinycpu

Tiny CPU 是一个小型的 32 位 CPU,主要用于教育目的。

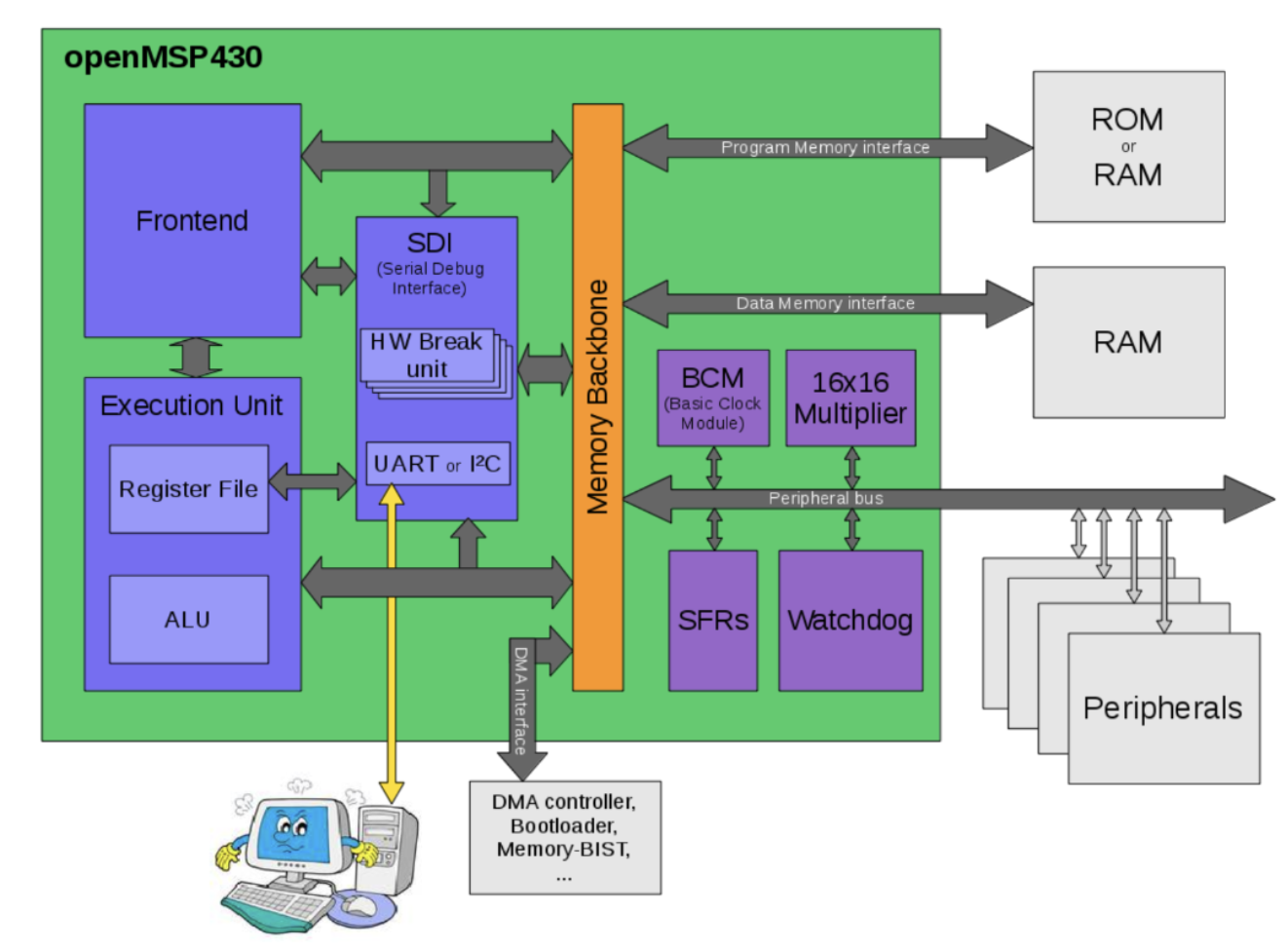

msp430

https://github.com/olgirard/openmsp430

Verilog实现的16位微控制器MSP430的内核。

详细的设计文档:

https://github.com/olgirard/openmsp430/tree/master/doc

ARM7

https://github.com/chsasank/ARM7

六级流水线ARM7TDMI处理器的实现。

主要模块:

ARM-LEGv8

https://github.com/nxbyte/ARM-LEGv8

此项目包含用 Verilog 编写的 ARM LEGv8 CPU 的源代码。

支持的指令包括:LDUR, STUR, ADD, SUB, ORR, AND, CBZ, B, 和NOP.

这本书也是一本经典书籍的软件仓库,书名《Computer Organization and Design ARM edition》

大家可能不熟悉,但是他的中文名大家肯定熟悉《计算机组成与设计:硬件软件接口》:

前面几个版本都是MIPS的,第5版是RISC-V版本,之前也分享过:

《图书推荐|计算机组成与设计(原书第5版) 硬件软件接口 RISC-V》

PDF版本:

链接:https://pan.baidu.com/s/1Pzsepkb5E30z2I8U3uBf5A?pwd=open 提取码:open

ARM9

https://github.com/risclite/ARM9-compatible-soft-CPU-core

Verilog编写的与ARMv4 兼容的 CPU 内核。

详细的中文设计文档

https://github.com/risclite/ARM9-compatible-soft-CPU-core/tree/master/TRAINING(CHINESE)

ARM_Cortex-M3

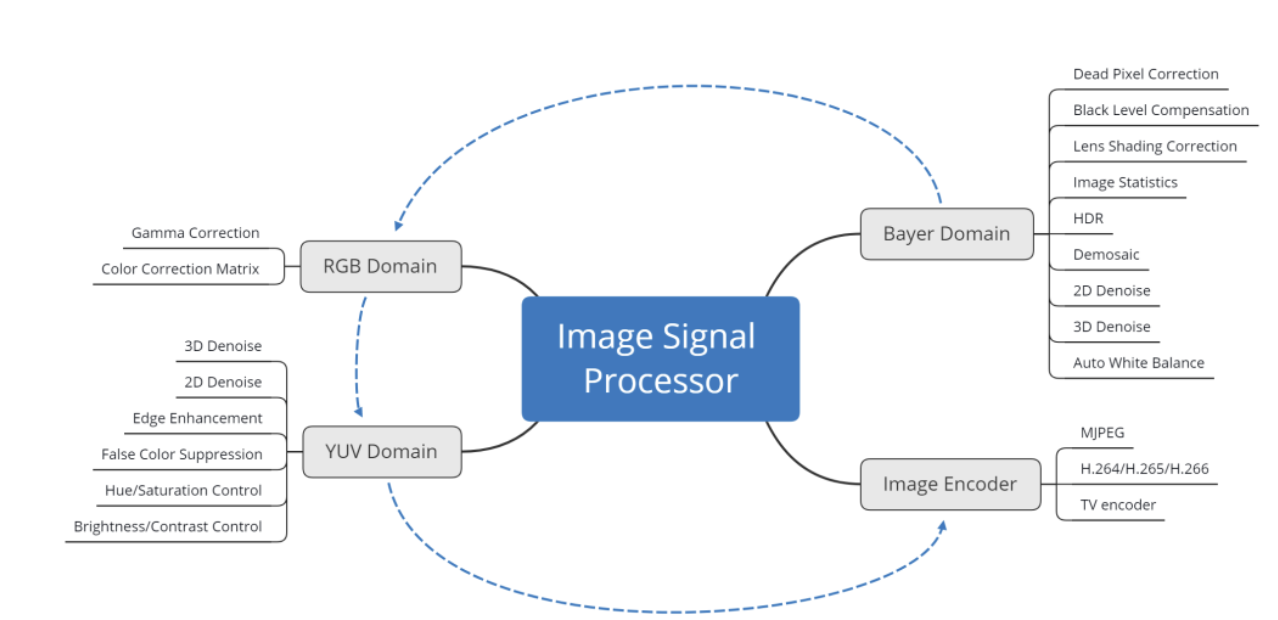

该项目依据全国大学生集成电路创新创业大赛“ARM杯”赛题要求,在FPGA上搭建Cortex-M3软核、图像协处理器,并通过OV5640摄像头采集车牌图像,实现对车牌的识别与结果显示。项目基于Altera DE1 FPGA搭载Cortex-M3软核,依据AHB-Lite总线协议,将LCD1602、RAM、图像协处理器等外设挂载至Cortex-M3。视频采集端,设计写FiFo模块、SDRAM存储与输出、读FiFo模块、灰度处理模块、二值化、VGA显示等模块。最终将400位宽的结果数据(对应20张车牌)存储在RAM中,输出至AHB总线,由Cortex-M3调用并显示识别结果。

总结

今天介绍了几个小型CPU,适合学习计算机架构相关知识,同时今天推荐的项目主要特点都是“易实现”,最明显的基本都是有详细的设计教程,但是代码肯定不是最优的。

今天的项目都适合复现~

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。