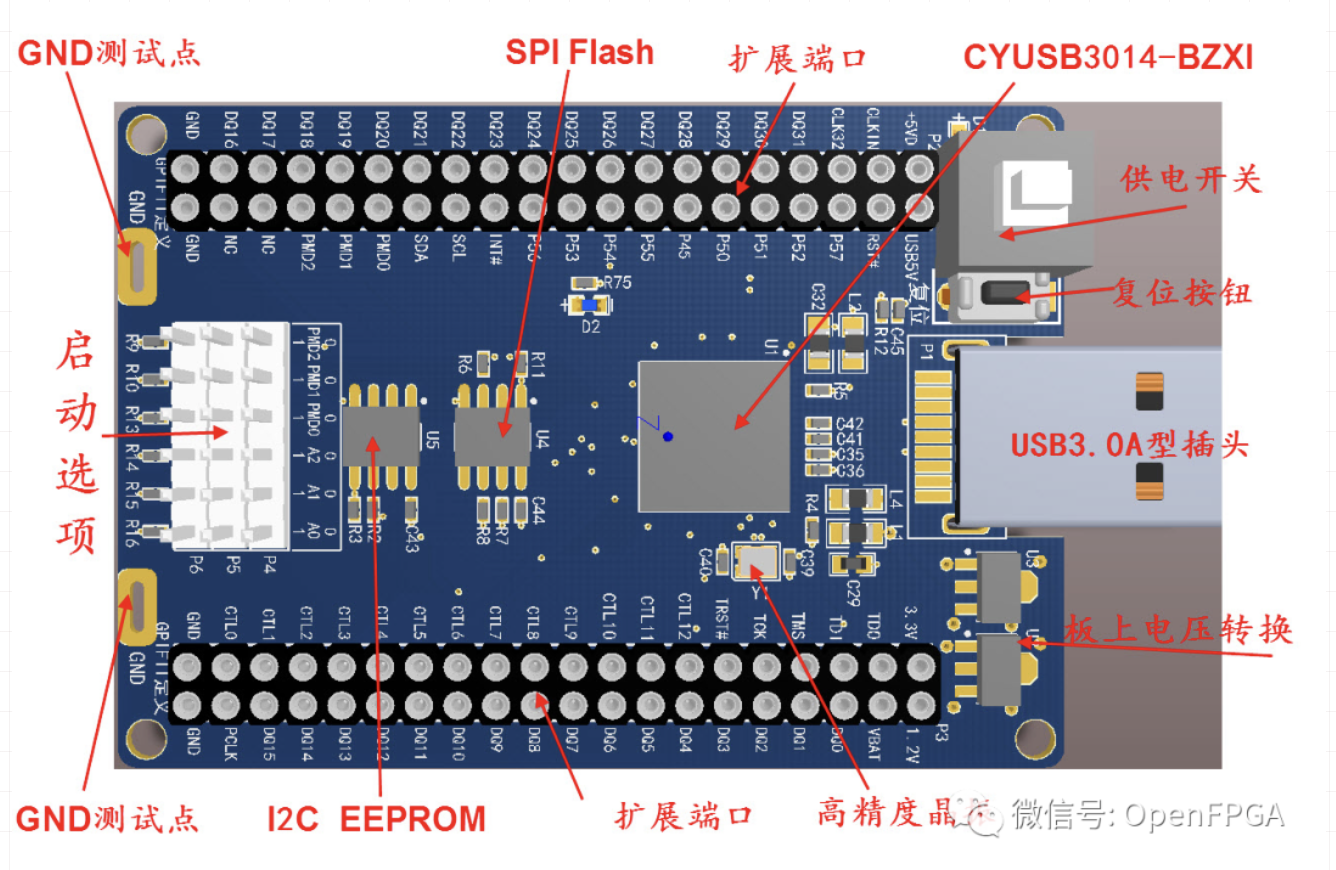

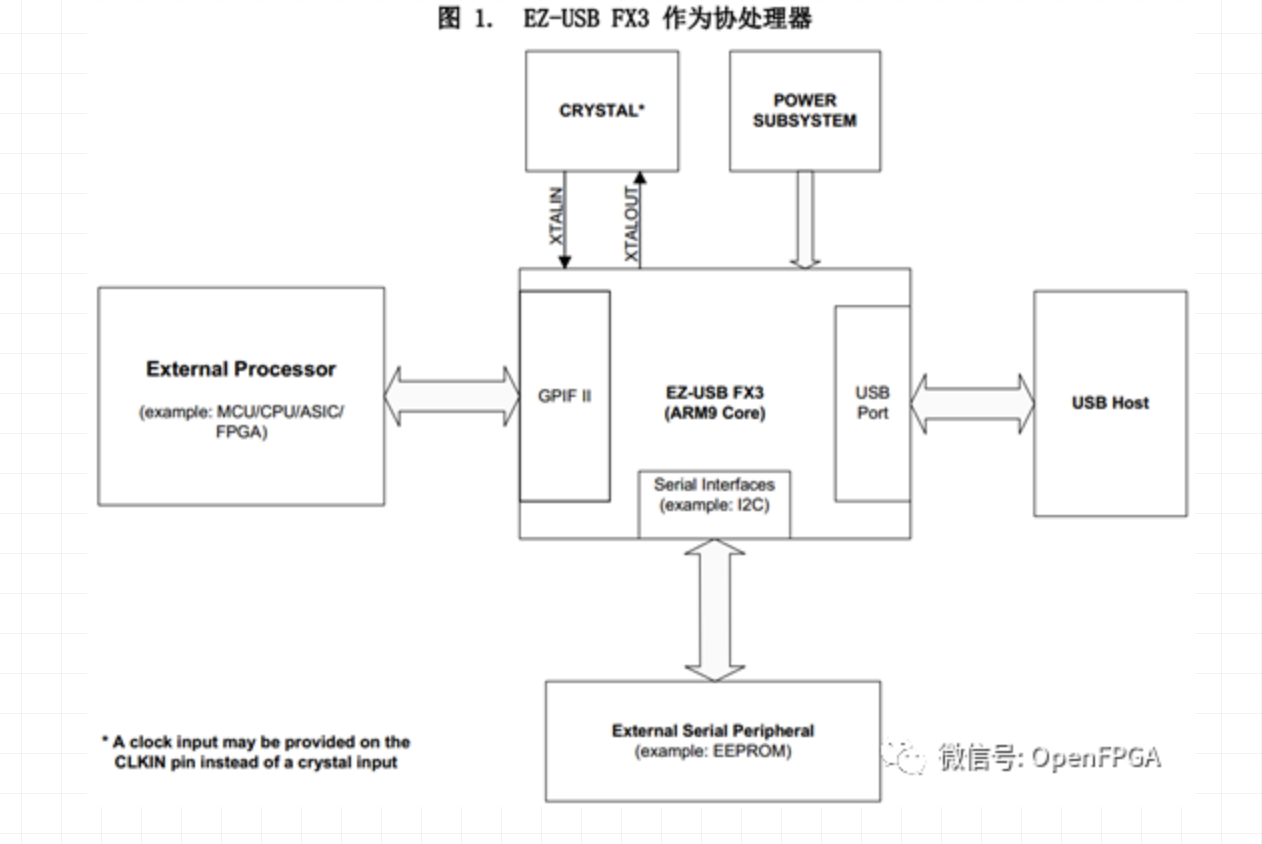

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写控制即可,同时该芯片还具有ARM核+I2S、I2C、SPI、UART等接口,大大增加了该芯片的使用范围。

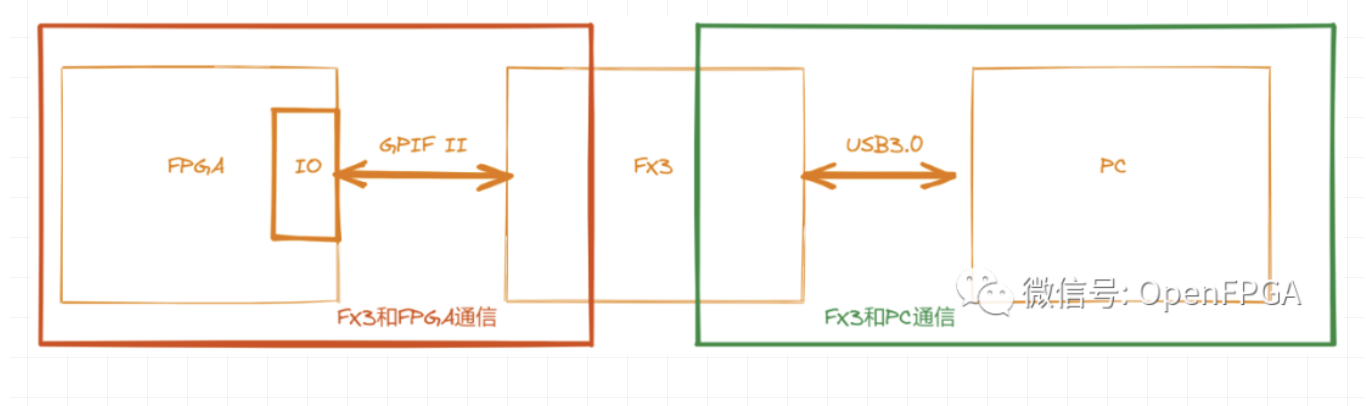

FX3应用中后半部分测试已经完成暨FX3和PC之间的通信:

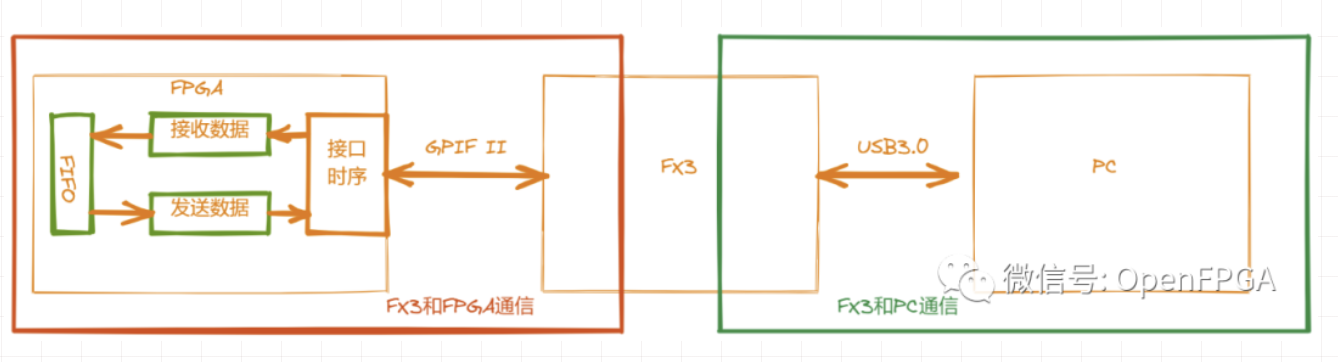

接下来就是通过FX3这个“桥梁”实现FPGA与PC之间的通信。

在此之前我们还需要打通FPGA和FX3之间的通信,通过前面的介绍我们知道FX3和FPGA之间是可以通过一个GPIF II的接口进行连接的,上一级我们介绍了GPIF II接口,这一节我们将利用官方工具搭建及测试接口。

GPIF II Designer工具的使用

产生配置头文件

使用 Cypress 官方提供的 GPIF II Designer 工具, 获取 GPIF II接口的配置参数, 然后将这些参数传递到 FX3 的 firmware 工程中进行编译。

双击桌面的快捷方式:

接下来打开工程,工程参考:

官方文档:《AN84868 - Configuring an FPGA Over USB Using Cypress EZ-USB® FX3™》

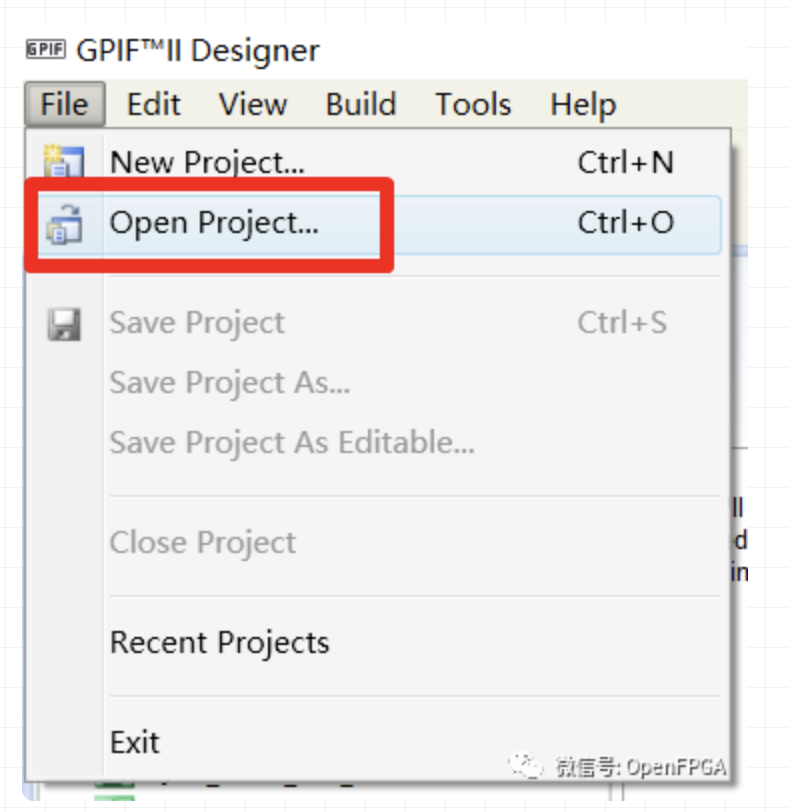

菜单File-->Open Project

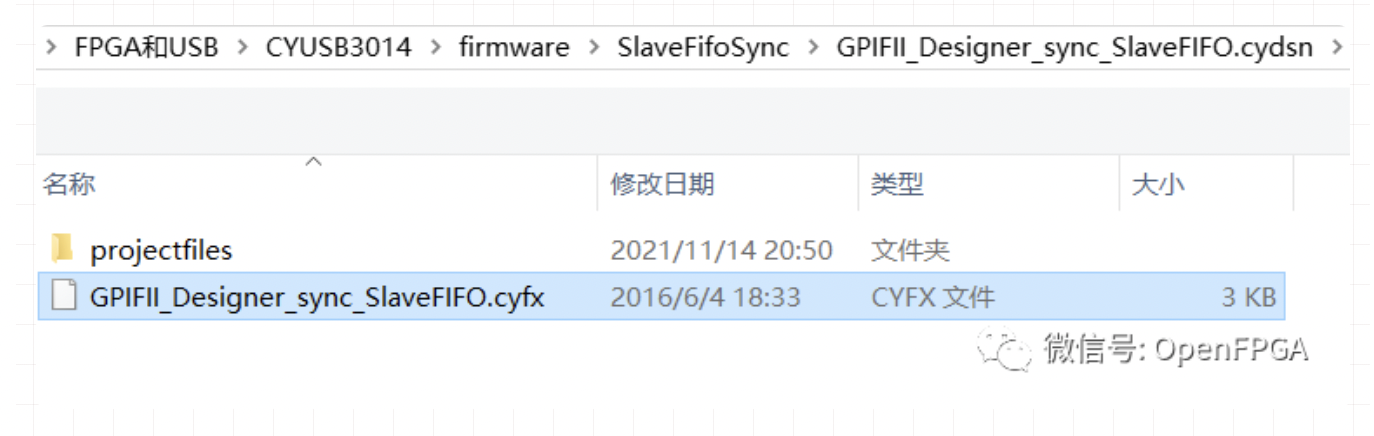

选中:

❝

XXX\firmware\SlaveFifoSync\GPIFII_Designer_sync_SlaveFIFO.cydsn

❞

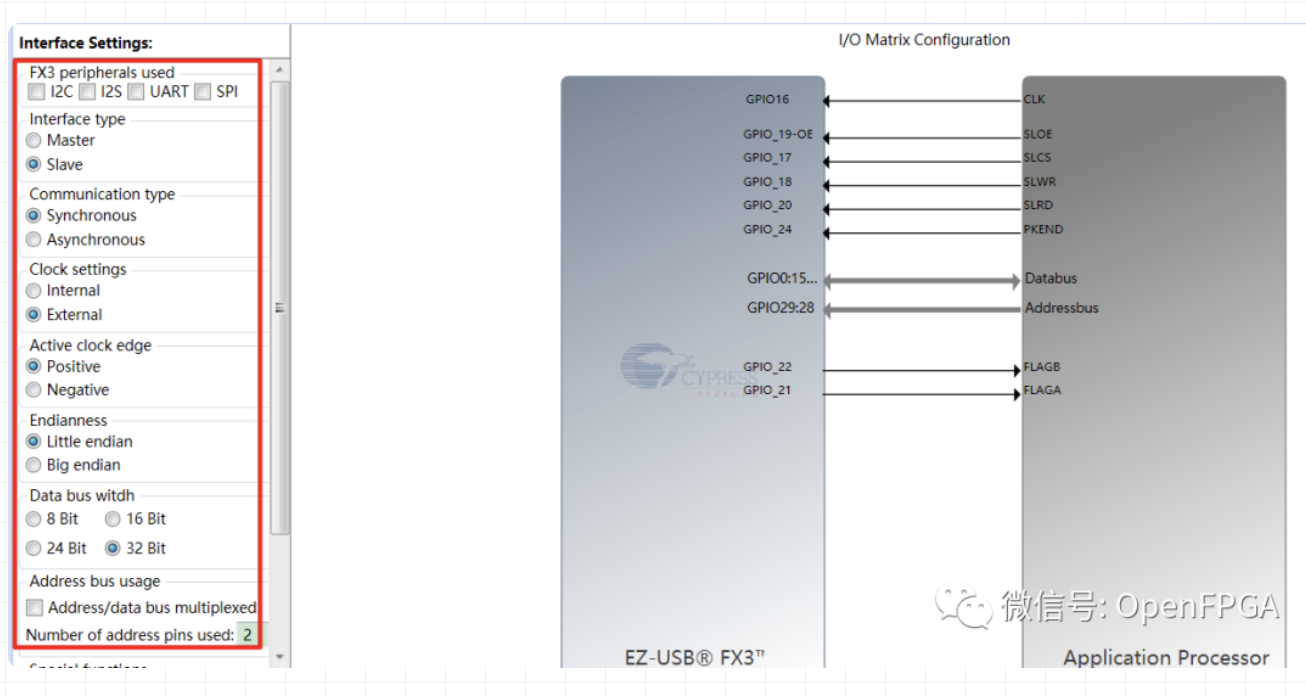

根据实际需求更改工程中的接口配置。下图使我们本次使用的32 位的 Slave FIFO 实现 FPGA 与 FX3 之间的数据传输。

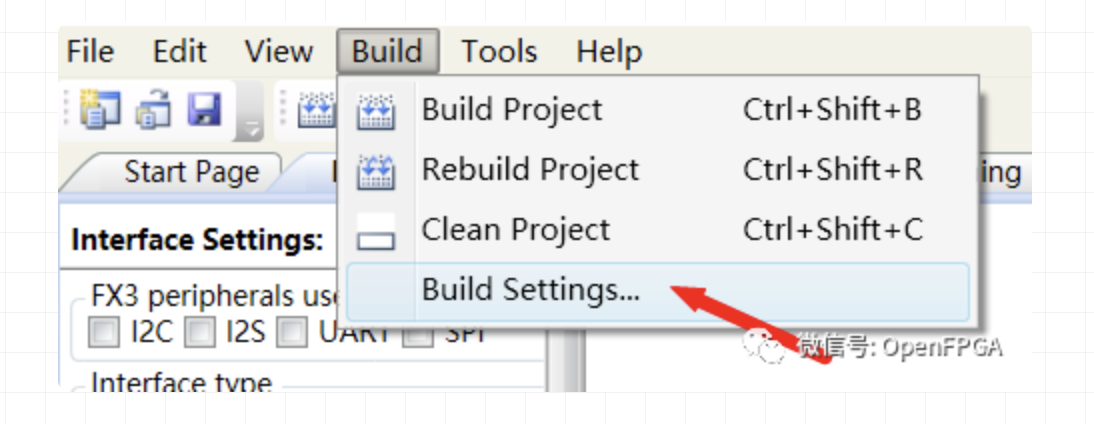

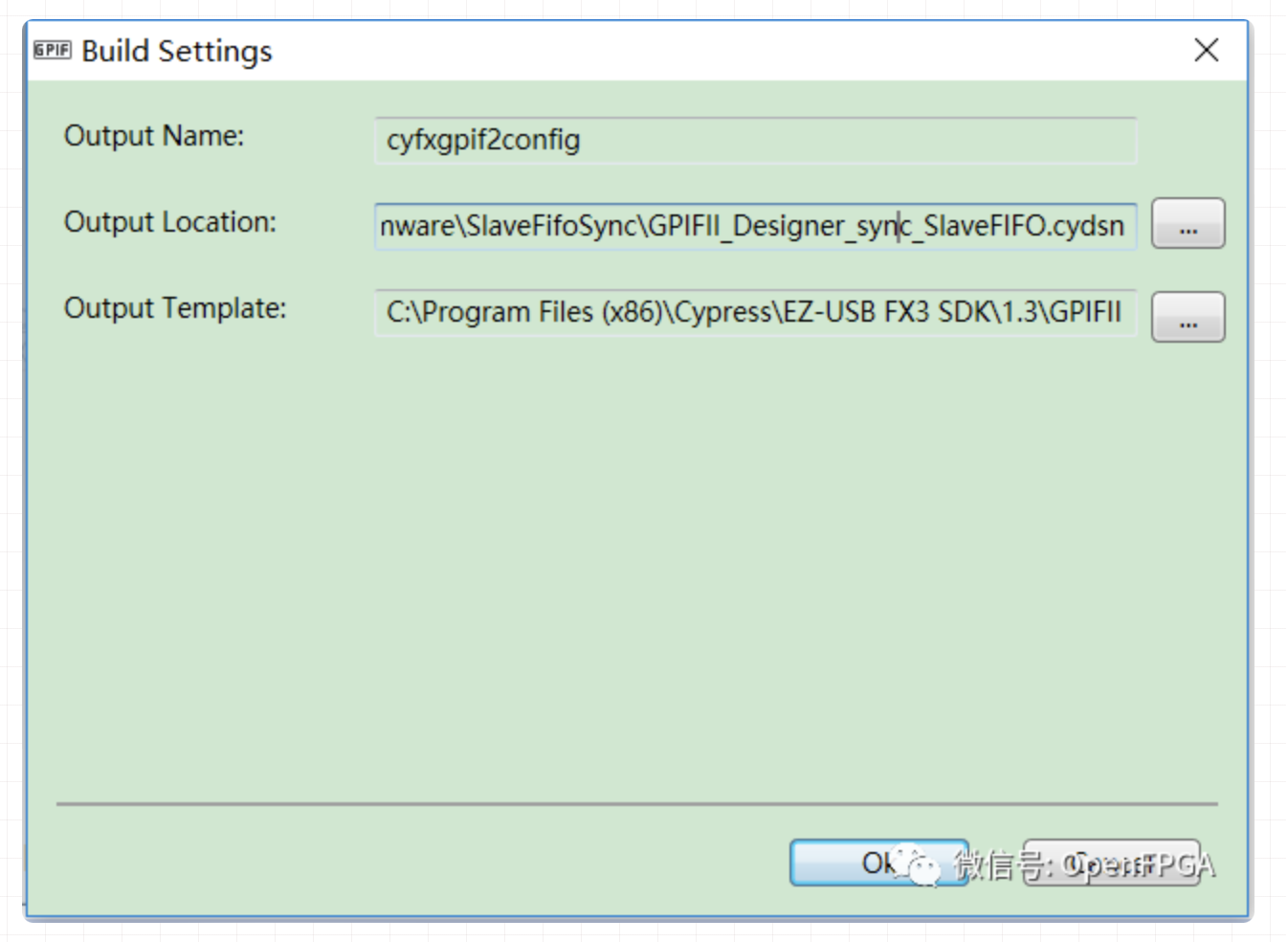

菜单Build--> Build Setting

设置输出路径,这里建议选择工程所在目录。

PS:Output Template路径不要动。

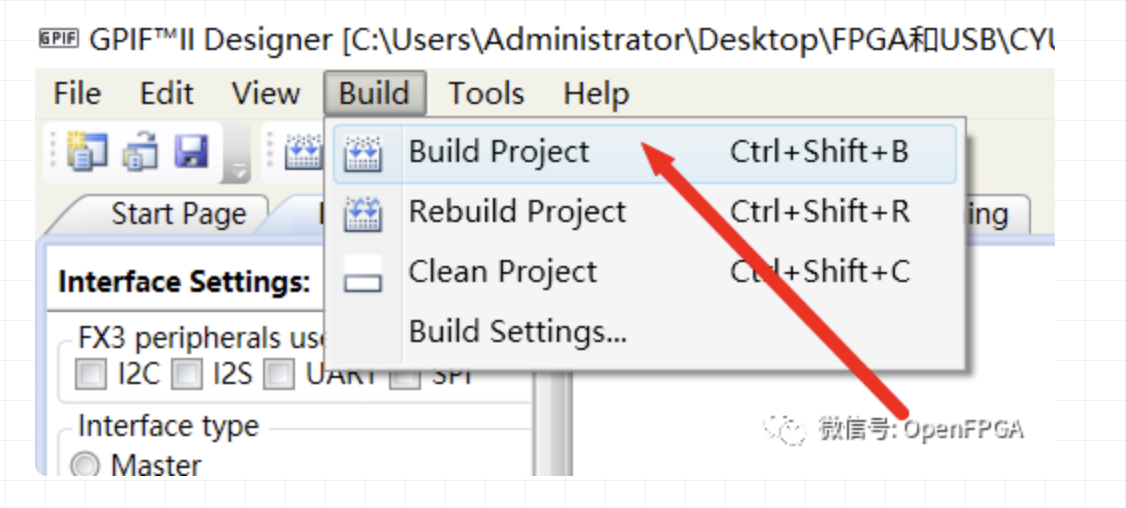

菜单Build--> Build Project对工程进行编译

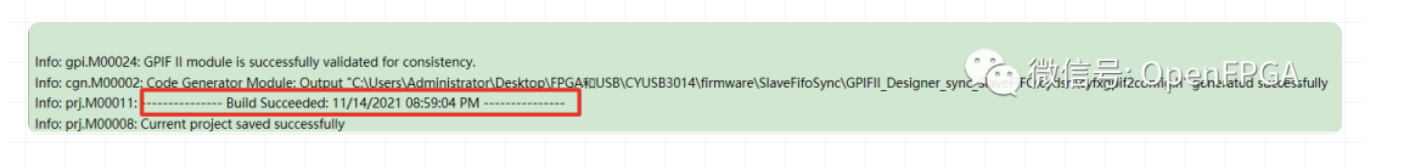

下面的OutPut窗口会出现编译成功的提示:

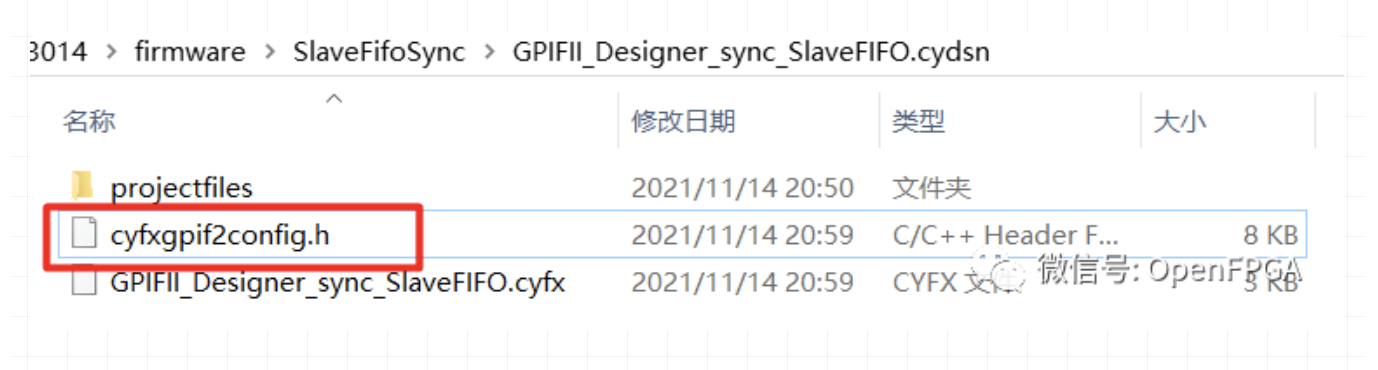

这时会在刚刚设置的路径下出现一个头文件《cyfxgpif2config.h》,如下图所示:

编译FX3所需的固件

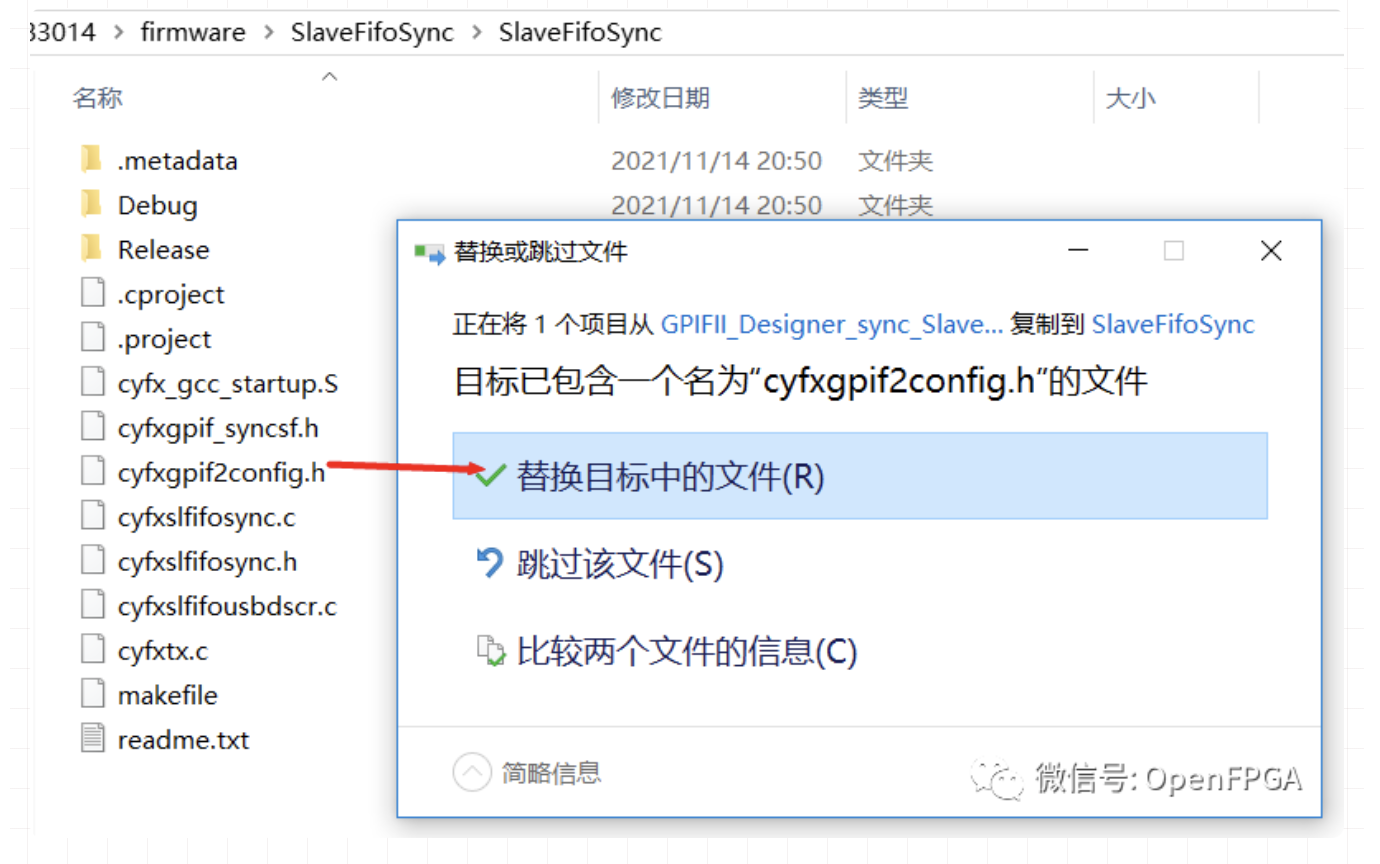

将上面产生的头文件复制到

❝

XXX\firmware\SlaveFifoSync\SlaveFifoSync

❞

替换源文件:

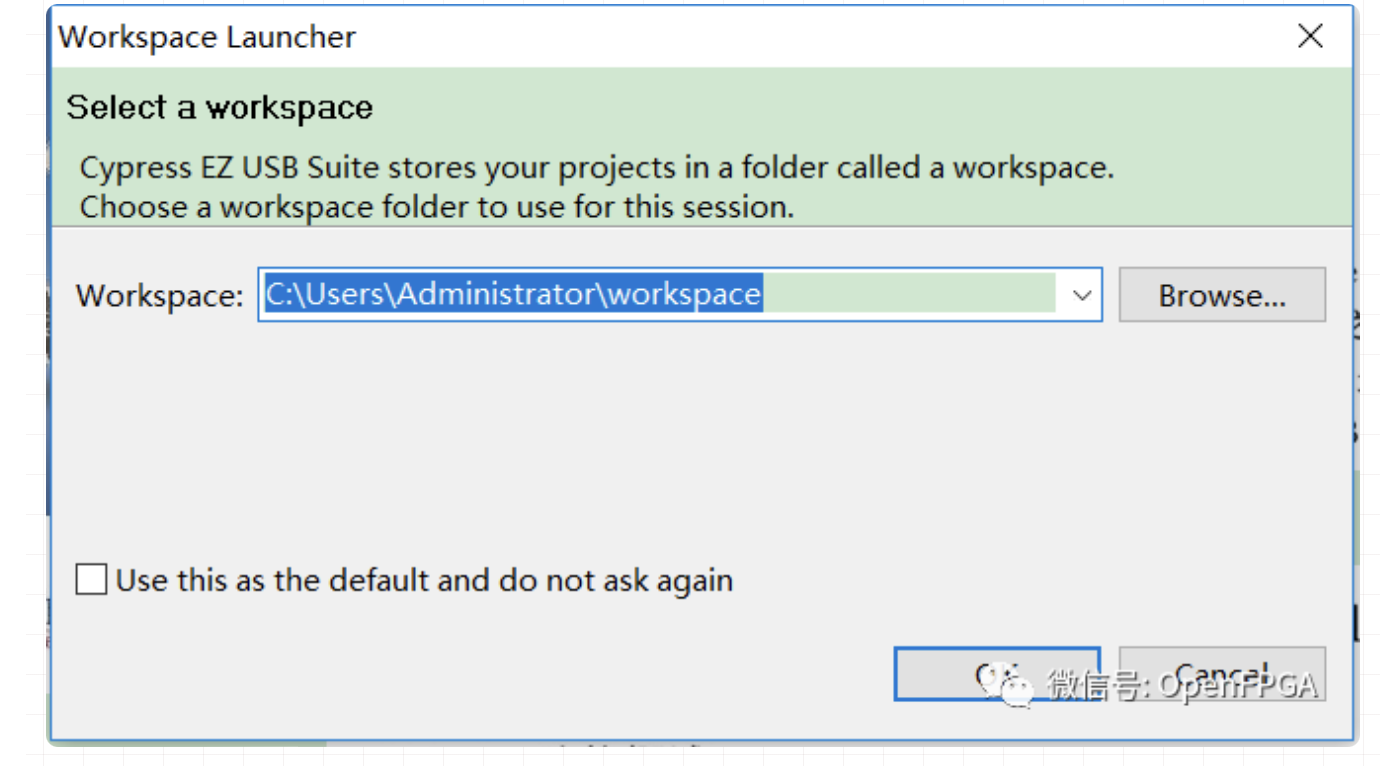

开启 EZ USB Suite

点击OK

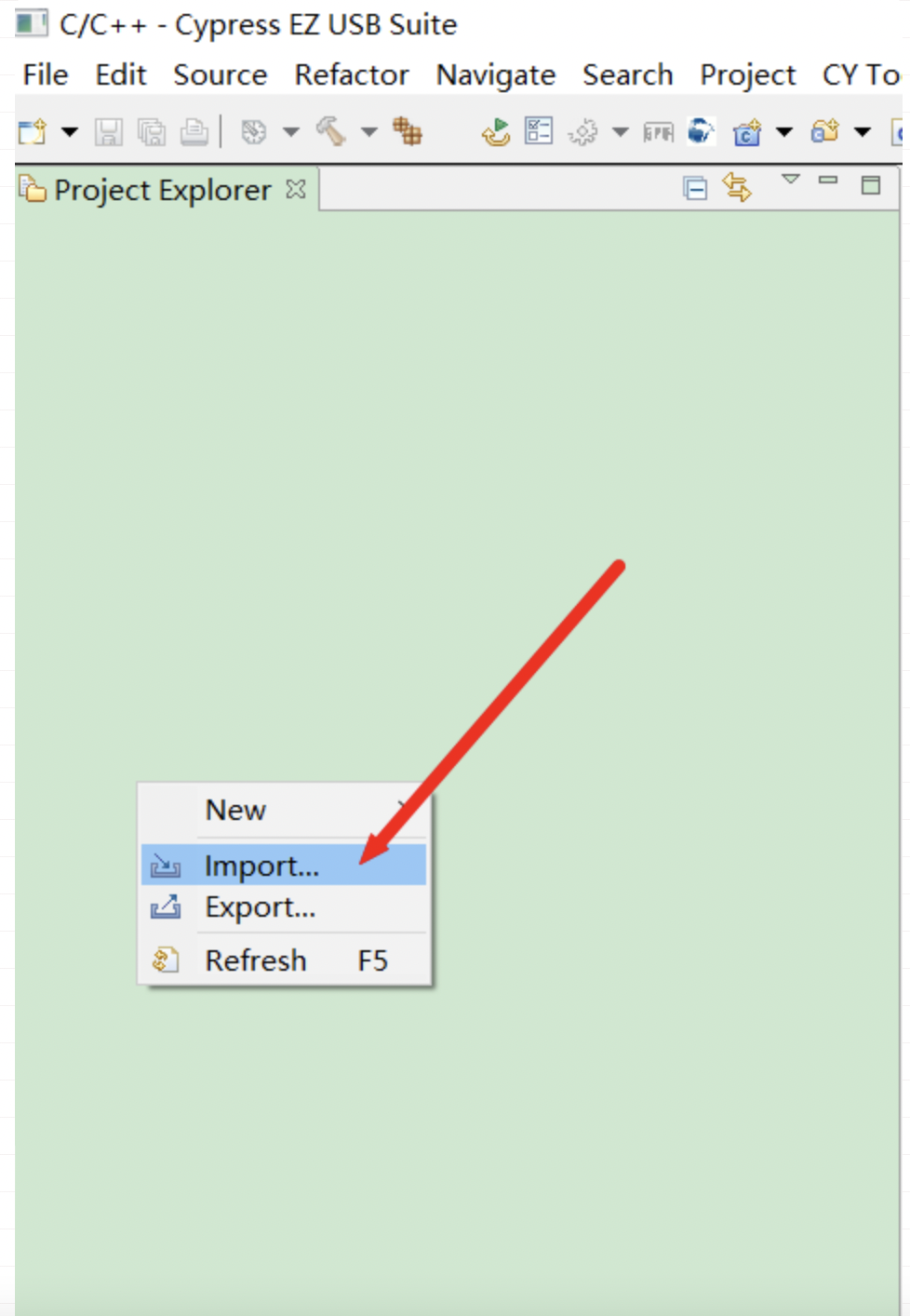

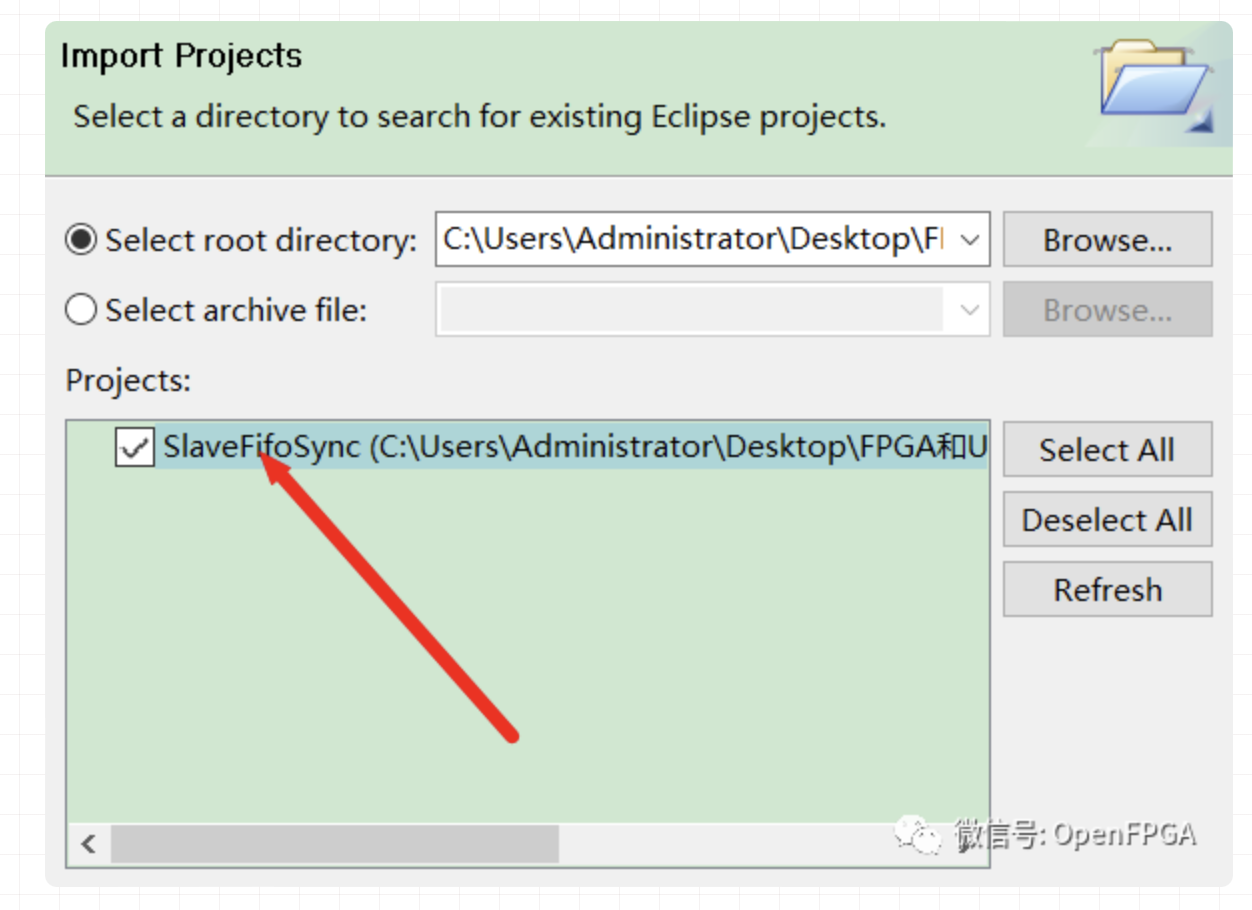

空白处右击,选中Import

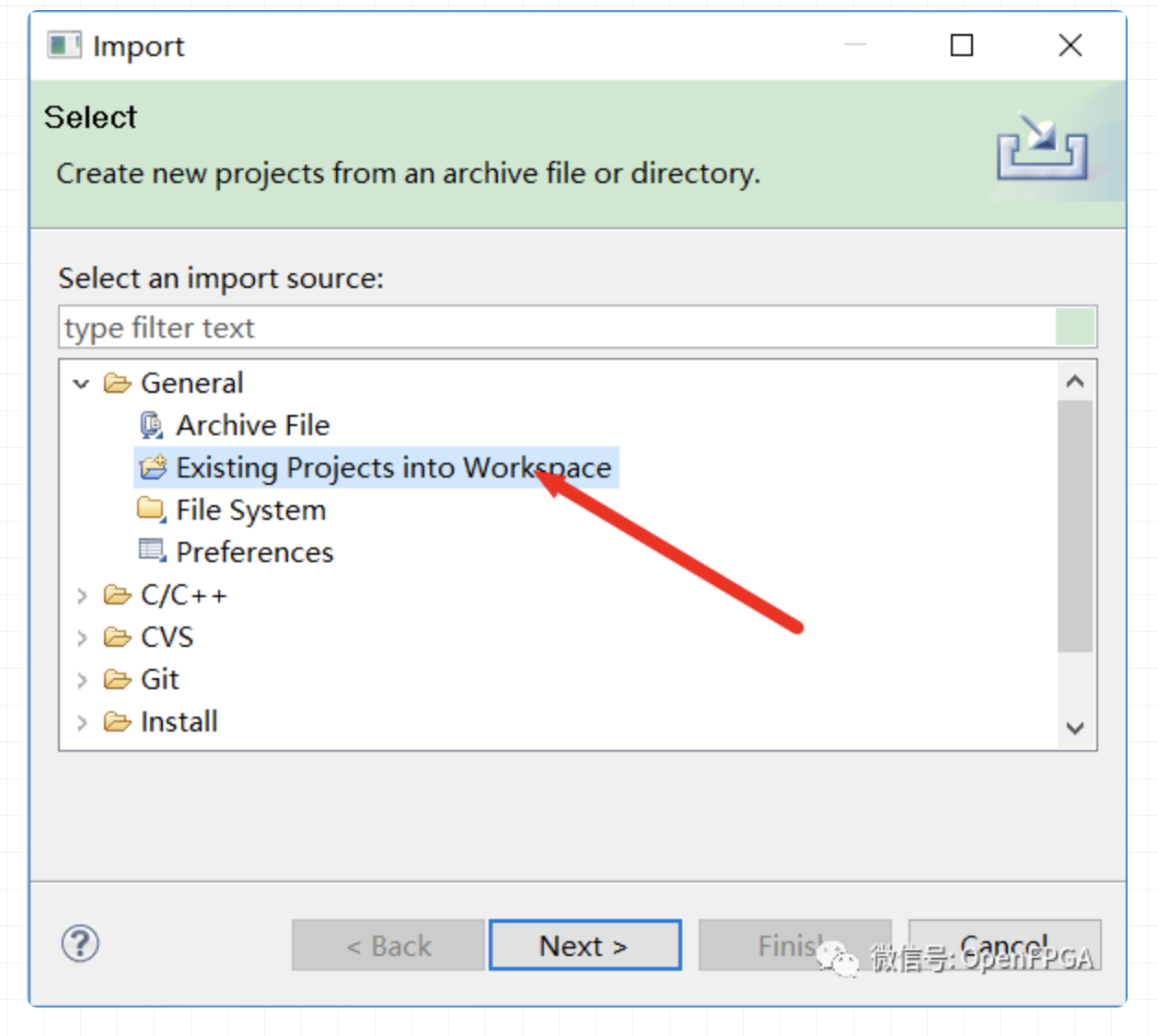

选择 Existing Projects into Workspace, 单击 Next 按钮进人下一步。

单击 Browse 按钮, 加载工程所在路径,定位到下面路径(刚刚替换头文件的路径),然后单击 OK 按钮。

这里要选中路径下的工程:

单击Finish

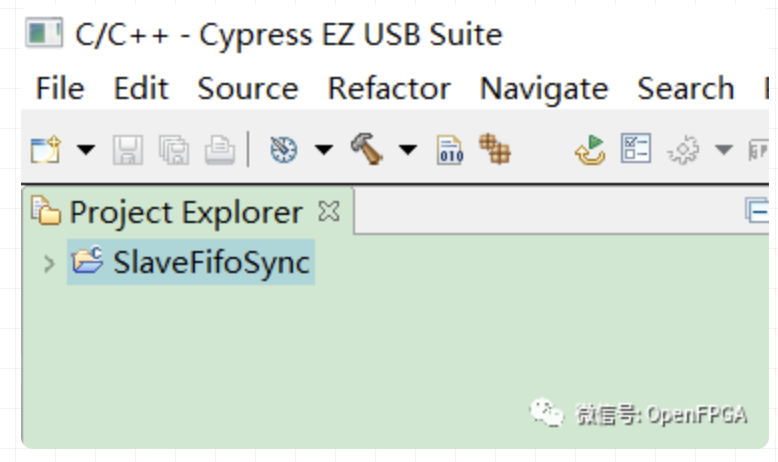

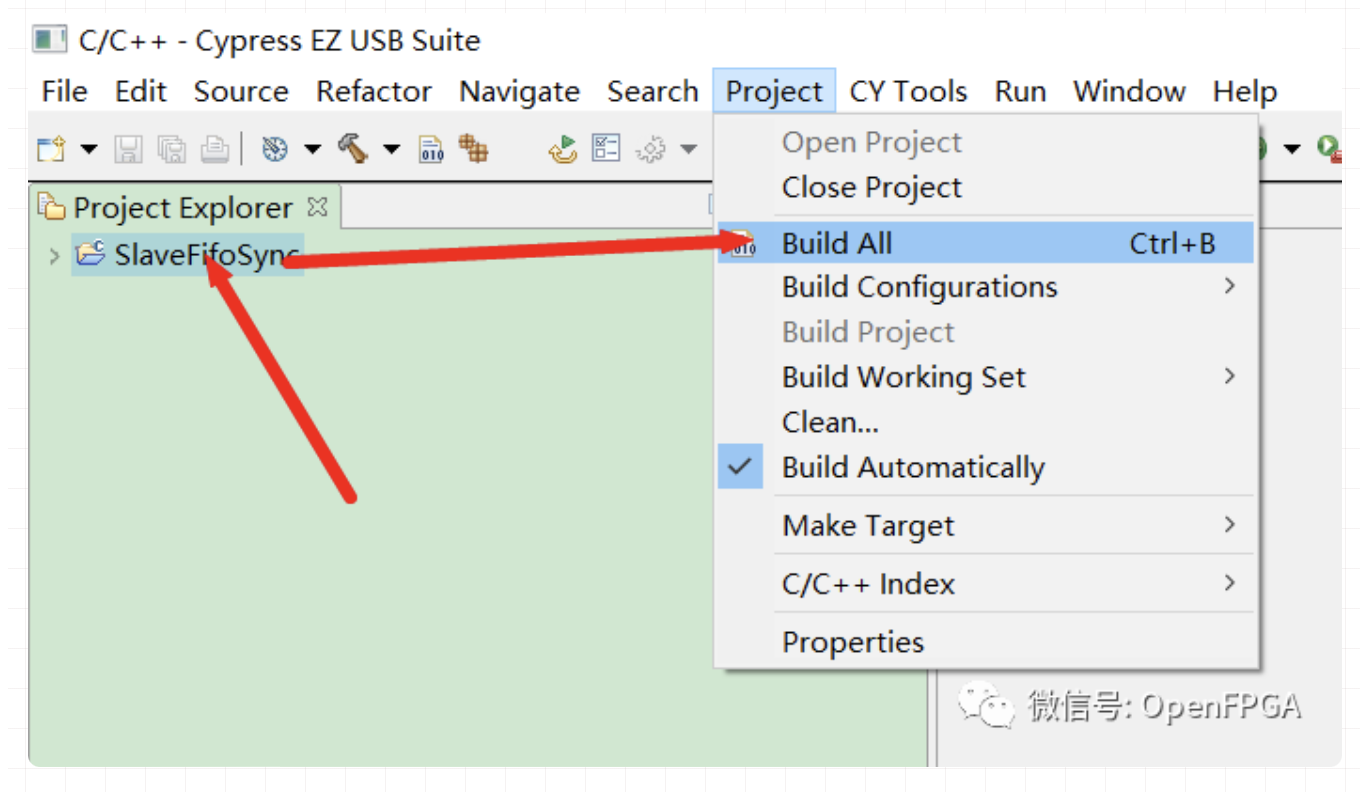

选中SlaveFifoSync工程,然后选择菜单 Project—Build All。

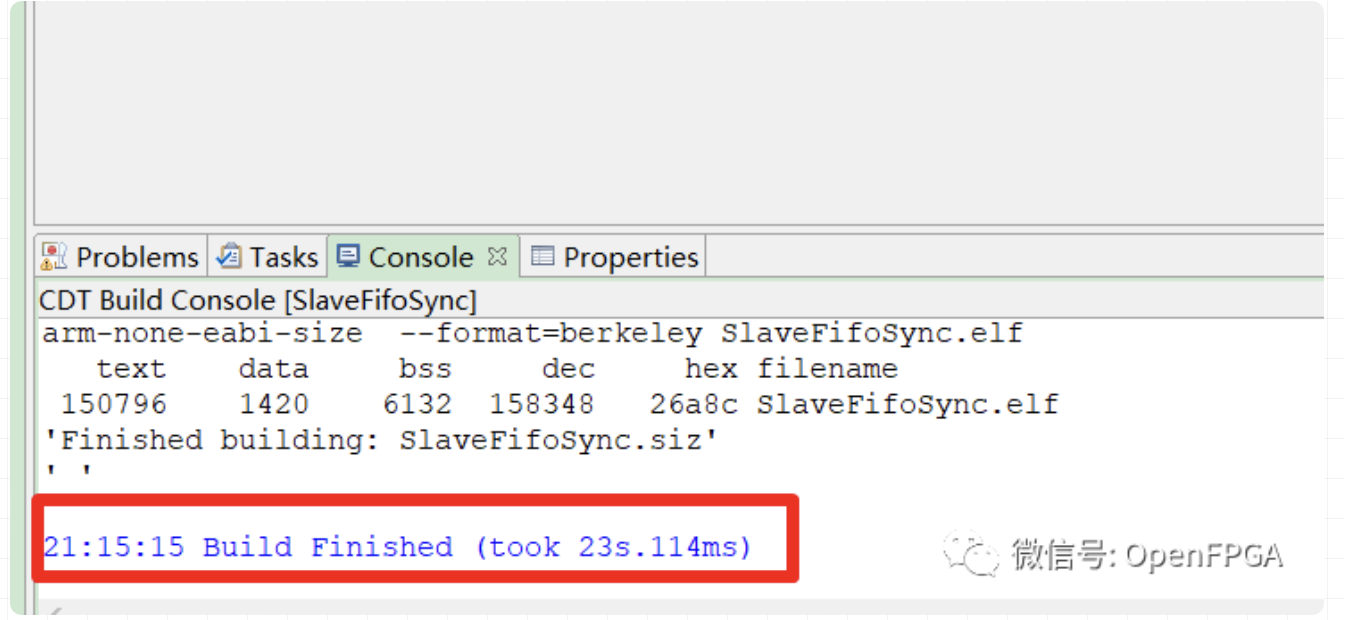

在Console下会打印出编译完成的通知。

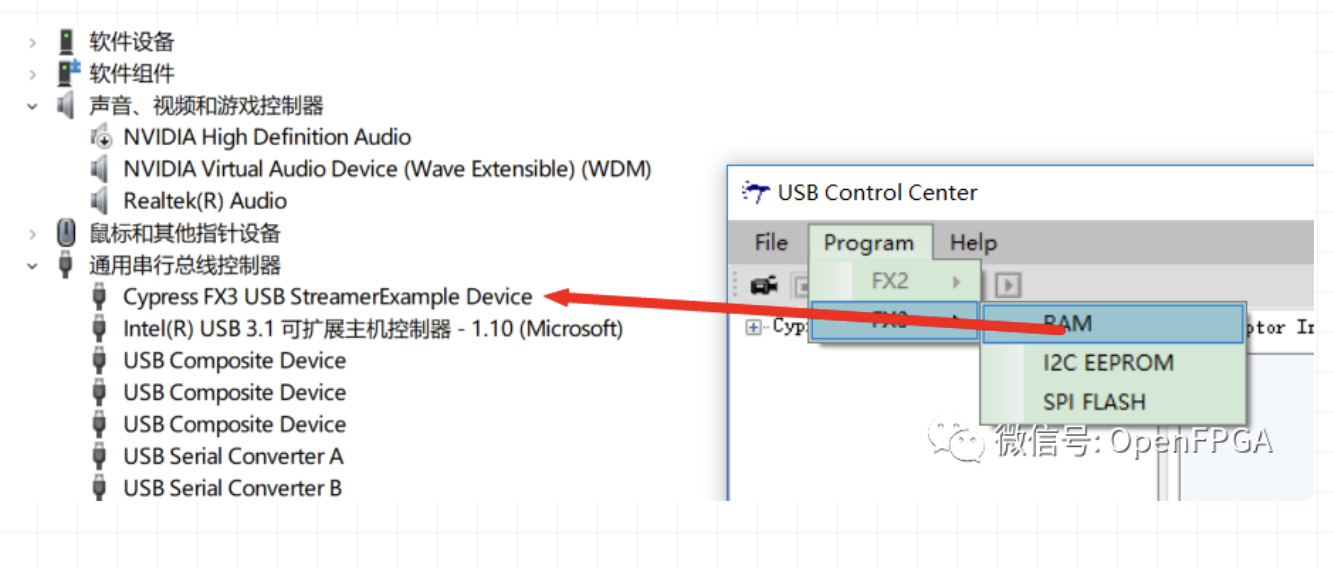

打开 USB Control Center, 在 USB Boot 方式下, 下载 SlaveFifoSync/ Debug/SlaveFifoSync.img 文件到 FX3 中。

步骤不赘述,同之前。

FPGA和FX3联合测试

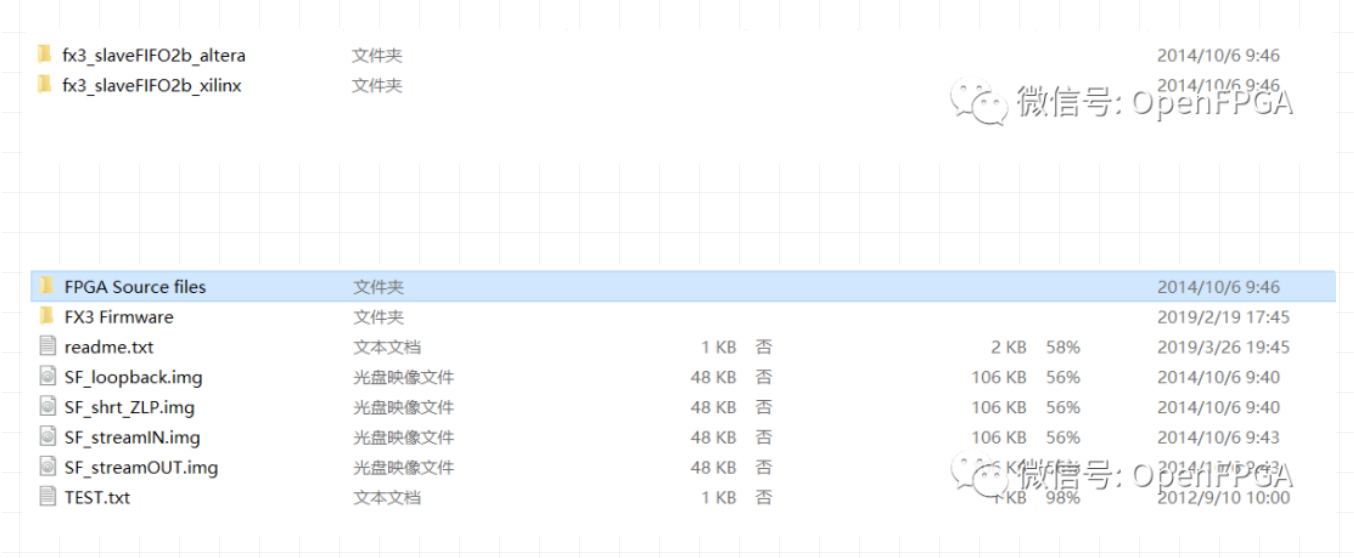

参考《AN65974\FPGA Source files》,里面有相应的固件和FPGA源程序。

FPGA端设计

参考官方历程《AN65974》

整个方案设计如下,因为回环设计所以需要将接收的数据回环到发送数据,因为设计到两个时钟域,所以回环采用FIFO设计,具体如下:

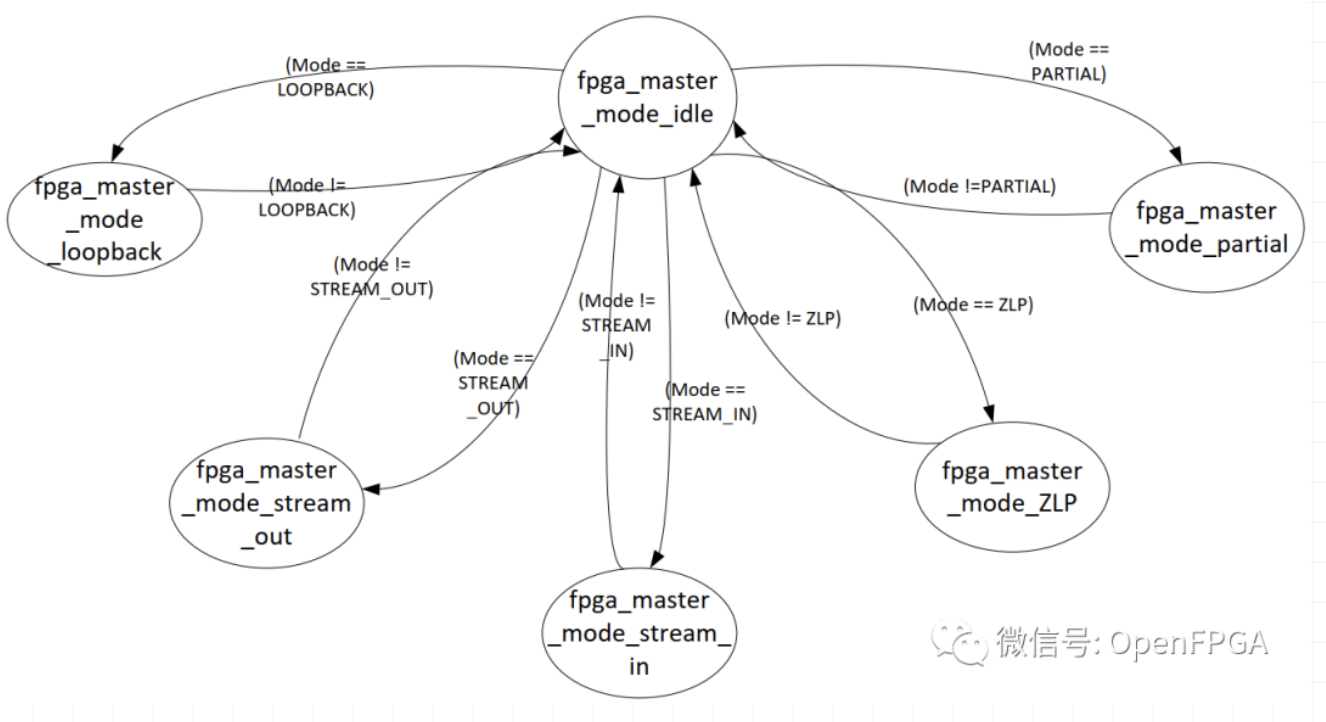

官方的历程里是个集合程序,包括四个方式:Loopback,Short Packet (Partial), Zero-length Packet, Stream IN, and Stream OUT transfers(回送、短数据包(局部)、零长度数据包、串流 IN 和串流 OUT 传输)。

程序设计如下:

每一个程序都有详细的设计状态机,这里就不一一截图了,大家可以看下《001-92219_AN65974_Designing_with_the_EZ-USB_FX3_Slave_FIFO_Interface_Chinese.pdf》中文版本,都是很简单的状态机,大家一定要花点时间去看一下,不仅能学习到状态机知识,还能学习到官方的程序设计。

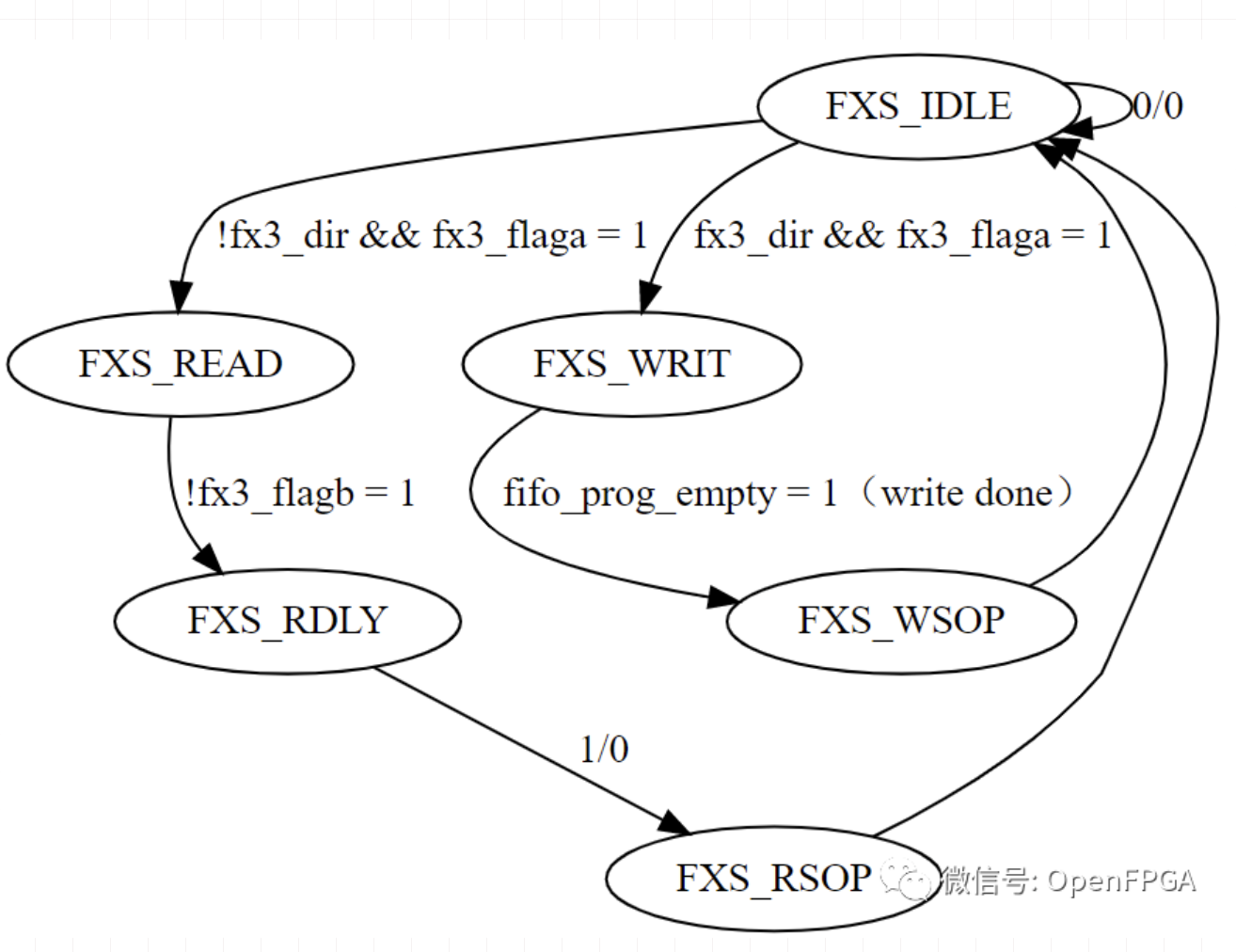

接下来我们将回环(官方称为回送),程序单独摘出来,形成一个工程,主要是抓取一下重要信息。

PS:回环的整个程序的设计思路就是:FX3 通过指示信号 flaga 告知 FPGA 有数据待读取, FPGA 端便通过 SlaveFIFO 接口读取 PC 端发送过来的数据缓存到 FPGA 内部的 FIFO 中, FPGA 在完成读取操作后, 发起一次 SlaveFIFO 的写人操作, 将接收到的数据通过 FX3 最终返回到 PC 端。

状态机如下:

根据上述状态机编写程序后,生成到BIT流文件,不着急下载,首先要下载FX3的固件,然后在下载FPGA程序(要保证先后顺序)。

PS:这里出现一个小BUG,就是硬件设计时没有将FX3复位上拉,直接拉到FPGA管教上,这样FPGA在下载程序时管教是高阻状态,会将FX3处于不定状态,这样就没办法先下载FX3固件了,这里需要注意一下,对于一些FPGA外围器件,一些重要的输入引脚(时钟、复位等),一定要有一个固定的初始状态,不要让这些器件处于不定状态,很容易造成意向不到的情况,本次飞线即解决。

固件下载

这里使用上一节产生的固件,流程和方式不变,查看以前的下载方式即可。

FPGA和FX3联合调试

在上一步基础上,下载 .bit 和 debug.ltx(ILA Core)到FPGA内。

将 fx3_slcs_n 信号添加到 Trigger Setup 界面中, 并设置触发条件为下降沿( = = F)有效,然后等待触发即可。

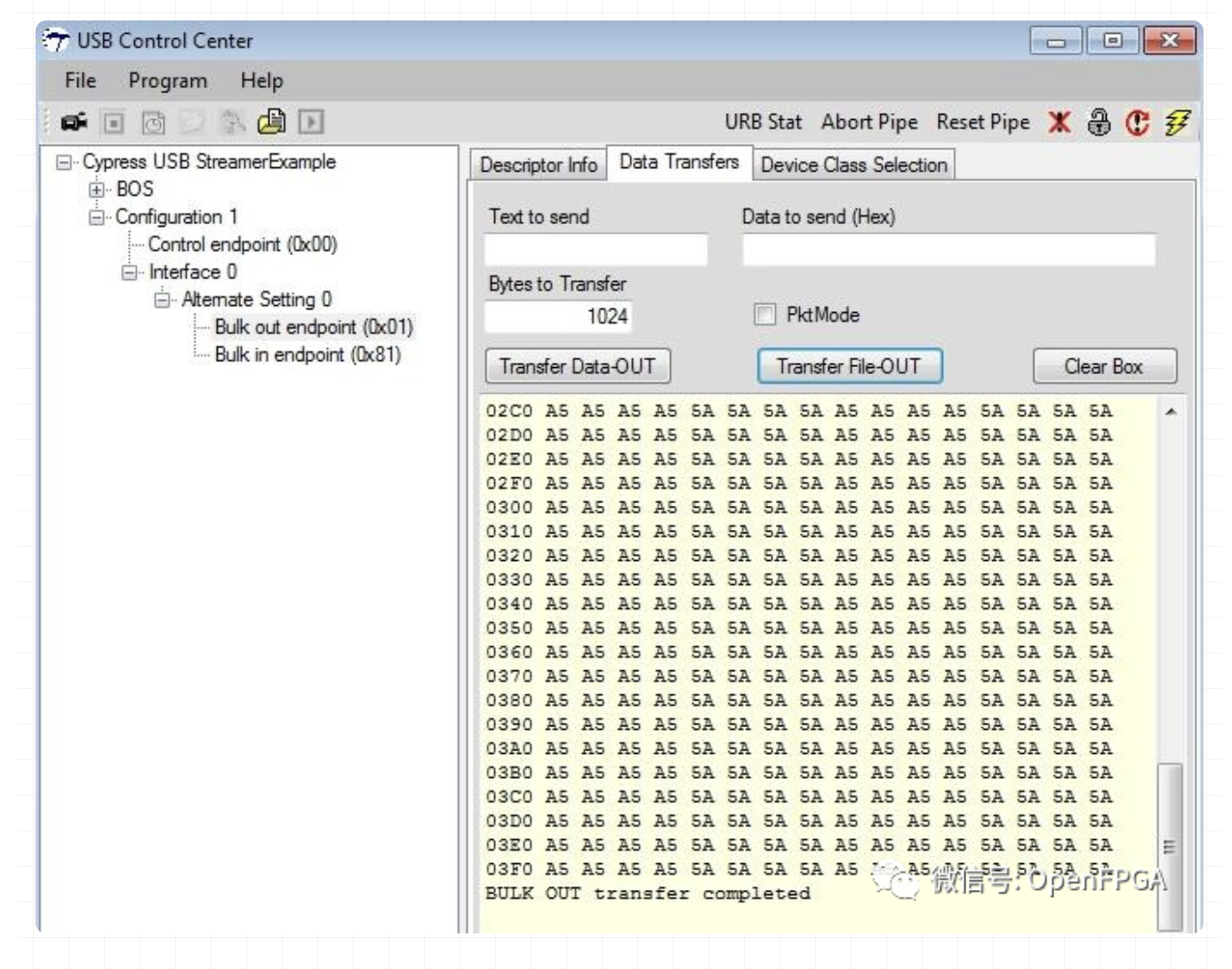

使用 Control Center 工具启动传输过程。首先, 从 USB 主机启动一个 BULK OUT 传输。在 Control Center 中选择 BULK OUT endpoint 项, 然后点击 Transfer File-OUT 按键。

浏览并选择包含需要传输的数据的文件。在附件中,在 Loopback 文件夹中找到TEST.txt 文件。该文件包含一个以交替方式发送“0xA5A5A5A5 0x5A5A5A5A” 的数据图案。双击选择该文件,然后发送数据。

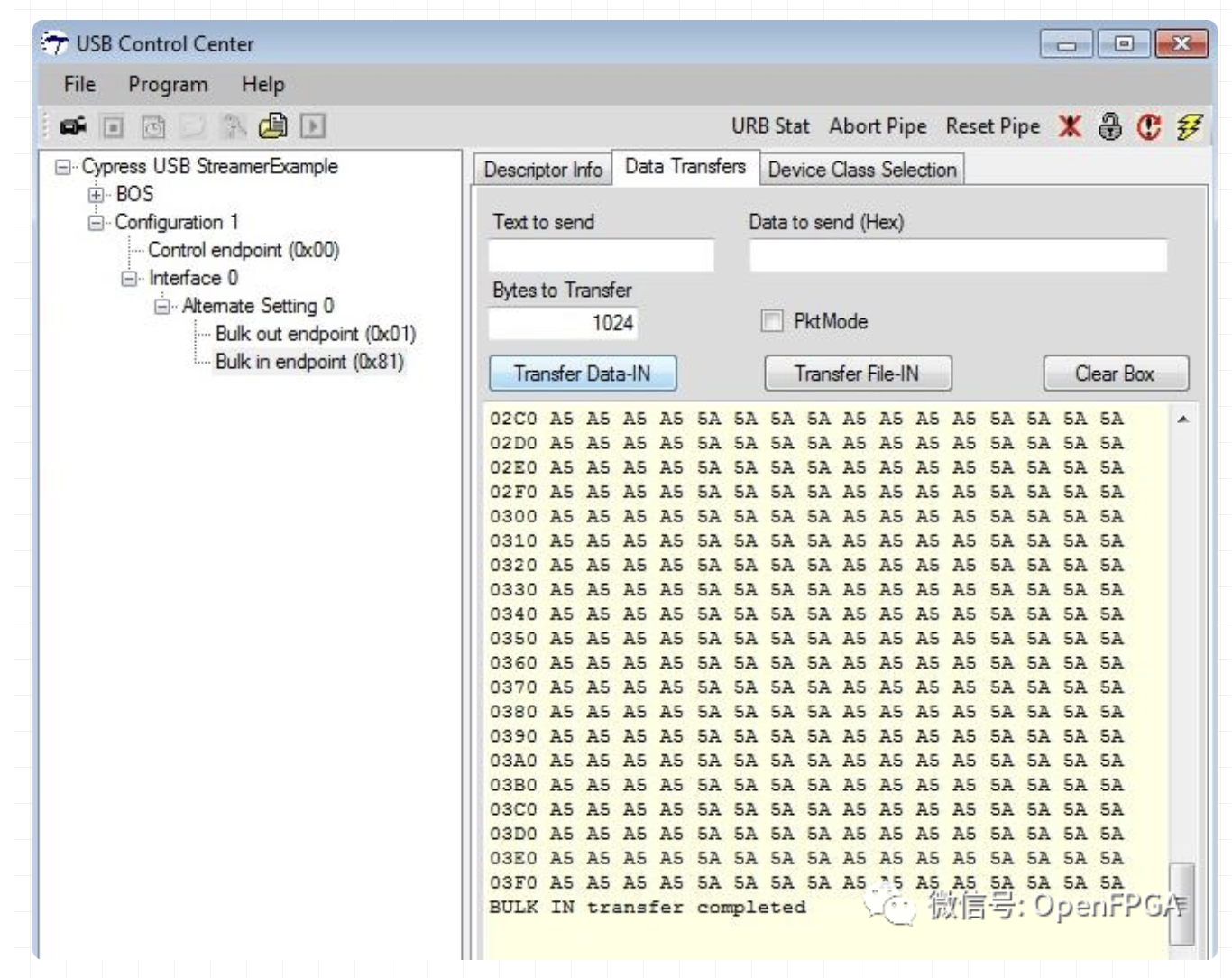

在 Control Center 中选择 BULK IN endpoint 项,并点击 TransferData-IN 按键。先前写入的数据将被读取。

同时也可以在ILA窗口读取到相应的数据,结合发送数据可以查看一下我们设计的时序对不对。

StreamOUT 实例、Streamer 中查看数据吞吐量等测试

《AN65974 - Designing with the EZ-USB® FX3™ Slave FIFO Interface》这个文件夹下。

上面的测试就不一一展示了,具体可以查看上面的官方文档,每一个步骤都有详细的说明和图示说明。

总结

最新的链接及相关代码都可以在下列链接中找到,同时wiki上有最新的文章:

❝

https://github.com/suisuisi/FPGAandUSB3.0

❞

❝

https://github.com/suisuisi/FPGAandUSB3.0/wiki

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。