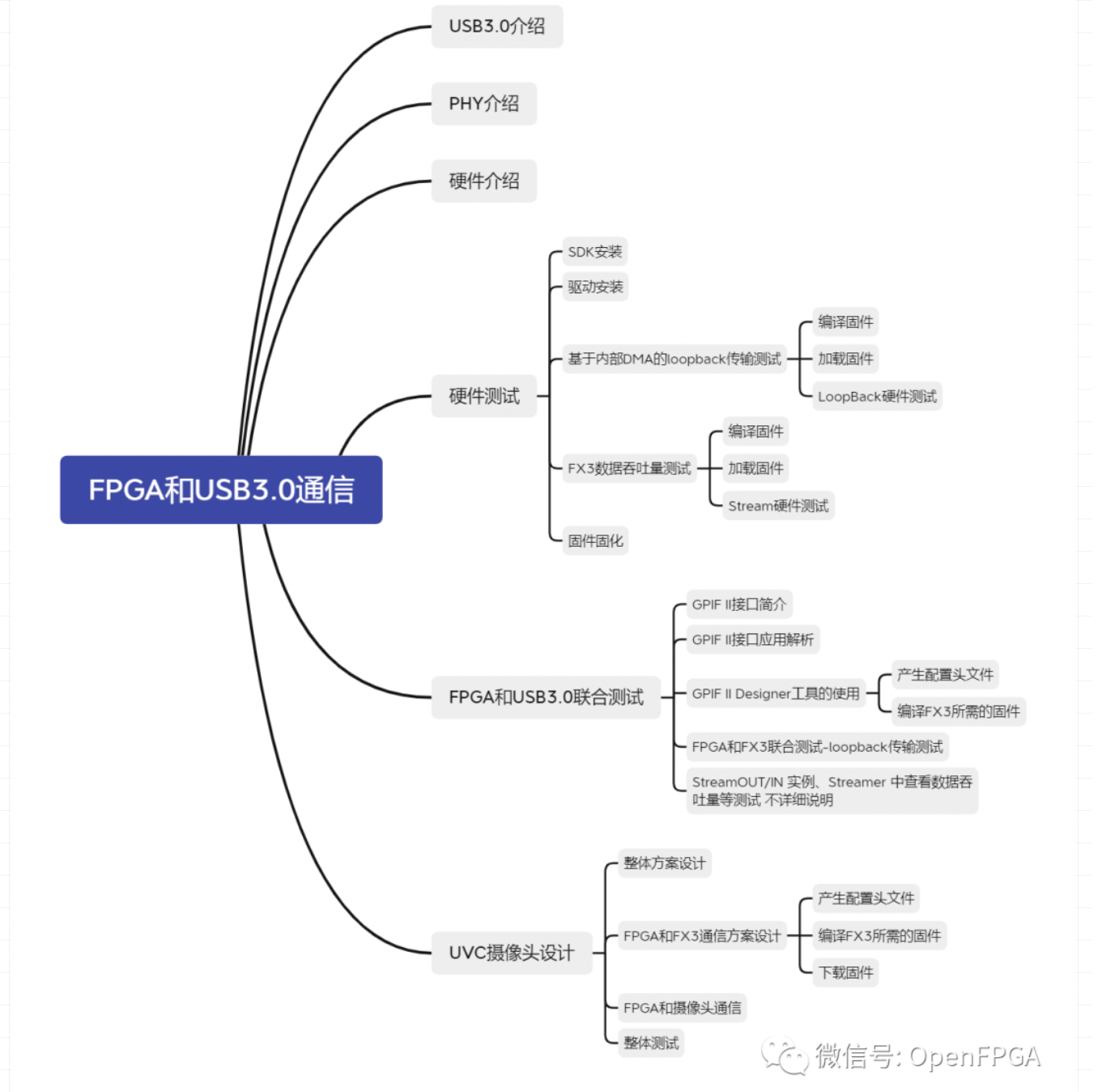

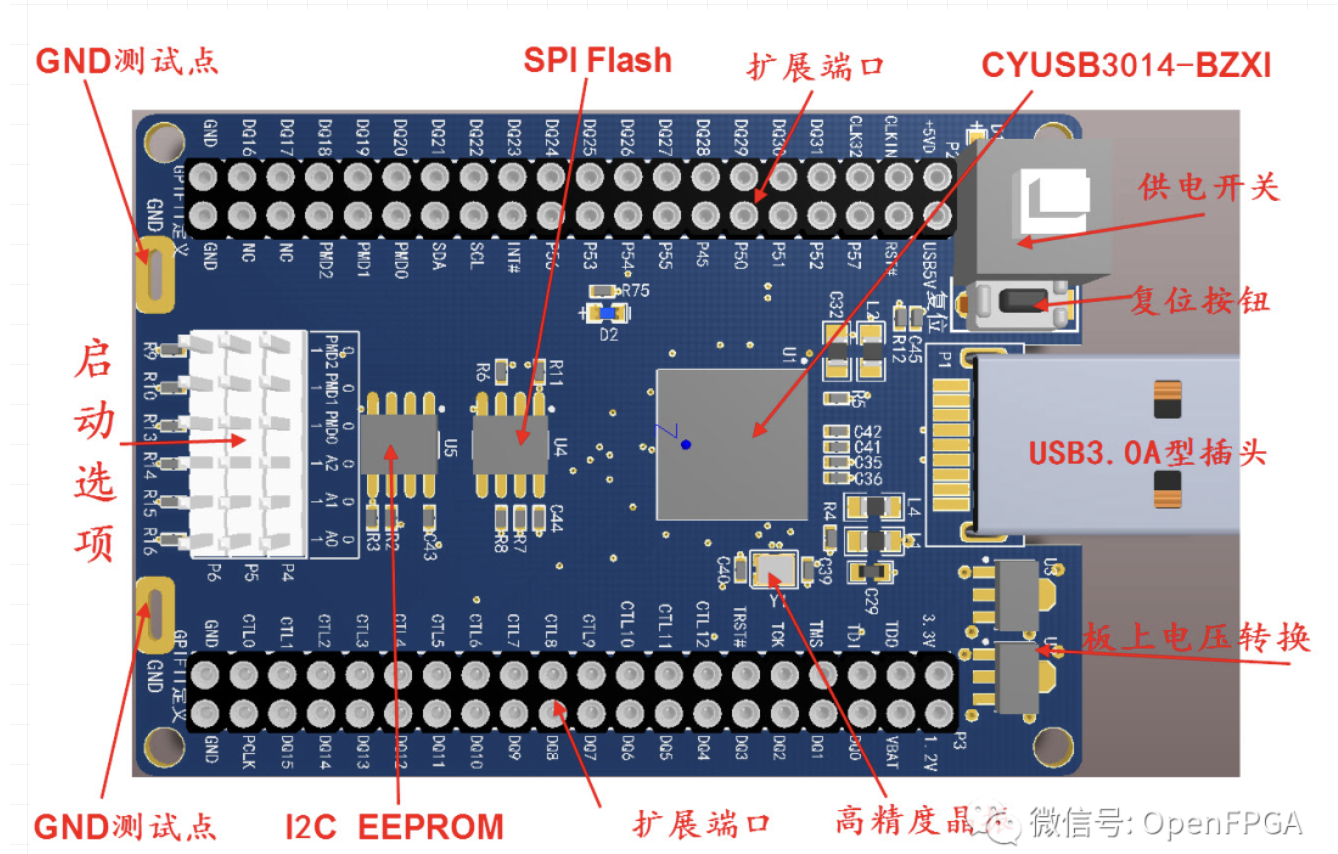

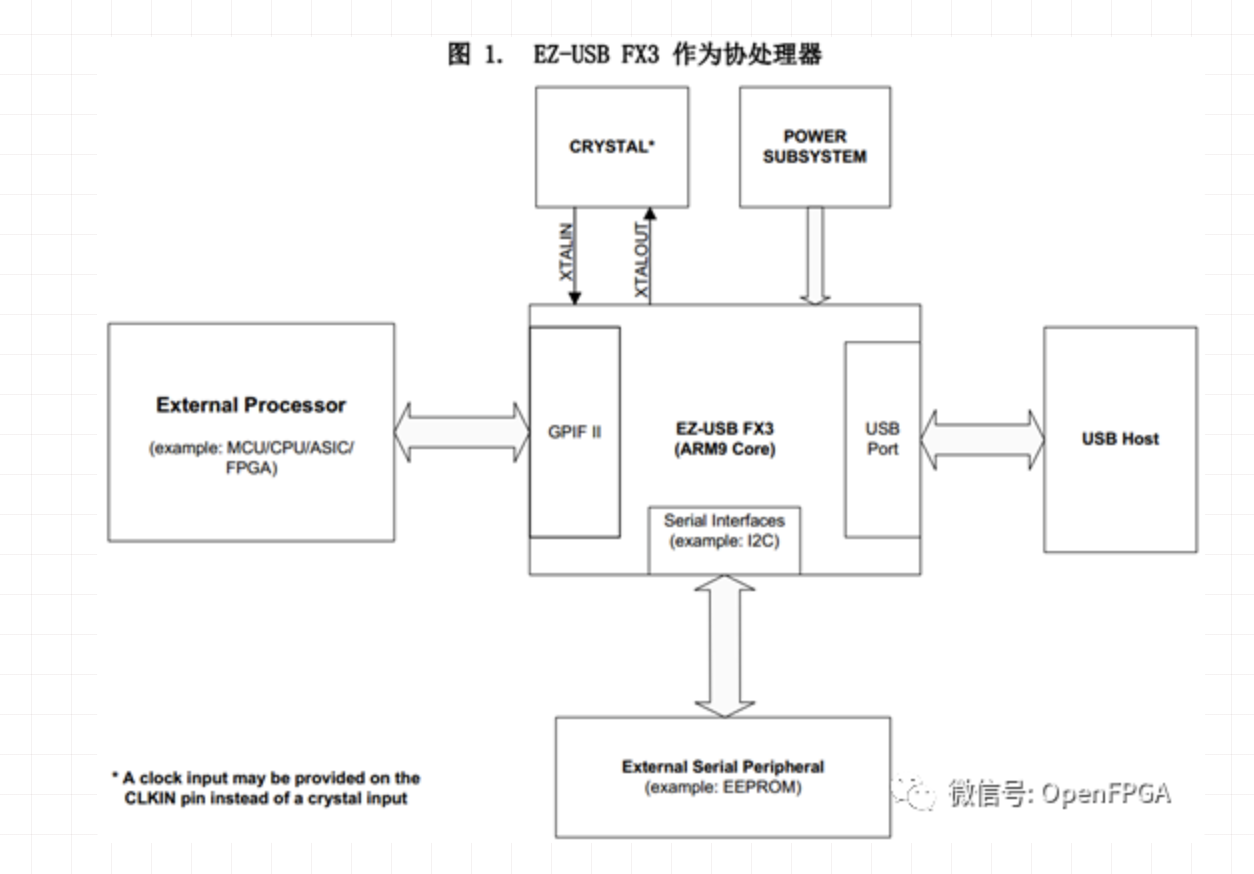

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下称 FX3),该芯片是标准的USB3.0 PHY,可以大大简化使用USB通信时FPGA的设计,主需要使用状态机进行FIFO的读写控制即可,同时该芯片还具有ARM核+I2S、I2C、SPI、UART等接口,大大增加了该芯片的使用范围。

FX3应用中后半部分测试已经完成暨FX3和PC之间的通信:

接下来就是通过FX3这个“桥梁”实现FPGA与PC之间的通信。

在此之前我们还需要打通FPGA和FX3之间的通信,通过前面的介绍我们知道FX3和FPGA之间是可以通过一个GPIF II的接口进行连接的,所以我们首先介绍一下这个接口(主要是时序相关),然后再进行下面的操作。

GPIF II接口简介

FX3具有完全可配置的并行通用可编程接口,称为GPIF II,可连接到任何处理器、ASIC或FPGA。GPIF II是FX2LP(Cypress的USB 2.0旗舰产品)中GPIF的增强版™。GPIF II的一个最广实现是从FIFO接口,设计连接到FX3的外部设备对FX3中的FIFO进行寻址、读取或写入数据的应用。

GPIF II是一种可编程状态机,支持灵活的接口,在工业标准或专有接口中可以作为主接口或从接口。并行和串行接口都可以用GPIF II实现。GPIF II提供以下功能:

- 作为主设备或从设备使用

- 提供256个固件可编程状态

- 支持8位、16位、24位和32位并行数据总线

- 支持高达100 MHz的接口频率

- 当使用32位数据总线时,支持14个可配置控制引脚;所有控制引脚可以是输入/输出或双向

- 当使用16/8位数据总线时,支持16个可配置的控制引脚;所有控制引脚可以是输入/输出或双向

FIFO接口介绍及应用

在FX3这边利用FIFO进行通信,SDK部分提供相应的驱动,我们先大致了解一下,后续会有详细的设计说明:

应用说明

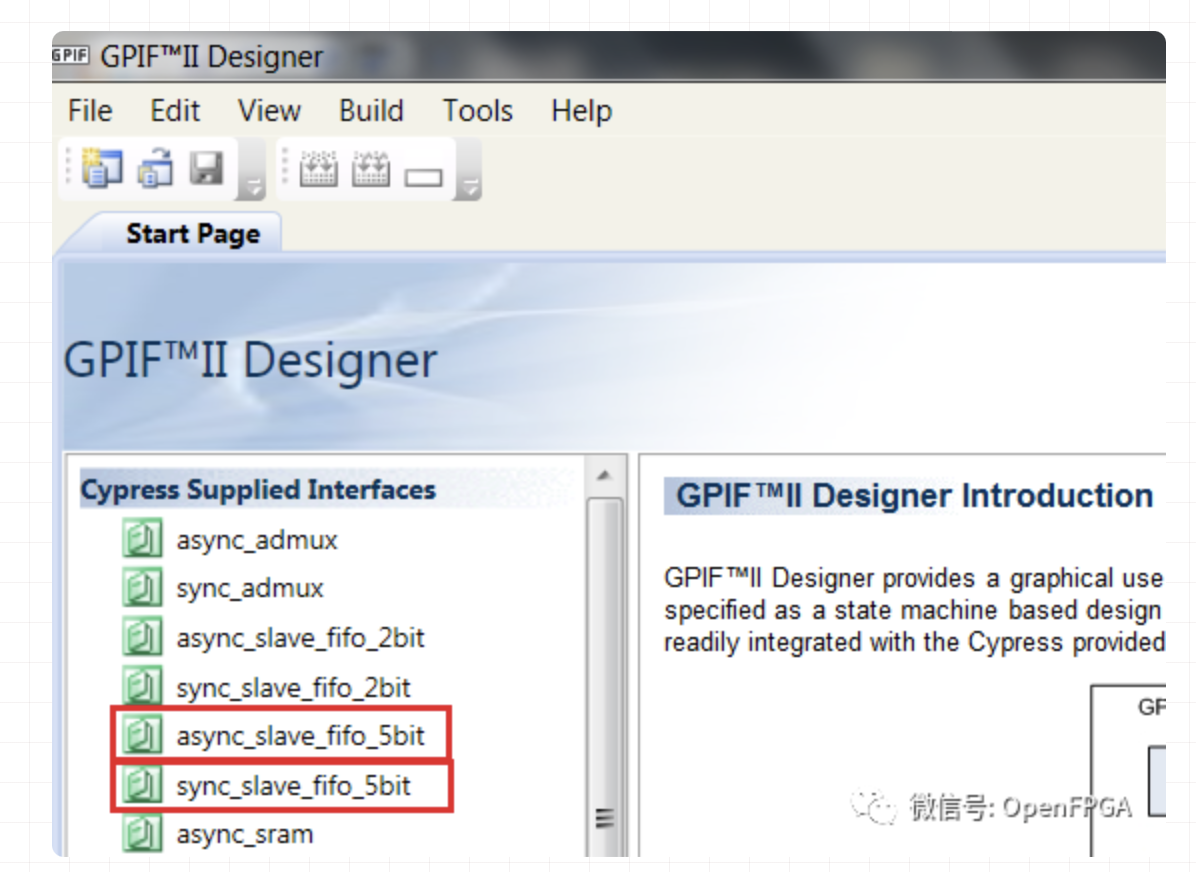

FX3 SDK的firmware/slavefifo_examples文件夹中提供了用于5位异步从FIFO和5位同步从FIFO的FX3固件

- async_slave_fifo_5bit:这是带有5位地址总线的异步从fifo接口的实现。

- sync_slave_fifo_5bit:这是带有5位地址总线的同步从fifo接口的实现。

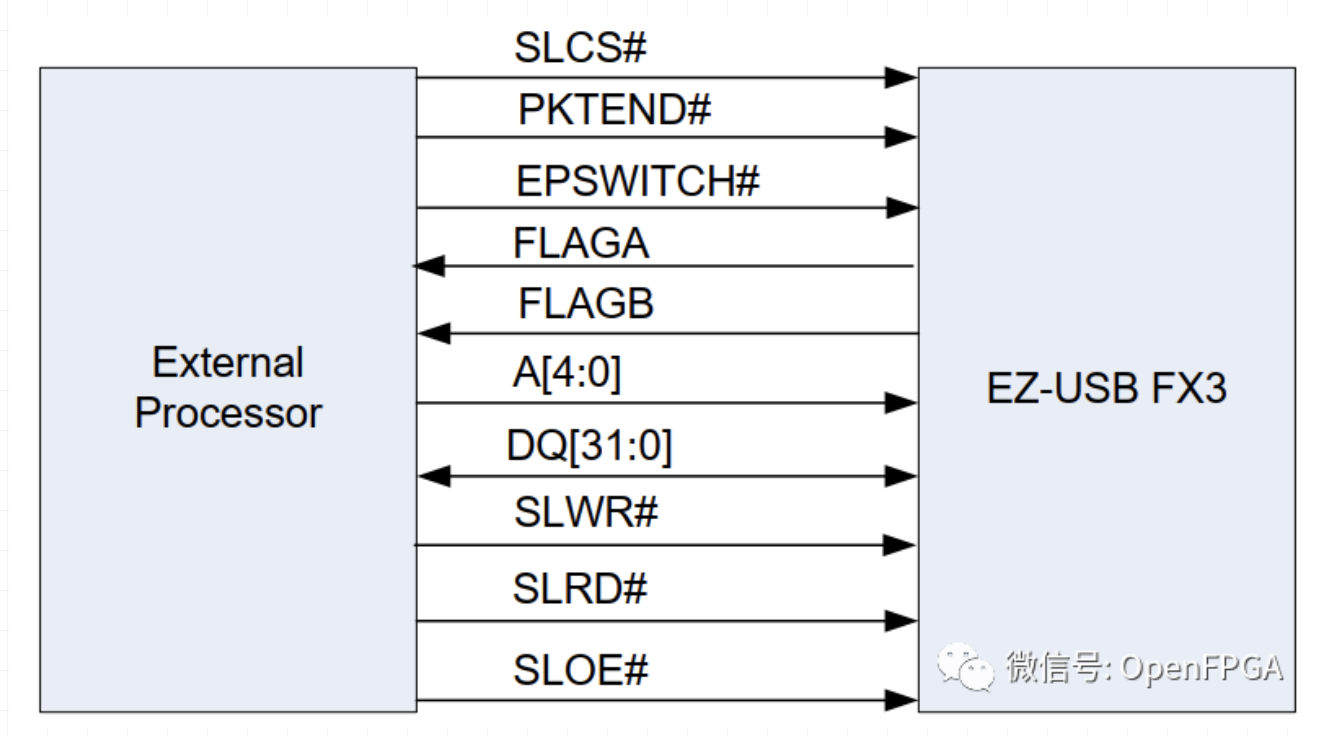

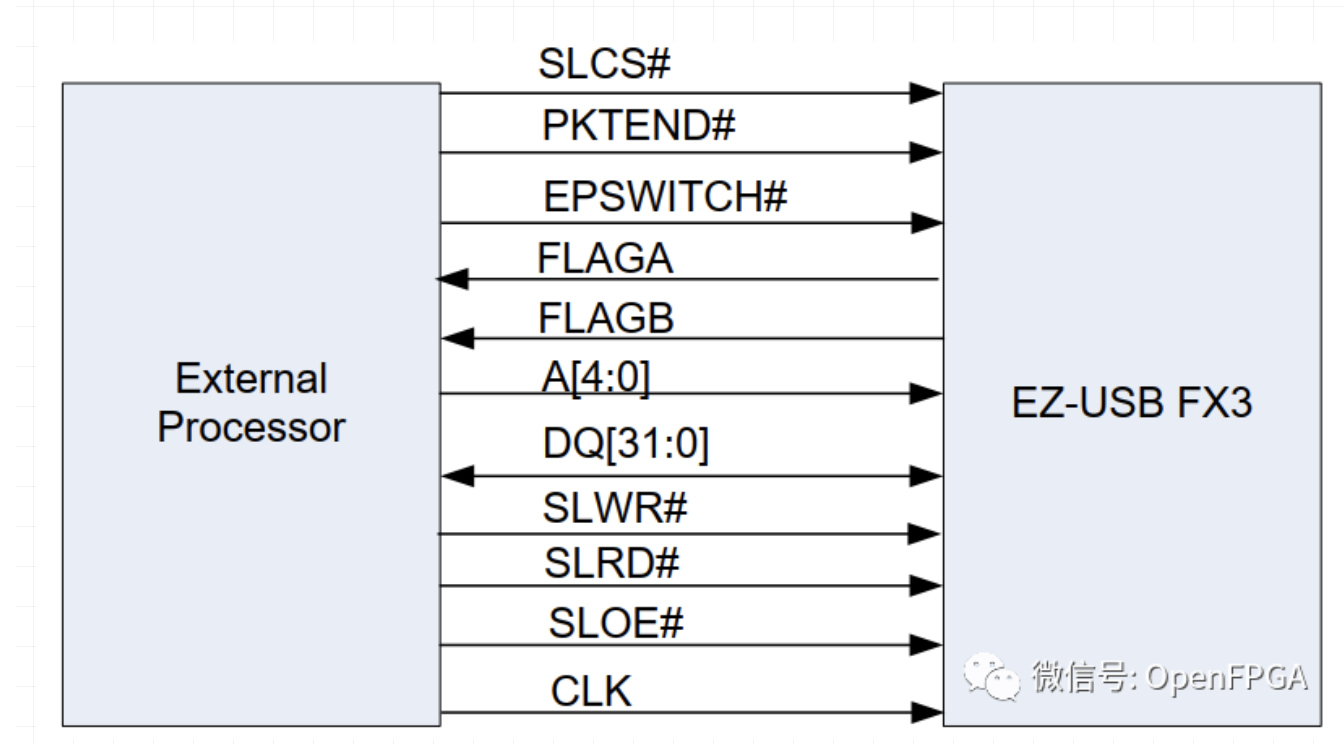

下面是两种应用的框图:

Asynchronous Slave FIFO Interface Diagram

Synchronous Slave FIFO Interface Diagram

带有两条地址线的同步从FIFO接口支持访问多达四个插槽。如果需要访问四个以上的插槽,则应使用具有五条地址线的同步从属FIFO接口。除了额外的地址线外,此接口还有一个名为“EPSWITCH#”的信号。由于用于此目的的管脚较多,可用作标志的管脚较少,因此需要将该标志配置为当前线程标志。

使用具有五条地址线的同步从属FIFO接口时会产生额外的延迟:

- 从地址到标志有效状态的两个周期延迟在每次传输开始时产生。

- 无论何时切换套接字地址,都会产生多个延迟周期来完成套接字切换。

由于延迟增加和额外的接口协议要求,建议仅当应用程序需要访问四个以上的GPIF II插槽时,才使用具有五条地址线的同步从属FIFO接口。

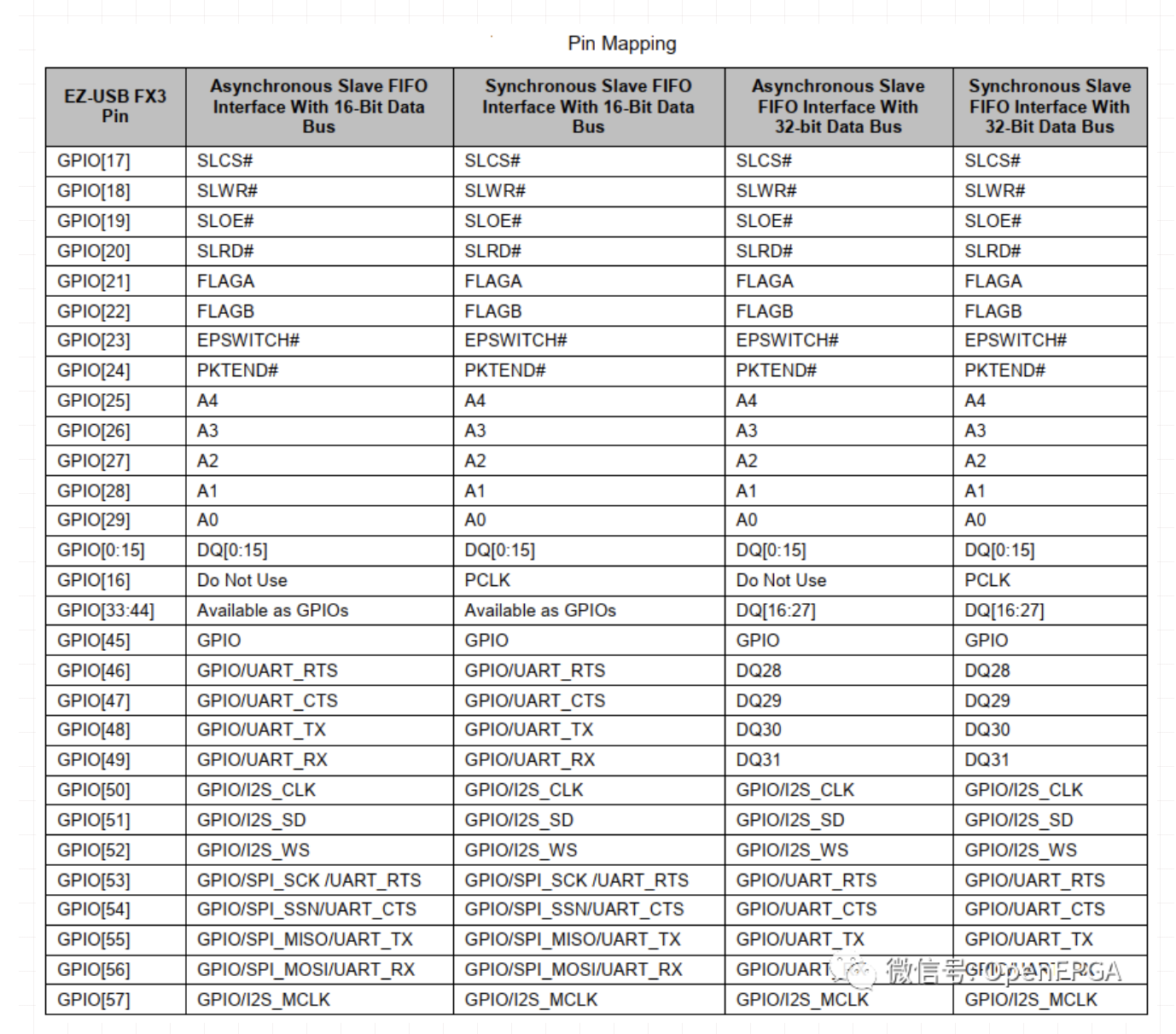

引脚映射

下表显示了SDK中从FIFO描述的引脚映射。它还显示了GPIF II配置为从FIFO接口时可用的GPIO引脚和其他串行接口(UART、SPI和I2S)

异步FIFO读写时序

外部处理器或设备(作为接口主设备)可以对FX3的内部FIFO缓冲区执行单周期或突发数据访问。在断言读或写选通之前,外部设备在FIFO ADDR线上显示5位地址(带或不带EPSWITCH#)。FX3断言或取消断言标志信号,以指示缓冲区的空/满状态。

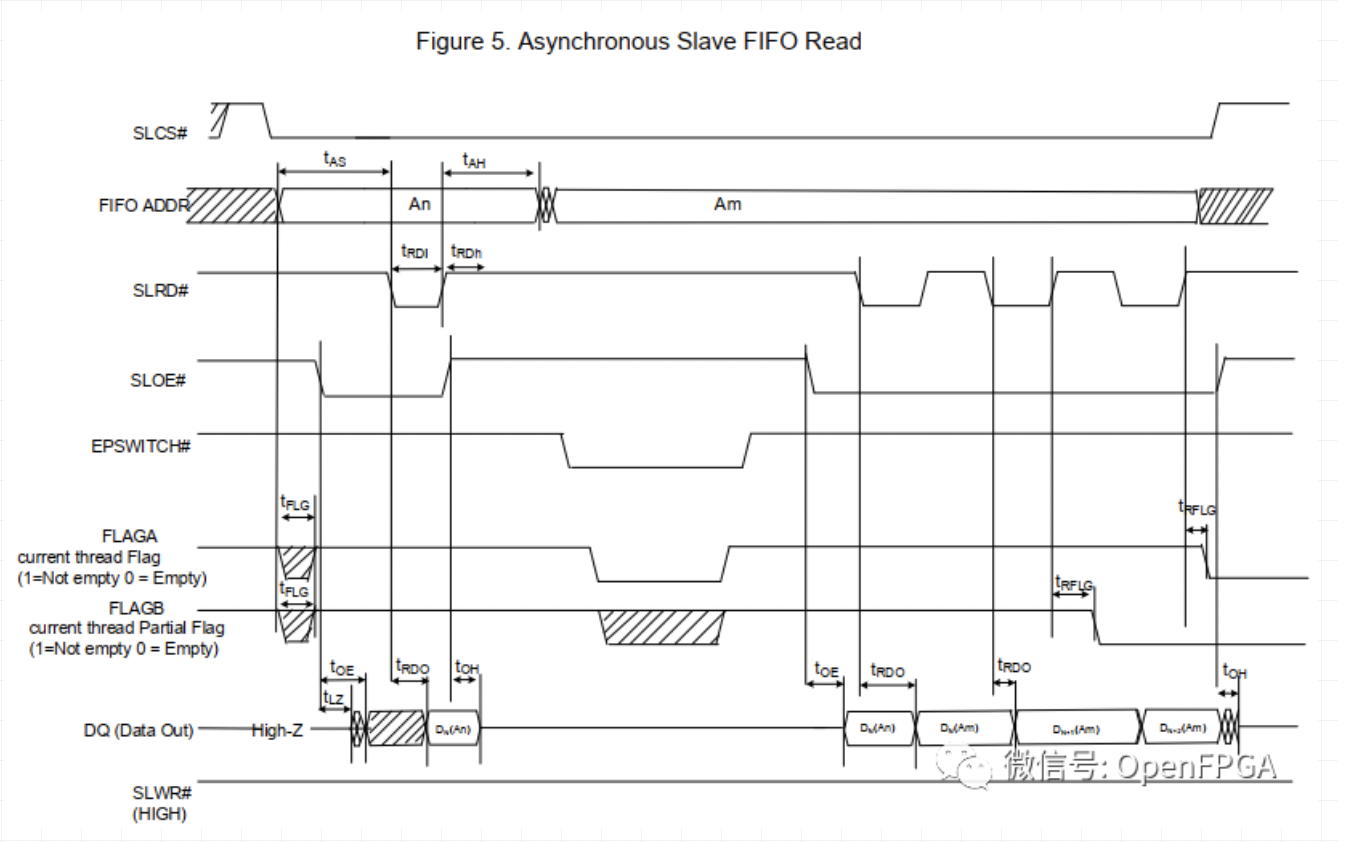

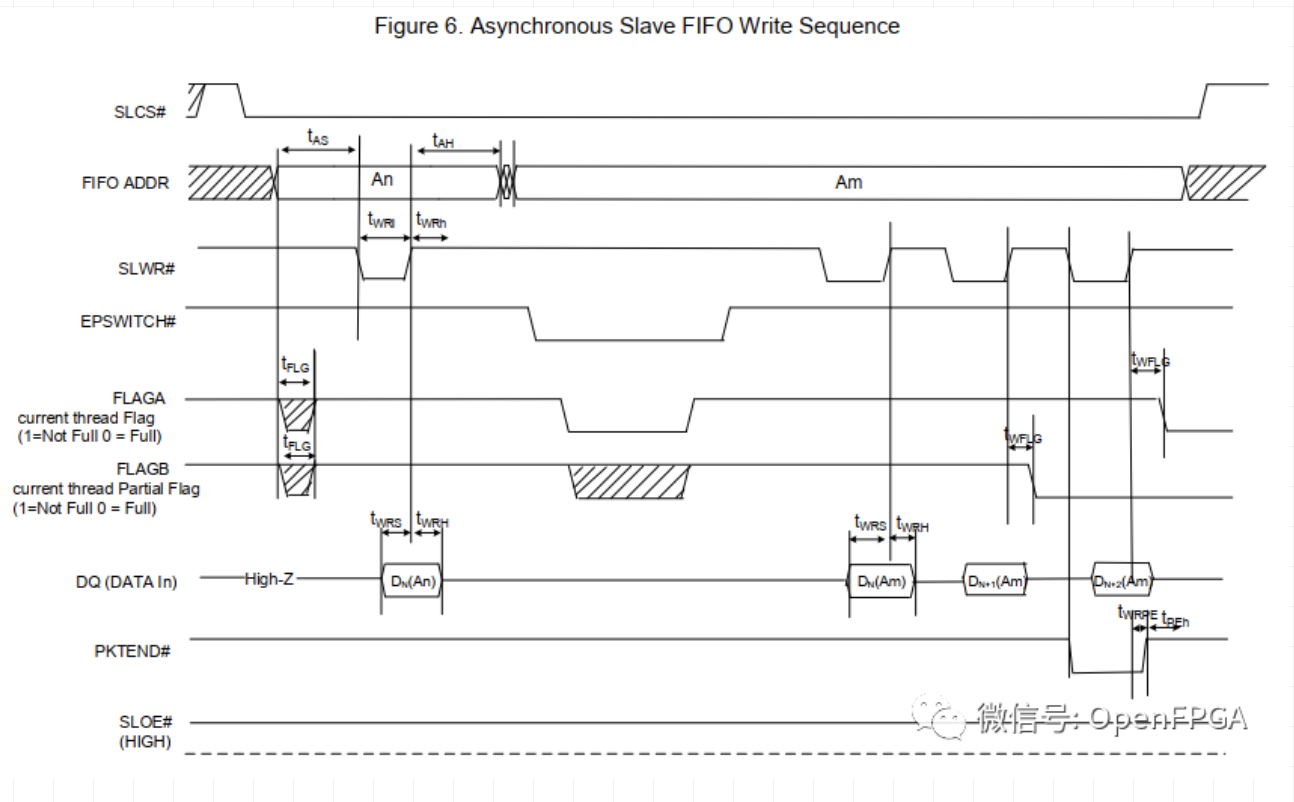

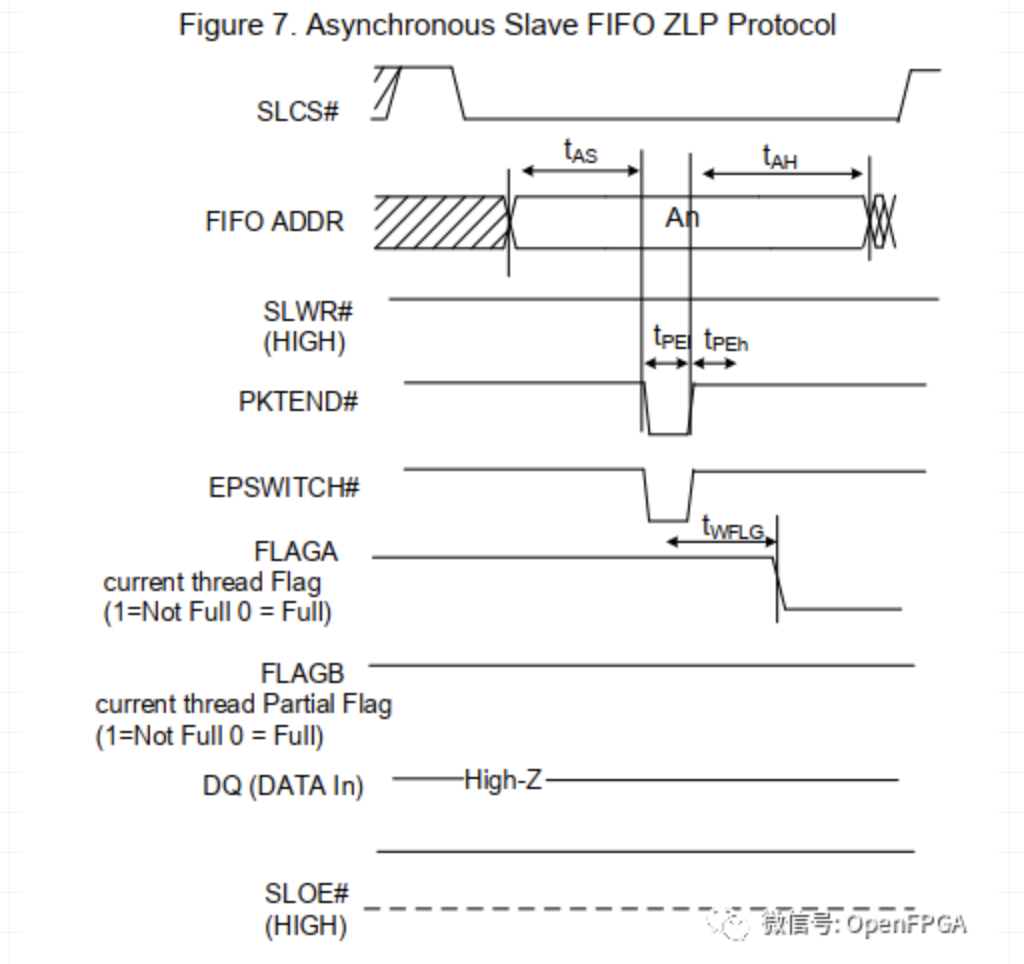

图5显示了异步从FIFO读取访问的时序和顺序。图6显示了异步从FIFO写入访问的时序和顺序。图7显示了用于异步从FIFO协议的ZLP协议。

从异步从FIFO接口执行读取的顺序如下:

- FIFO地址稳定,SLCS#信号被选中。

- 选中EPSWITCH#(根据地址映射中使用EPSWITCH#信号的讨论),并等待标志的有效状态(FLAGA变为1,表示DMA缓冲区中的数据可用性),然后解除对其的断言。

- 选中SLOE#,从而驱动数据总线。

- SLRD#被选中。

- 来自FIFO的数据在SLRD#断言后驱动。从SLRD#下降沿传播tRDO延迟后,此数据有效。

- 在SLRD#的取消赋值时,FIFO指针递增。

在图5中,数据N(DN)是从FIFO读取的第一个有效数据。要使数据在读取周期内出现在数据总线上,SLOE#必须处于断言状态。SLRD和SLOE也可以并列。

突发读取遵循相同的事件序列。请注意,在突发读取模式下,在SLOE#断言期间,数据总线处于受驱动状态(数据由先前寻址的FIFO驱动)。在断言SLRD#之后,来自FIFO的数据在数据总线上被驱动(SLOE#也必须被断言)。先入先出指针在SLRD#取消赋值后递增。

对同步从FIFO接口执行写入的顺序如下。

- FIFO地址是稳定的,SLCS#被断言。

- expndtw-1,并将epsrt的状态设为“有效”,表示缓冲区的可用性。

- SLWR#被断言。SLC必须与SLWR一起断言,或在断言SLWR之前断言。

- 在SLWR#的拆卸边缘之前,总线TWR上必须存在数据。

- SLWR的解除断言#导致数据从数据总线写入FIFO,然后FIFO指针递增。

- FIFO标志在SLWR的解除装配边缘tWFLG之后更新。

- 突发写入遵循相同的事件序列。请注意,在突发写入模式下,SLWR#解除断言后,数据写入FIFO,然后FIFO指针递增。

短包:可使用PKTEND#将短数据包提交到USB主机。外部设备或处理器的设计应确保PKTEND与数据的最后一个字以及与最后一个字对应的SLWR脉冲同时生效。在PKTEND#断言期间,FIFOADDR行必须保持不变。

零长度数据包:必须同时声明PKTEND#信号和EPSWITCH#信号才能提交ZLP。对于ZLP传输,不应断言SLWR,但应断言SLCS。这将导致正在寻址的套接字的第一个可用缓冲区以零字节的数据提交给使用者(通常是USB)。

FLAG使用:外部处理器监控流量控制的标志信号。标志信号是FX3输出,可配置为显示专用地址或当前地址的空、满和部分状态。

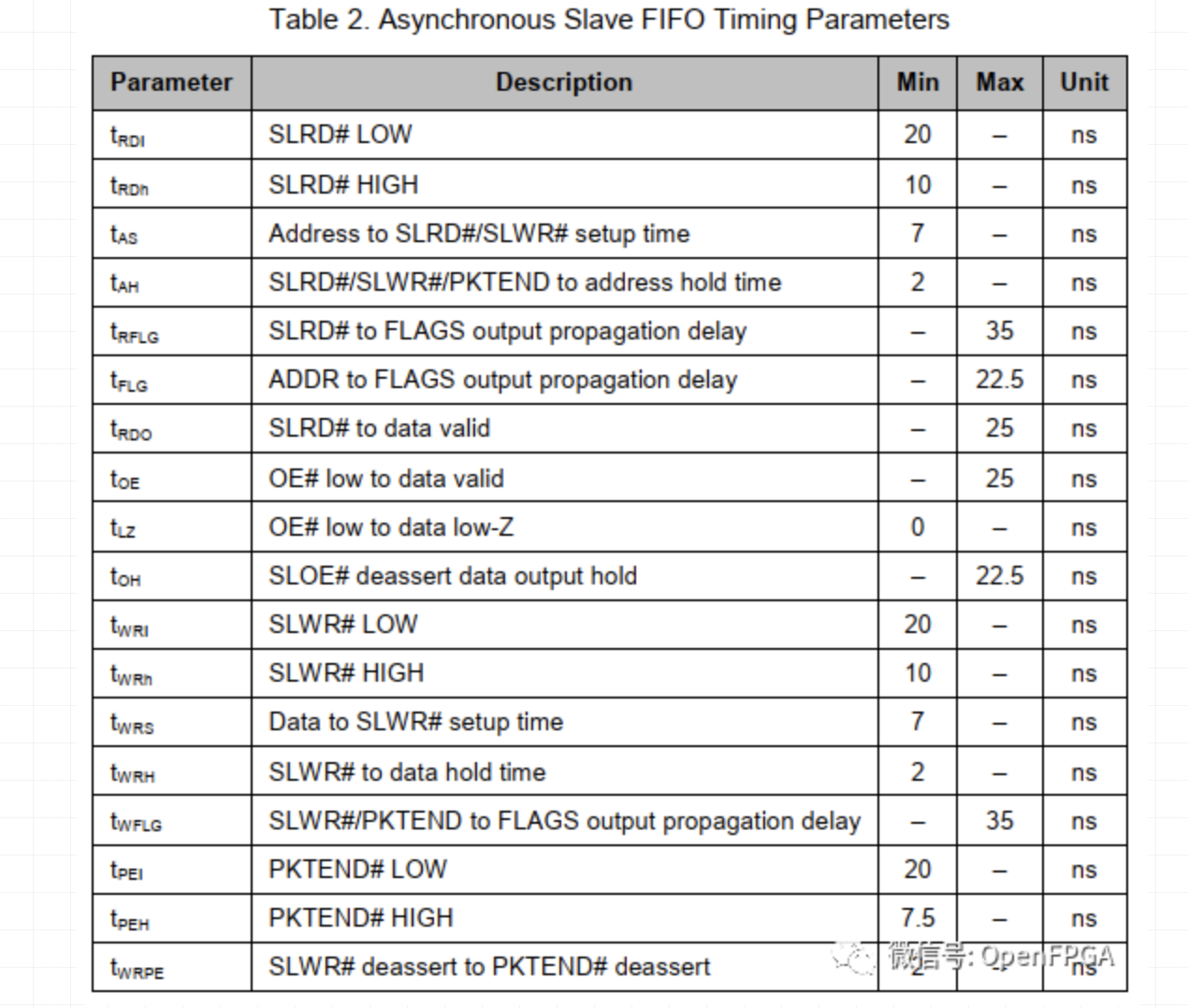

接口的时序详细说明:

同步FIFO读写时序

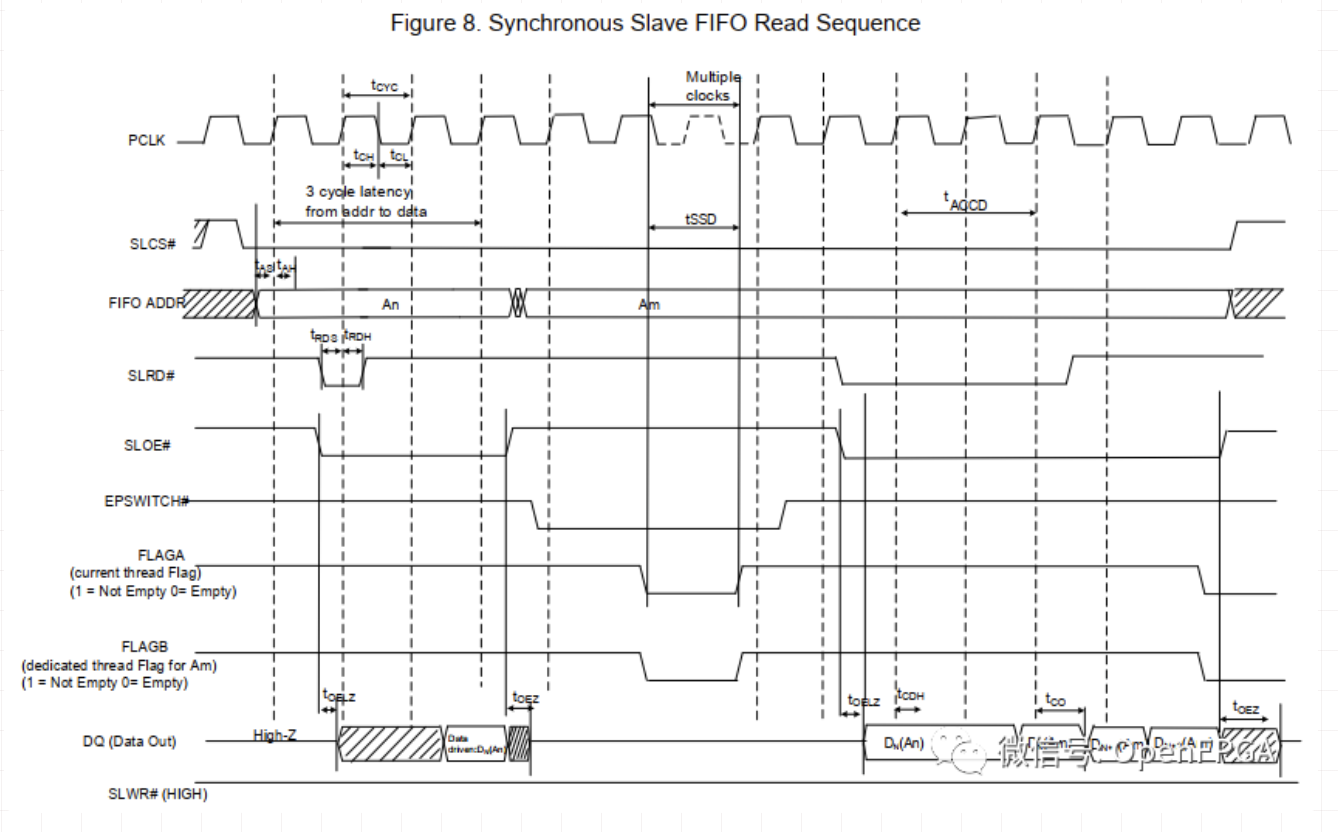

从同步从FIFO接口执行读取的顺序如下。

- FIFO地址是稳定的,SLCS#被断言(断言即激活或者使能)。

- 断言EPSWITCH#(根据地址映射中使用EPSWITCH#信号的讨论),并等待标志的有效状态(FLAGA变为1,表示DMA缓冲区中的数据可用性)并解除对其的断言。

- SLOE被断言。SLOE#是一个输出使能信号,其唯一功能是驱动数据总线。

- SLRD#被断言。

FIFO指针在PCLK的上升沿上更新,而SLRD#被断言。此操作启动从新寻址FIFO到数据总线的数据传播。tCO的传播延迟(从PCLK的上升沿测量)后,出现新的数据值。DN是从FIFO读取的第一个数据值。要驱动数据总线,还必须断言SLOE。

突发读取遵循相同的事件序列。请注意,对于突发模式,SLRD#和SLOE#在整个读取期间保持断言状态。当SLOE#被断言时,数据总线被驱动(使用来自先前寻址FIFO的数据)。对于PCLK的每个后续上升沿,当SLRD#被断言时,FIFO指针递增,下一个数据值被放置在数据总线上。

FLAG用法:标志信号由外部处理器监控,用于流量控制。标志信号是来自FX3的输出,可以配置为显示专用线程或正在寻址的当前线程的空/满/部分状态。

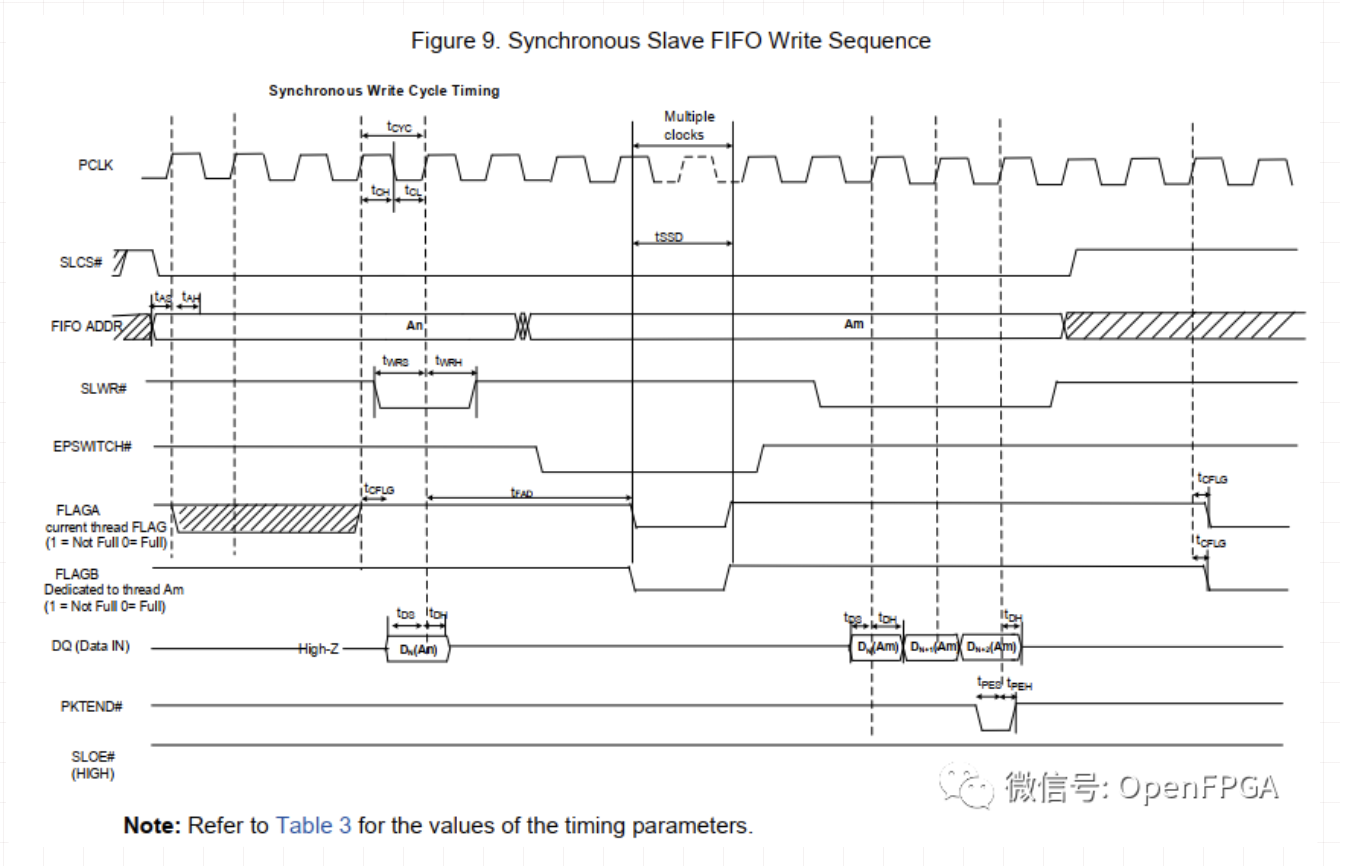

对同步从FIFO接口执行写入的顺序如下。

- FIFO地址稳定,信号SLCS#被断言。

- 断言EPSWITCH#(根据地址映射中使用EPSWITCH#信号的讨论),并等待标志变为有效(FLAGA变为1,表示DMA缓冲区的可用性)并解除对其的断言。

- 外部主机/外围设备将数据输出到数据总线上

- SLWR#被断言。

- 当SLWR#被断言时,数据被写入FIFO,并且在PCLK的上升沿上,FIFO指针递增。

- FIFO标志在时钟上升沿延迟t后更新。CFLG

突发写入遵循相同的事件序列。请注意,对于突发模式,SLWR#和SLCS#在突发写入的整个持续时间内保持断言状态。在突发写入模式下,在断言SLWR#后,数据总线上的值将写入PCLK每个上升沿上的FIFO。在PCLK的每个上升沿上更新FIFO指针。

短包:PKTEND#信号用于提交短数据包。如时序图所示,外部处理器必须断言PKTEND#信号以及要写入的数据的最后一个字(即,连同SLWR的断言以及数据总线上数据包的最后一个字)。还必须断言SLC。

在PKTEND#断言期间,FIFOADDR线路必须保持稳定。在PKTEND#with SLWR#断言时,GPIF II状态机将数据包解释为短数据包,并将其提交到USB接口。如果协议不要求传输任何短数据包,则PKTEND信号可能被拉高。请注意,在读取方向上,没有特定信号指示短数据包来自USB。外部主机必须监视空标志,以确定何时读取了所有数据。

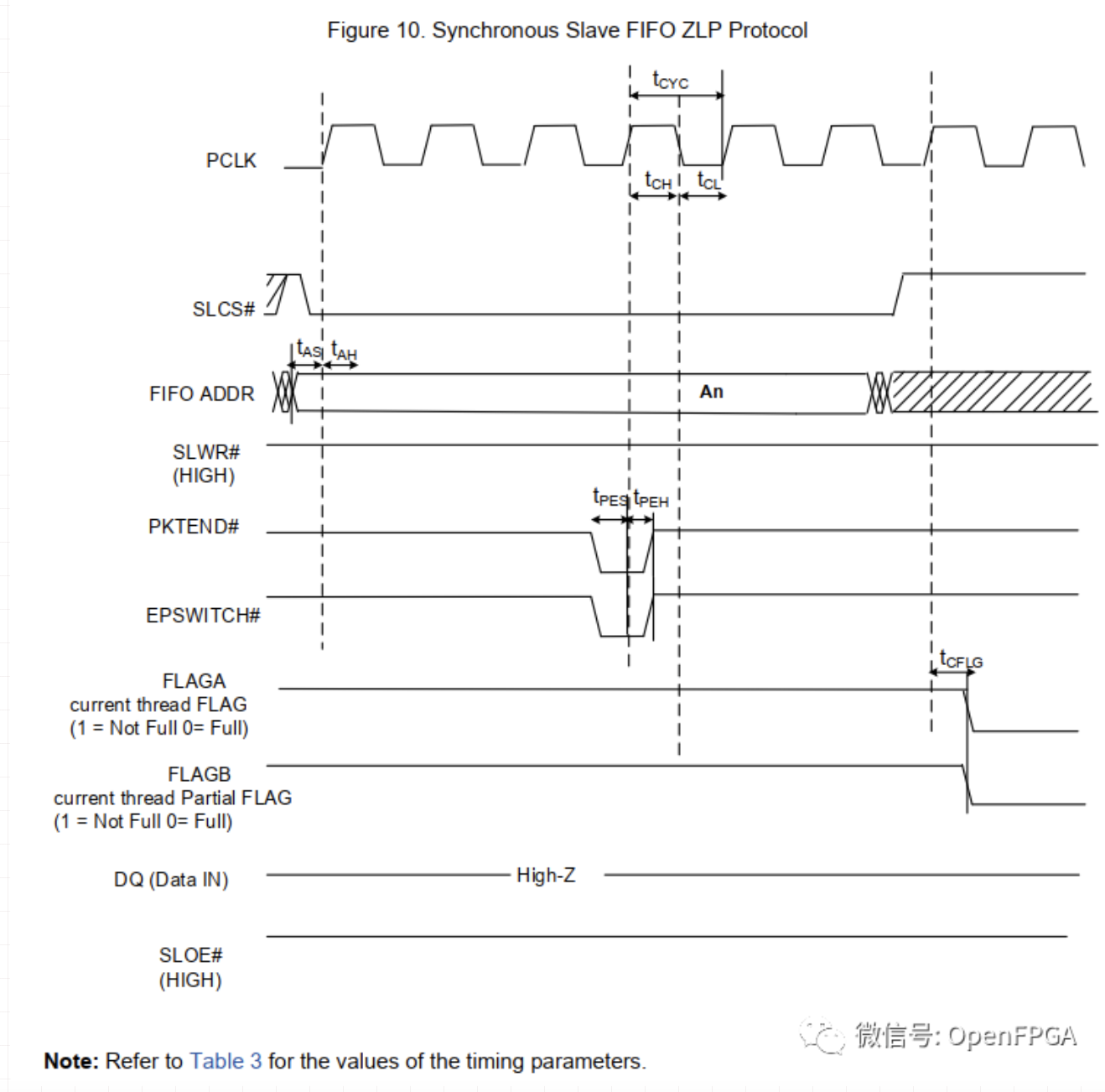

零长度数据包:必须同时声明PKTEND#信号和EPSWITCH#信号才能提交ZLP。对于ZLP传输,不应断言SLWR,但应断言SLCS。这将导致正在寻址的套接字的第一个可用缓冲区以零字节的数据提交给使用者(通常是USB)。

FLAG使用:外部处理器监控流量控制的标志信号。标志信号是FX3设备的输出,可配置为显示专用线程或正在寻址的当前线程的空/满/部分状态。

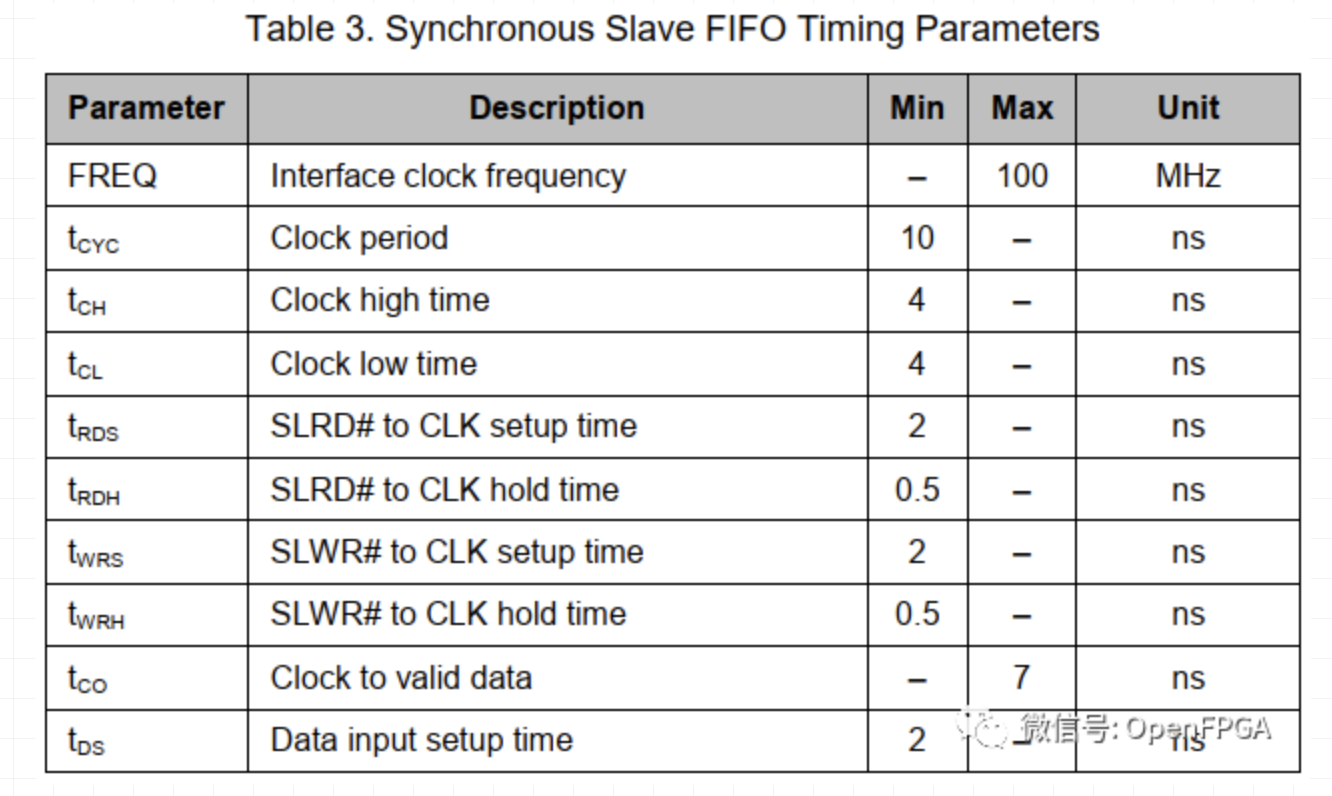

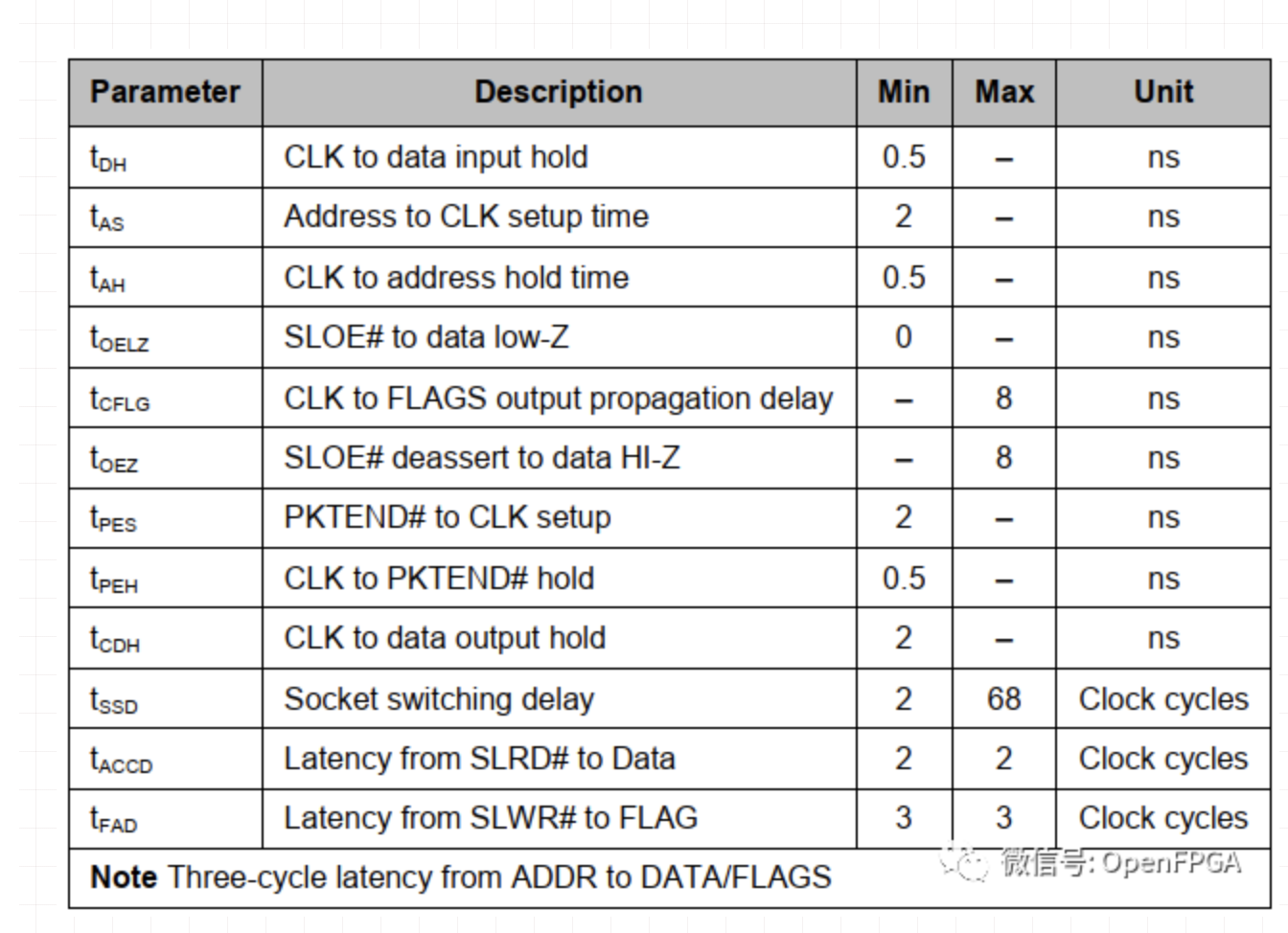

同步从FIFO定时参数

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。