AXI-Lite 自定义IP

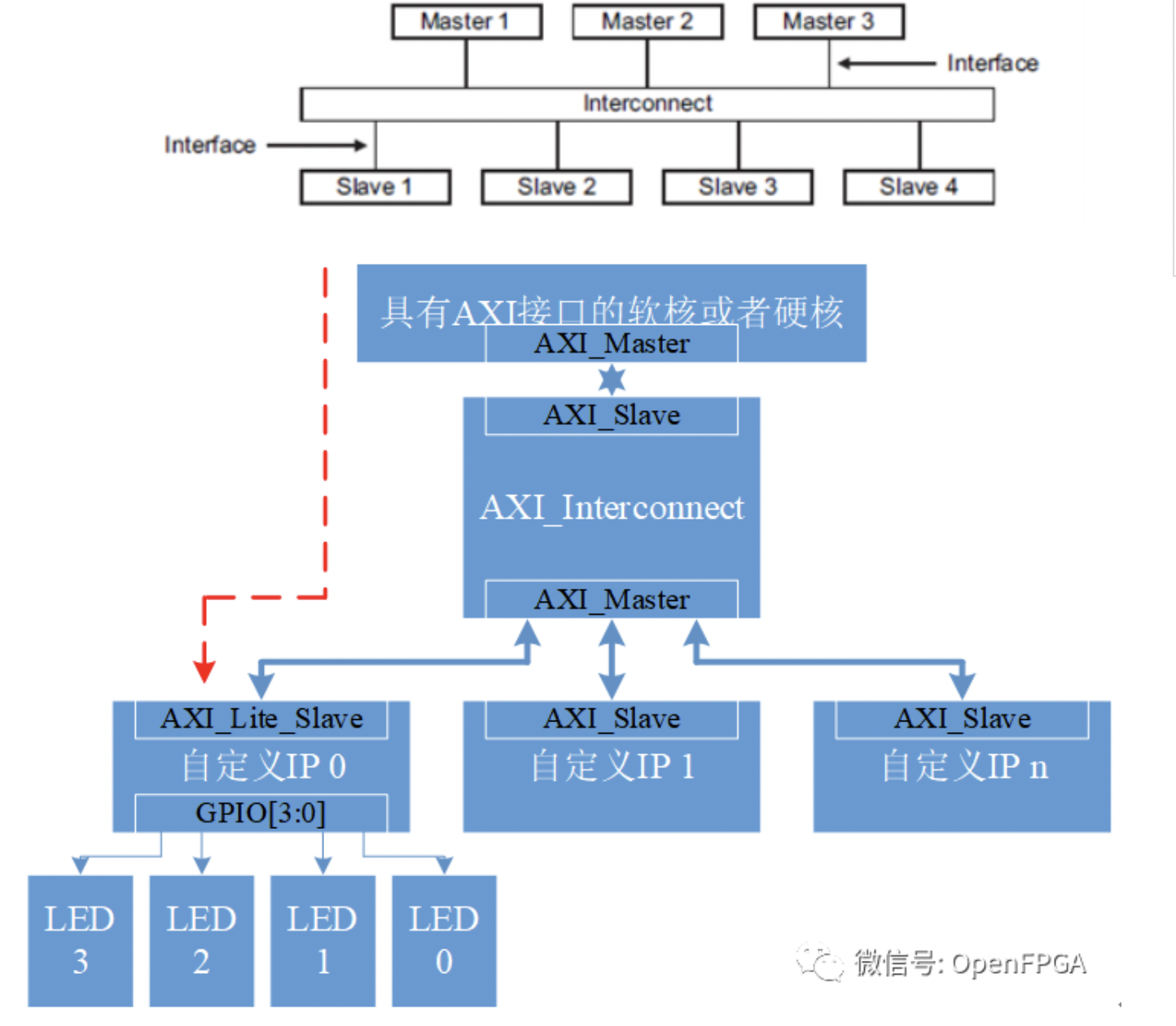

目的:通过嵌入式软核或者硬核通过AXI_Lite接口(Master)控制FPGA端引脚的GPIO。

实现框图:

图4‑50自定义IP应用框图

按照AXI互联机制我们知道,我们的自定义IP是通过AXI_Interconnect连接到Master端,整体的框图也比较简单,为了验证方便我们只按照红色线路径进行测试。

自定义的IP也比较简单,是直接在上面两节的基础上修改几个参数即可。

我们知道软核或者硬核通过接口向自定义IP写数据时,是通过slv\_reg寄存器向总线上写数据的,为了方便计算基地址,我们选用slv\_reg0寄存器赋值给GPIO。

通过图4‑49知道,IP的顶层接口分成两部分,一个是AXI_Lite接口,这部分上面两节有介绍,一个是GPIO接口,所以需要在顶层文件中增加这一接口。

代码4‑7自定义IP顶层接口定义

同时这一接口也需要传到实现接口协议的子module中,所以在例化子module时也需要增加这一语句,具体可以看源码。

子module中也比较简单只需要在最后面增加下面语句即可实现需要的功能:

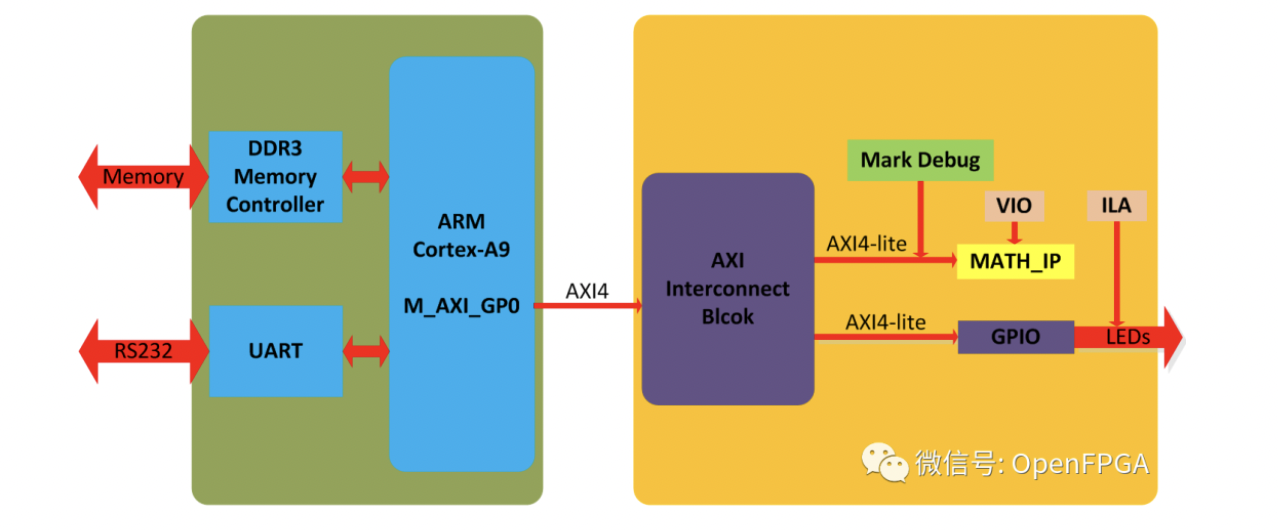

assignGPIO_LED\[3:0\]= slv_reg0\[3:0\];图4‑51系统实现框图

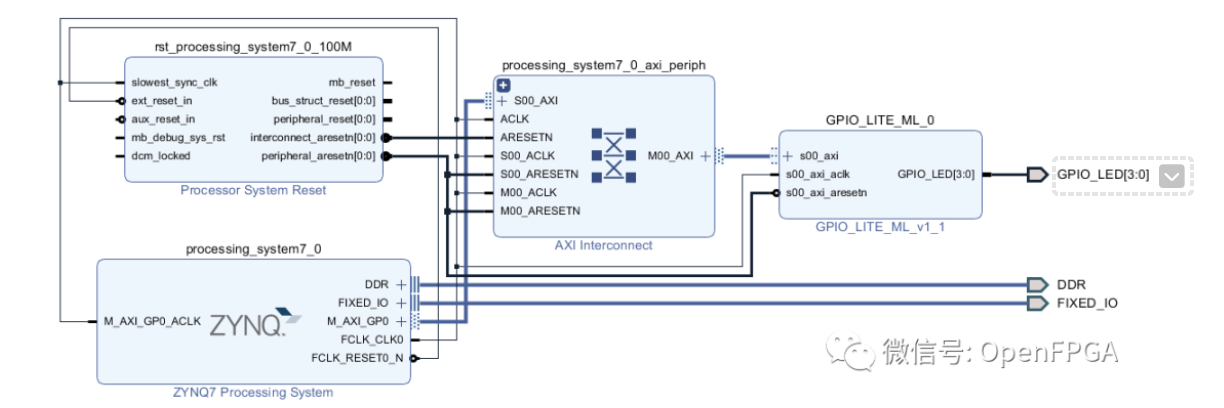

然后将自定义的IP打包封装好,就可以在Vivado中调用了,实现的BD如下:

图4‑52Vivado中实现的BD框图

最后编写约束文件,分配好引脚,综合编译、布局布线产生bit流文件,导出到SDK,编写SDK文件通过ARM硬核的AXI_GP_Master控制FPGA端的引脚即可,这部分不过多赘述,直接查看工程源码即可。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。