设计多级cache可以有很多种方式,可以根据一个cache的内容是否同时存在于其他级cache来分类,即Cache inclusion policy。

- 如果较低级别cache中的所有cacheline也存在于较高级别cache中,则称较高级别cache包含(inclusive )较低级别cache。

- 如果较高级别的cache仅包含较低级别的cache中不存在的cacheline,则称较高级别的cache不包含(exclusive )较低级别的cache。

- 如果较高级cache的内容既不严格包含也不排除较低级cache,则称为非包含非排他(non-inclusive non-exclusive ,NINE)cache。

Inclusive Policy cache

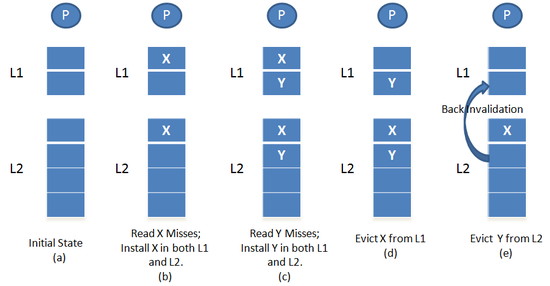

考虑一个两级cache 结构的示例,其中 L2 和 L1 是inclusive关系。假设有一个处理器对cacheline X 的读请求:

1、如果cacheline 在 L1 cache中找到,则从 L1 cache中读取数据并返回给处理器。

2、如果该cacheline 未在 L1 cache中找到,但存在于 L2 cache中,则从 L2 cache中提取该cacheline 并将其linefill到 L1 中。

3、如果该请求导致一个cacheline 从 L1 中被逐出,则 L2 不会发生任何动作。如果在 L1 或 L2 中均未找到该cacheline ,则从主存中取出该cacheline 并将其linefill到L1和 L2 中。

4、如果有来自 L2 的evict,L2 cache会向 L1 cache发送invalidation ,以便不违反“Inclusive Policy”。

如上图所示,最初 L1 和 L2 cache一开始都是空的(a)。

1、处理器发送一个读 X 请求。一开始L1 和 L2 都是miss的,因此cacheline 从主存被linefill到L1 和 L2,如(b)所示。

2、然后,处理器发出读取 Y 请求,该请求在 L1 和 L2 中均miss 。因此,cacheline Y 被linefill到 L1 和 L2 中,如(c)所示。

3、如果cacheline X 必须从 L1 中evict,那么它只会从 L1 中移除,如(d)所示。

4、如果块 Y 必须从 L2 中evict,它会向 L1 发送invalidation ,因此cacheline Y 从 L1 中移除,如(e)所示。

为了保持inclusion ,需要满足:

1、无论set的数量,L2 way的数量都必须大于或等于 L1 way的数量。

2、无论 L2 way的数量,L2 set的数量必须大于或等于 L1 set的数量。

Exclusive Policy cache

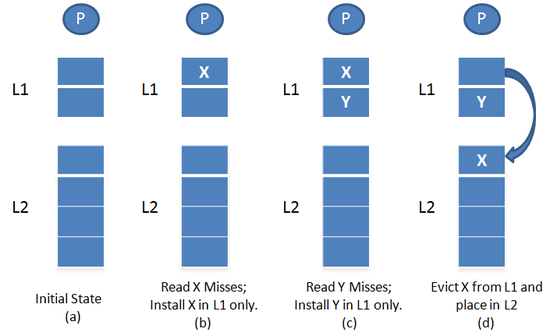

考虑一个 L2 cache 不包含 L1 cache的示例。假设有一个处理器对cacheline X 发起读请求。

1、如果cacheline 在 L1 cache中找到,则从 L1 cache中读取数据并返回给处理器。

2、如果该块未在 L1 cache中找到,但存在于 L2 cache中,则将该cacheline 从 L2 cache移动到 L1 cache。

2、如果一个cacheline 从 L1 中被evict,则被逐出的cacheline 将被放置到 L2 中。这是 L2 linefill的唯一方式。

3、如果在 L1 或 L2 中均未找到该cacheline ,则将其从主存中取出并linefill到 L1 中而不是 L2 中。

如上图所示,最初 L1 和 L2 cache都是空的 (a)。

1、处理器发送一个读 X 请求。它将在 L1 和 L2 中都miss,因此cacheline 从主存被linefill到 L1,如 (b) 所示。

2、处理器再次发出读取 Y 请求,该请求在 L1 和 L2 中均miss。因此,cacheline Y 被linefill到 L1 中,如(c)所示。

3、如果cacheline X 必须从 L1 中逐出,那么它会从 L1 中移除到 L2 中,如(d)所示。

NINE(non-inclusive non-exclusive) Policy

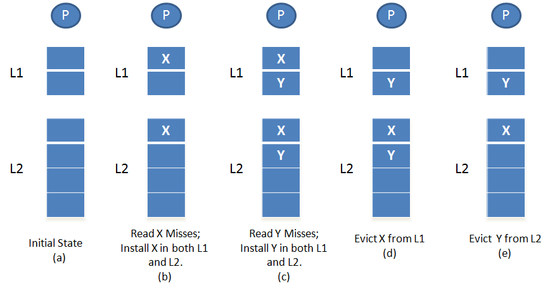

考虑一个 non-inclusive non-exclusive cache的示例。有一个处理器对cacheline X 的读请求:

1、如果cacheline 在 L1 cache中找到,则从 L1 cache中读取数据并返回给处理器。

2、如果该cacheline 未在 L1 cache中找到,但存在于 L2 cache中,则从 L2 cache中提取该cacheline并将其放置到L1 中。

3、如果一个cacheline 从L1逐出,则 L2 没有任何行为,这与Inclusive Policy相同。

4、如果在 L1 和 L2 中都没有找到该cacheline ,则从主存中取出该cacheline 并将其linefill到 L1 和 L2 中。

5、如果从 L2 逐出,与Inclusive Policy不同,没有invalidation 。

如上图所示,最初 L1 和 L2 cache都是空的 (a)。假设处理器发送一个读 X 请求。

1、 L1 和 L2 都是miss,因此cacheline 从主存被linefill到L1 和 L2,如(b)所示。

2、 处理器再次发出读取 Y 请求,该请求在 L1 和 L2 中均miss。因此,cacheline Y 被放置在 L1 和 L2 中,如(c)所示。

3、 如果cacheline X 必须从 L1 中逐出,那么它只会从 L1 中移除,如(d)所示。

4、如果cacheline Y 必须从 L2 中逐出,则它仅从 L2 中驱逐,如(e)所示。

3种策略的比较

inclusive policy的优点在于:在每个处理器都具有私有cache 的并行系统中,如果存在cache miss,则检查其他私有cache以查找该cacheline。如果L2 cache包含L1 cache并且在L1 cache中miss,则不需要再搜索L1 cache。这意味着与inclusive cache和 NINE cache相比,inclusive cache的miss 延迟更短。

inclusive policy的一个缺点是:cache的内存容量由L2 cache决定的。exclusive cache的容量是层次结构中所有cache的总容量。如果L2 cache较小,则在inclusive cache中浪费的cache容量更多。

尽管exclusive cache具有更多的内存容量,但相比NINE cache,它需要占用更多的带宽,因为L1 cache evict时需要linefill数据到L2 cache。

因此,需要基于成本和收益评估,然后进行选择_。_

上面仅仅是介绍了cache的包含问题,没有说明不同level cache中的数据一致性问题。可能存在L2 cache和L1 cache同时包含一个cacheline tag,但是其内容是不同的。这取决于write policy:

write back policy在写L1 cache时不会通知L2 cache;

write-through policy在写L1 cache时会通知L2 cache。

作者:xpuu

原文:处理器芯片设计

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。添加极术小姐姐(微信:aijishu20)微信可申请加入IC设计交流群。