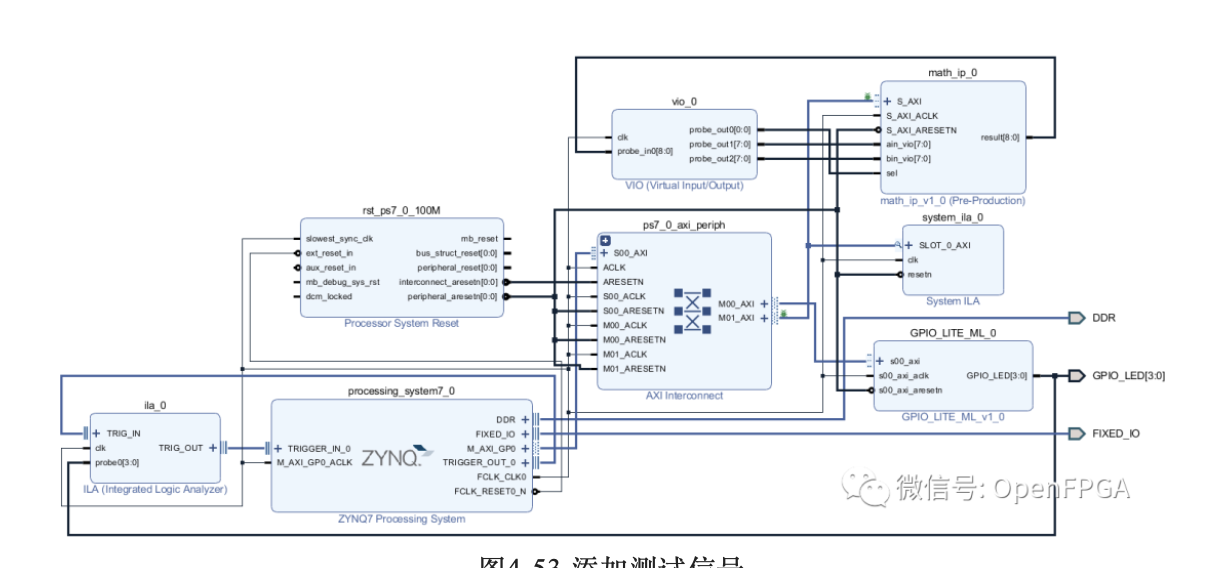

在《AXI-Lite 自定义IP》章节基础上,添加ila\vio等调试ip,完成后的BD如下图:

图4‑53添加测试信号

加载到SDK,并且在Vivado中连接到开发板。

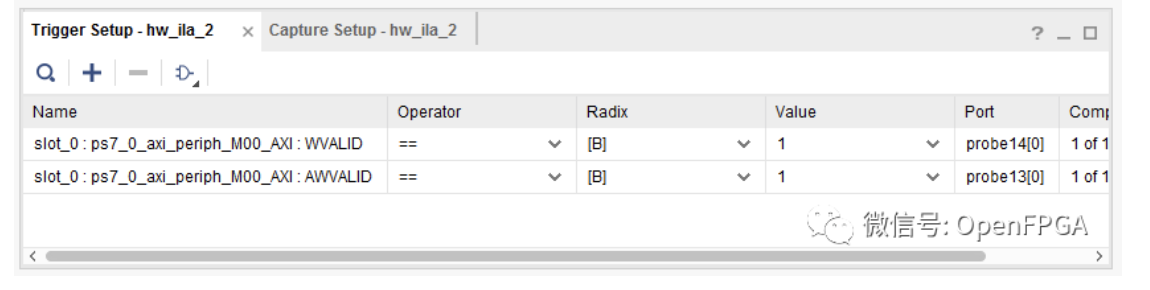

Trigger Setup,点击“+”,选择 AXI_WVALID,双击添加。设置 Radix 为 B,触发条件 Value 为 1。

图4‑54添加信号

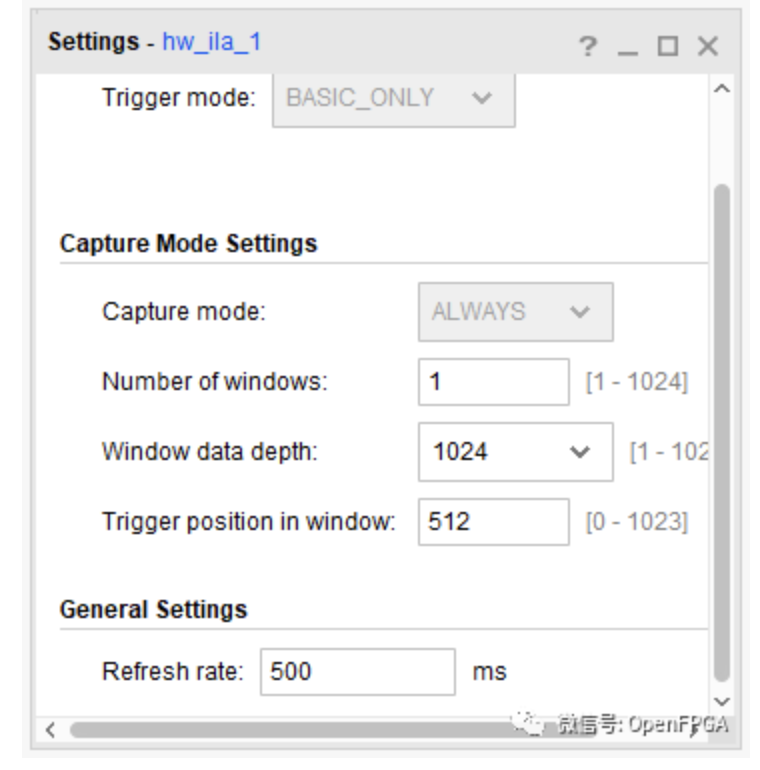

设置触发位置为 512

图4‑55设置触发位置

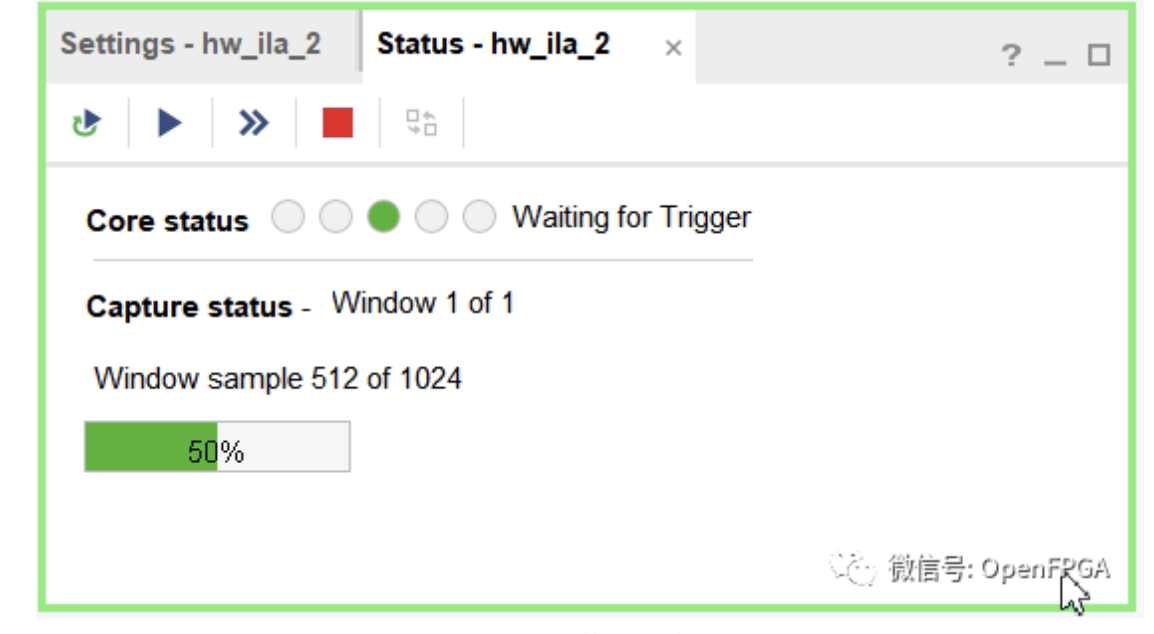

单击运行按钮,启动触发,进入等待触发状态。

图4‑56等待触发

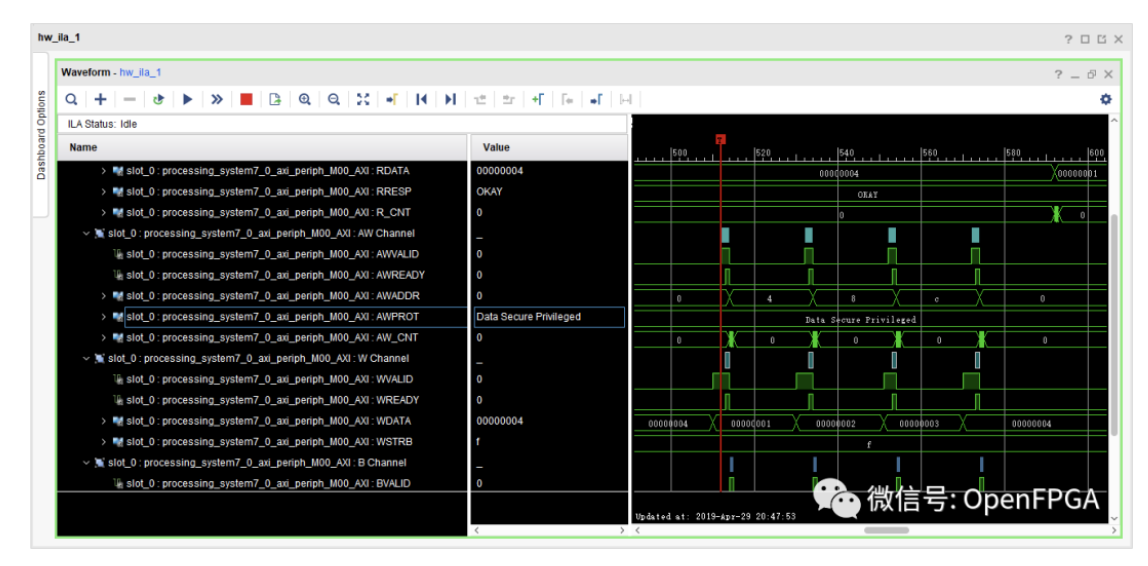

单击 SDK 中的运行按钮后, VIVADO 中 HW_ILA2 窗口采集到波形输出,可以看到 AXI 总线的工作时序。

SDK中 mian.c 程序功能是向 AXI4 总线写入 1~4,再从 AXI4 总线读数据,从上面对未修改直接封装的 IP 分析,可以读出的数据应等于写入的数据。

从波形图可以看出,写入的数据是 1、 2、 3、 4,对应基地址的偏移地址是 0、 4、 8、 12。

图4‑57仿真结果

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。