绪论

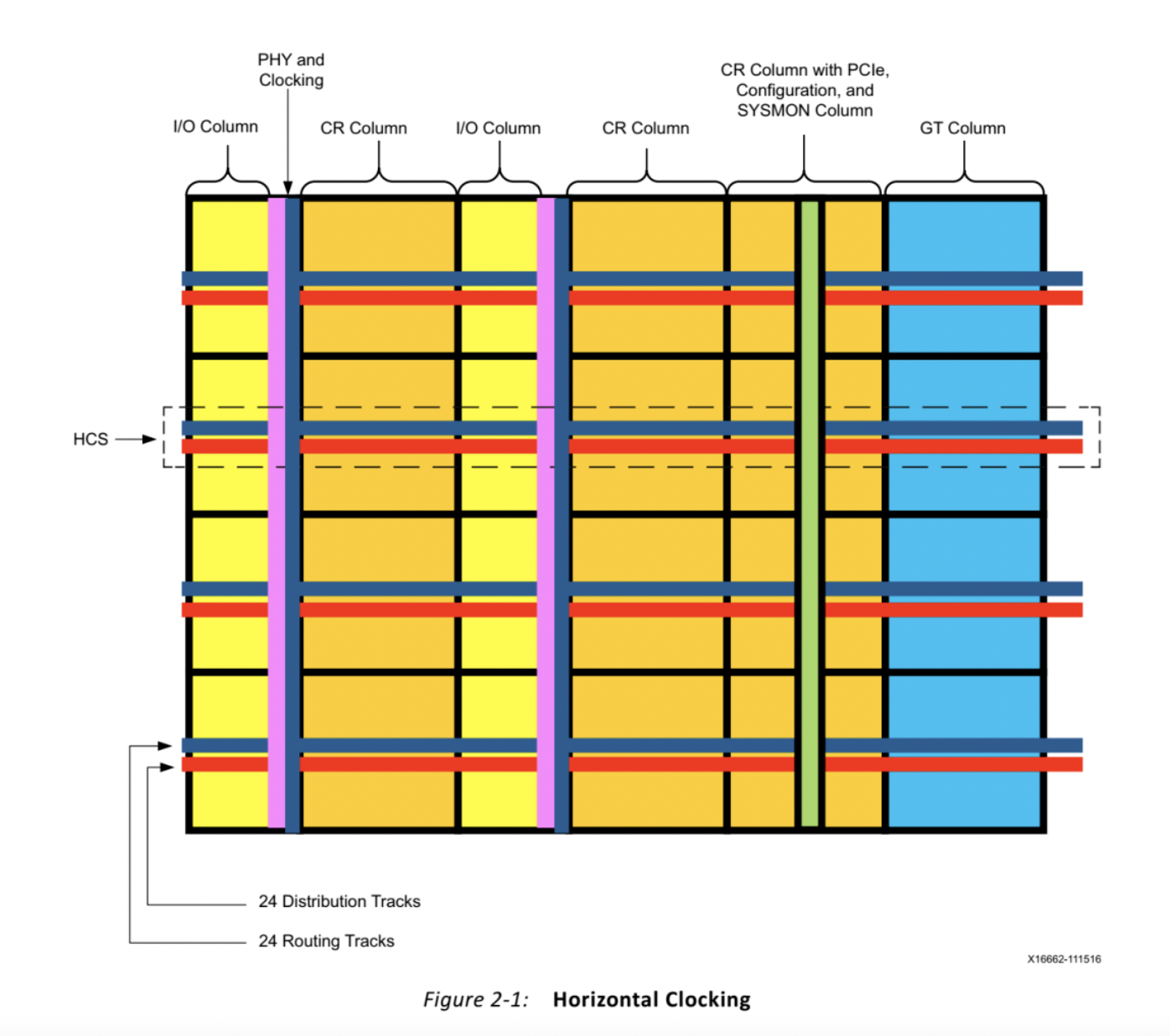

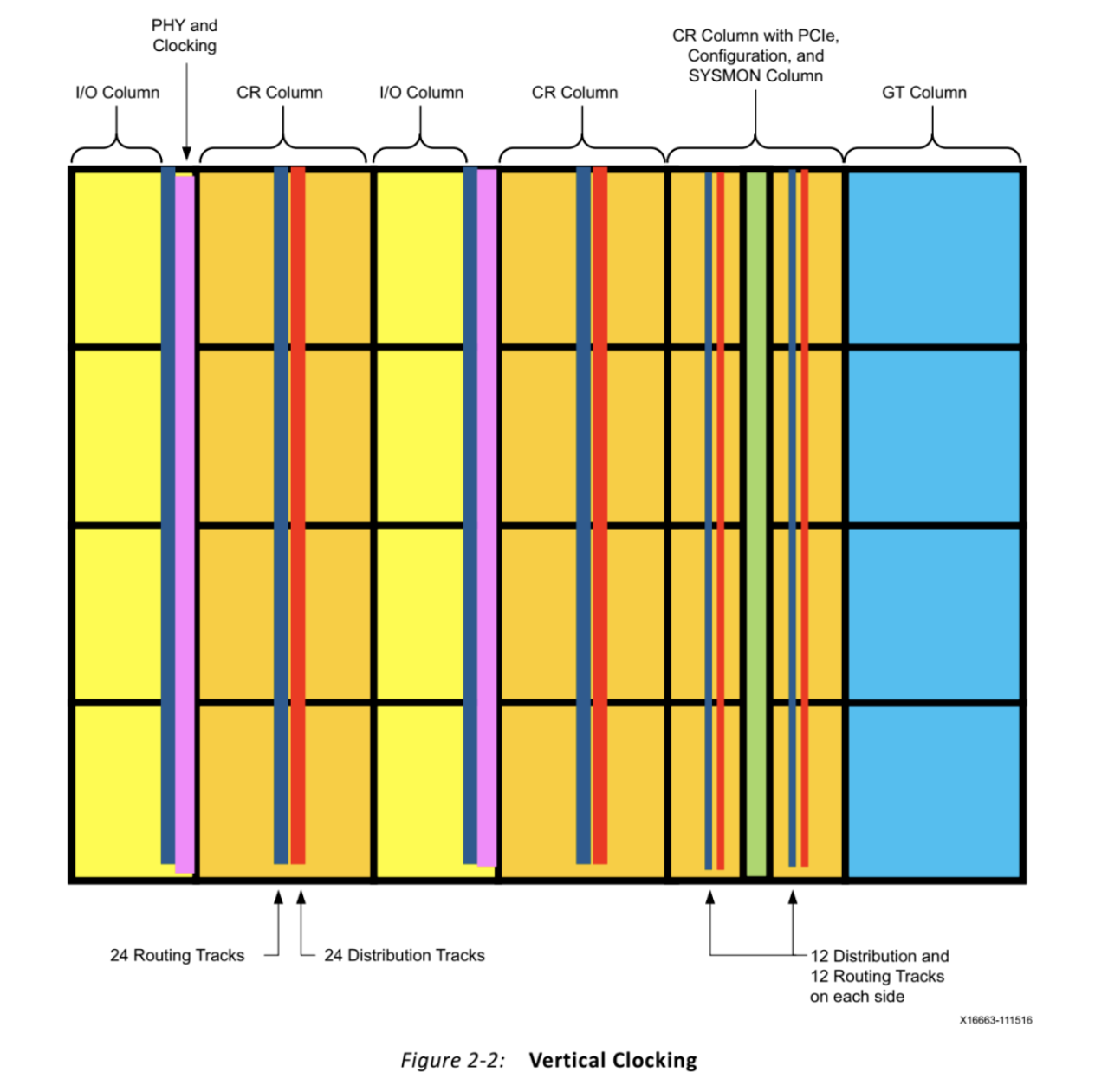

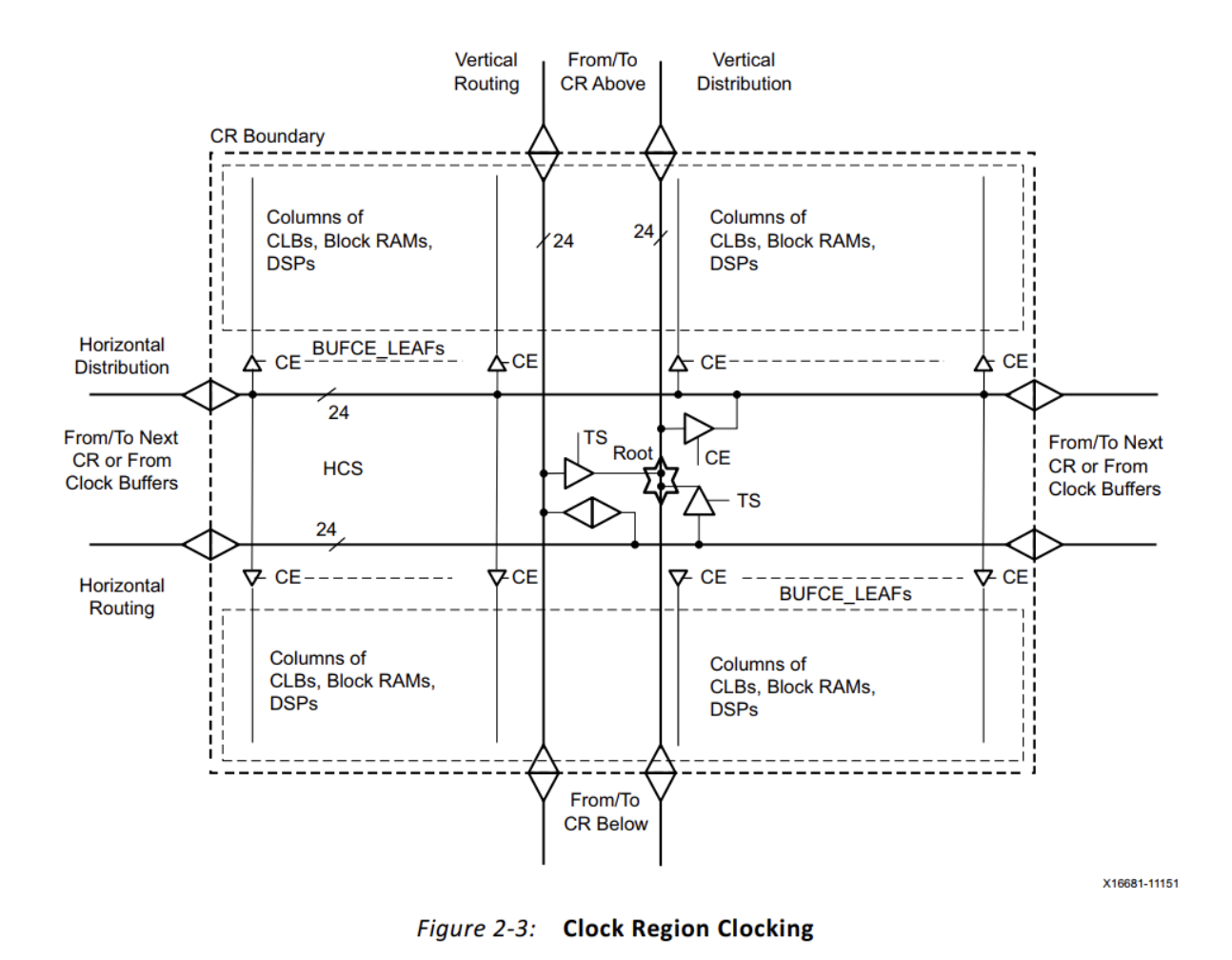

图2.1和2.2给出了UltraScale结构的时钟结构。从图中可以看出,基本的结构是由表示分段时钟行和列的CR块构成的CR以一个单元的方式排列,从而构造出行和列。每个CR包含切片、DSP、36KB的BRAM。在每个CR中,所包含这些资源的数目在行方向上可能不同,但是在垂直方向上是一样的。每个CR的高度是60个CLB、24个DSP和12个BRAM,从而为元器件构建了这些资源的列。

从图中可以看出:

(1)在CR的中间插入I/O列和GT列。

(2)与I/O列相邻的是PHY块,包含时钟管理单元(CMT)、全局时钟缓冲区、全局时钟复用结构和I/O逻辑管理功能。

(3)时钟结构存在一个单个的列,其包含配置逻辑、系统监控器和PCIe。

(4)一个水平时钟脊梁(HorizontalClockSpine,HCS)穿过每行CR、I/O和GT的中间。HCS含有水平布线和分布引线,以及叶子时钟缓冲区,还有在水平/垂直布线和分配之间的时钟网络互连。

(5)垂直的布线连接通道和分配连接一列内所有的CR,而垂直布线跨越一个完整的I/O列。时钟结构包含24个水平布线连接通道和24个分布引线连接通道,以及24个垂直布线连接通道和24个分配引线连接通道。

(6)I/O由来自PHY的时钟直接驱动,或者通过布线引线由相邻的PHY驱动。

CR结构如下:

时钟资源

UltraScale结构的时钟资源包括全局时钟输入、字节时钟输入、时钟缓冲和布线。

1.全局时钟输入

每一个I/O组(Bank)上有4个全局时钟(Global Clock,GC)引脚,可以直接访问全局时钟缓冲区、MMCM和PLL。GC输入提供了高速访问全局和区域时钟资源的专用通道。

每个I/O组位于一个单个时钟域内,包含52个I/O引脚。

2.字节时钟输入

字节时钟(DBC和QBC)输入引脚是专用的时钟输入,直接驱动源同步的时钟到I/O块的比特切片。在存储器应用中,这些称为DQS。

3.时钟缓冲和布线

PHY全局时钟包含BUFGCTRL、BUFGCE和BUFGCE\_DIV,如图1.26所示。它们中的每一个都可以被来自相邻Bank、MMCM、同一PHY的PLL和互连直接驱动。时钟缓冲区用于驱动整个芯片内的布线和分配资源。每个PHY包含24个BUFGCE、8个BUFGCTRL和4个BUFGCE\_DIV。但是,在同一时刻,只能使用其中的24个缓冲区。

时钟管理模块

UltraScale结构的每个I/O组包含一个时钟管理单元(ClockManagementTile,CMT),每个CMT包含下面的功能单元:

(1)一个混合模式的时钟管理器(Mixed-modeClockManager,MMCM)。

(2)两个相位锁相环(PhaseLockLoop,PLL),其目的主要用于为I/O生成时钟。但是,它也包含了用于内部结构的MMCM的一些功能集。

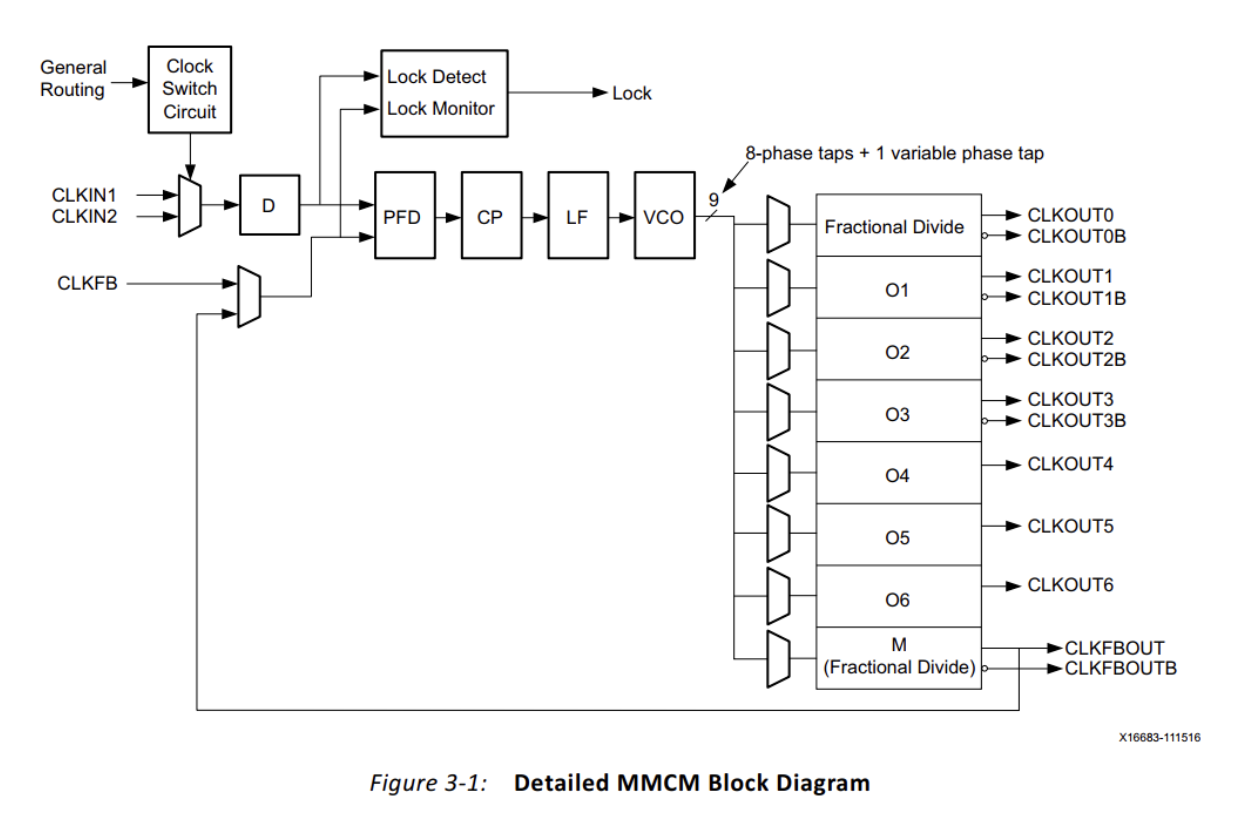

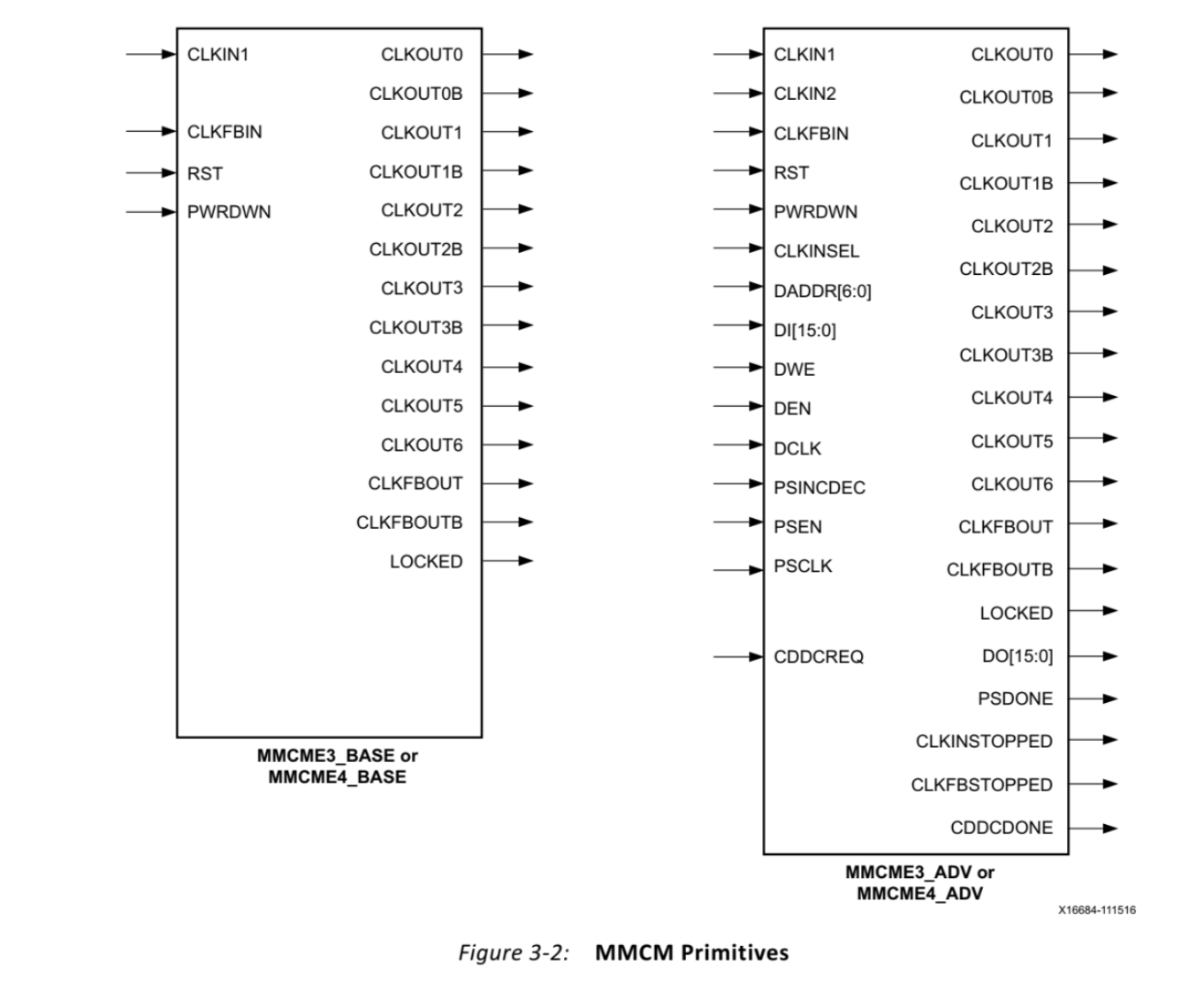

图1.28给出了MMCM的内部结构。MMCM用于宽范围频率的合成、内部或者外部时钟的抖动过滤器。MMCM的核心是一个压控振荡器(Voltage Controlled Oscillator,VCO),根据来自相位频率检测器(Phase Frequency Detector,PFD)的电压,VCO增加或者降低频率。

MMCM中有3个可编程的分频因子D、M和O。通过动态配置端口,可以在配置和正常的操作期间对其进行编程。预触发器D,用于降低输入时钟的频率,然后将其送入相位/频率比较器;反馈分频器M,由于在将它送给相位比较器之前,其将VCO的输出频率进行分频,所以其充当乘法器的角色。必须选择合适的D和M,以便VCO处于其指定的频率范围内。VCO有8个等间隔的输出相位(0°、45°、90°、135°、180°、225°、270°和315°),可以选择其中的一个相位来驱动一个输出分频器。可以在配置时,对每个分频器进行编程,分频因子为1~128中的任意整数。

MMCM有3个输入抖动过滤器选项:低带宽、高带宽和优化模式;其中:

(1)低带宽模式有最好的抖动衰减。

(2)高带宽模式有最好的相位偏置。

(3)优化模式允许Vivado工具找到最好的设置。

MMCM也有一个小数计数器,它位于反馈路径(充当乘法器)或者输出路径。小数计数器允许非整数的1/8增量。因此,增加频率合成能力8倍。根据VCO的频率,MMCM也能够提供小幅度增量的固定相移或者动态相移。在1600MHz时,相位移动时间增量是11.2ps。

PLL比MMCM的特性要少得多。在一个时钟管理单元内的两个PLL,其基本上是为专用的存储器接口电路提供必要的时钟的。在PLL中心的电路类似于MMCM,带有PFD和VCO,以及可编程的M、D和0计数器。每个PLL有两个到FPGA结构的分频输出,以及到存储器接口电路的一个时钟和一个使能信号。

在实际使用时,读者可以通过Vivado开发套件中IP Catalog中提供的Clocking Wizard来选择并配置MMCM/PLL。

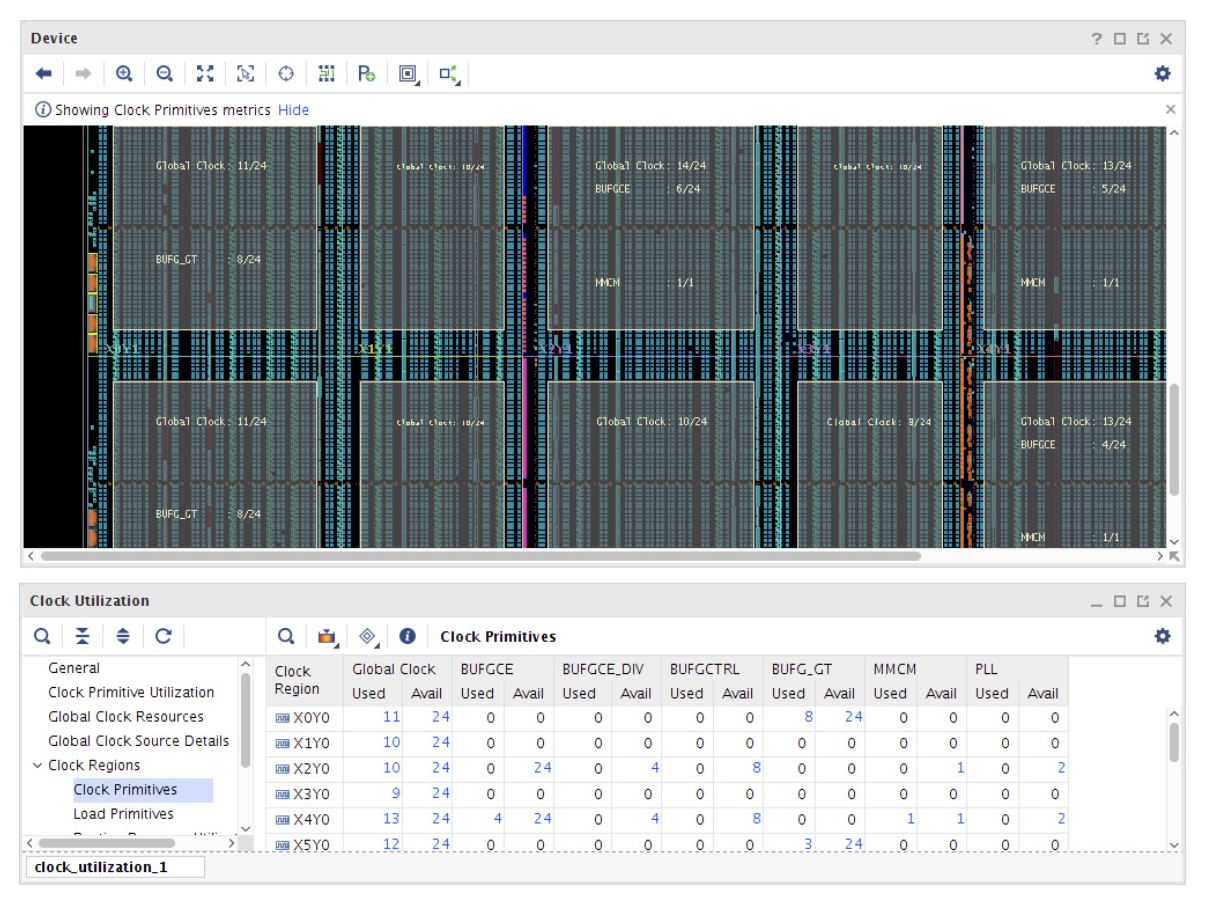

可以使用 Vivado IDE 中的“Clock Utilization Report”来进行可视化分析时钟资源利用率和时钟布局。下图显示了在“Device”窗口中叠加的每个时钟区域的时钟资源利用率。如需了解更多有关此报告的信息,请参阅 《Vivado Design Suite 用户指南:设计分析和收敛技术》 (UG906) 。

更多关于Ultrascale的时钟资料请查看Xilinx官方文档UG572。

Ultrascale和ZYNQ-7000系列时钟资源的区别

以下内容参考来源:https://cloud.tencent.com/developer/article/1554748

UG949 第三章-设计创建-时钟指南

时钟管脚

7系列FPGA的时钟管脚分为SRCC(Single-region clock-capable I/O)和MRCC(Multi-region clock-capableI/O),两者的主要差异在于驱动局部时钟资源的类型不同,也就是SRCC可驱动BUFR,不能驱动BUFMR,而MRCC则即可驱动BUFR也可驱动BUFMR。在UltraScale系列FPGA中,GC(Global Clock)管脚取代了SRCC和MRCC,换言之,GC不再有SRCC和MRCC。

时钟区域

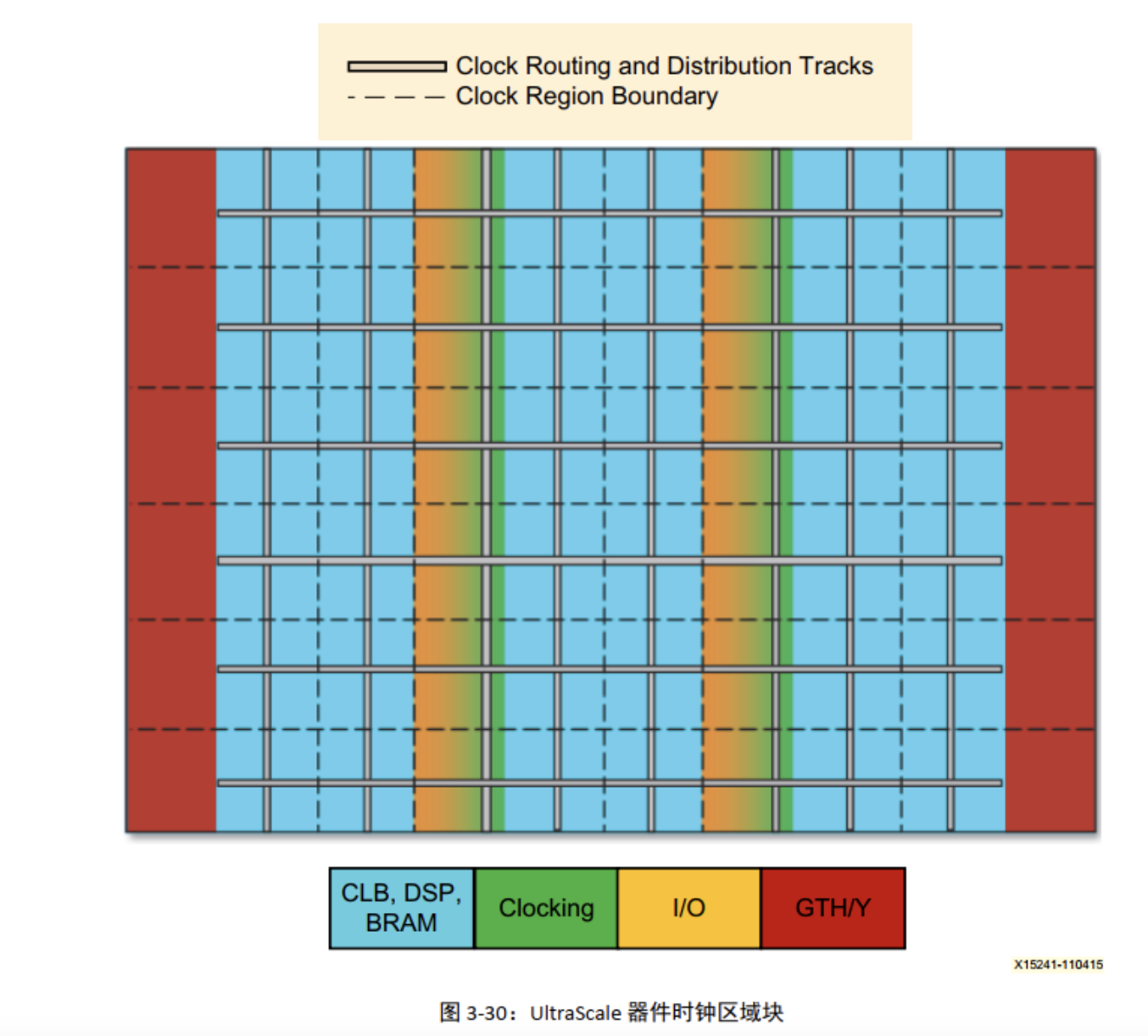

这里所说的时钟区域(Clock Region)是FPGA内部结构,包括相应的CLB、DSP、BRAM、互联资源等。7系列FPGA中,时钟区域的宽度(水平方向)为芯片宽度的一半,而UltraScale不再有这种限制。如下图所示的UltraScale时钟区域(图片来源,ug949,figure3-37),共有6x6即36个,如果是7系列FPGA,则是2x6即12个。

时钟缓冲器

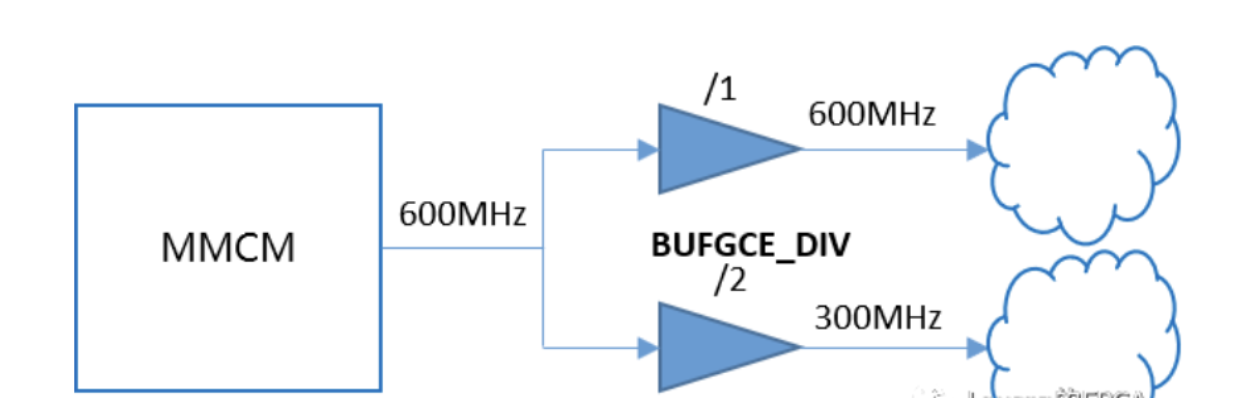

7系列FPGA中有所谓的局部时钟缓冲器,例如BUFR、BUFMR、BUFIO等,而UltraScale系列FPGA中不再包含这类时钟缓冲器,其功能由新增的BUFGCE\_DIV代替。同时,需要明确BUFGCE\_DIV并非局部时钟资源,而是全局时钟资源。BUFGCE\_DIV具有分频功能,对于简单的分频,相比于MMCM/PLL,BUFGCE\_DIV在功耗上更具优势,而且如果分频时钟和源时钟有跨时钟域路径,那么相应的Clock Skew会更小。看一个案例,设计中需要两个时钟,一个600MHz,一个300MHz,可采用如下图所示方案。MMCM生成时钟为600MHz,实例化两个BUFGCE\_DIV,其分频因子分别为1和2,从而可分别生成一个600MHz时钟和一个300MHz时钟,而且,这两个生成时钟也是同相的。

此外,在使用高速收发器生成的时钟时,可以使用BUFG\_GT。该时钟缓冲器也具有分频功能,也可以驱动FPGA内部其他逻辑资源。

总结一下:

• BUFMRs, BUFRs, and BUFIOs, and the associated routing resources have been removed from this architecture and are replaced by new clock buffers, clock routing, and a completely new I/O clocking architecture.

• The BUFGCTRL and its derivatives are still available. Two new global clock buffer resources BUFGCE and BUFGCE\_DIV have been introduced in the new architecture. At the local clocking level, a new BUFCE\_LEAF clock buffer provides local, vertical clocking with additional features.

• A BUFG\_GT buffer for clock division of GT clocks has been added.

• A new and improved clock routing architecture is available. There are now two types of global routing tracks called routing and distribution. Both types of routing provide a segmentable clock network at the CR level. Both types can be driven by the global clock buffers. The distribution tracks can be driven by routing tracks or directly by clock buffer resources. The distribution tracks provide connectivity to all clocking points in UltraScale devices.

• The CMTs now have two PLLs instead of one.

• MMCMs are similar to the MMCM in the 7 series devices. PLLs have new features related to I/O PHY clocking. However, other clocking related functionality and connectivity has been reduced as compared to the 7 series FPGAs. For example, the PLLs do not support phase compensation or external feedback, have fewer outputs, share a voltage-controlled oscillator (VCO) with the PHY clocking, and have other features removed as compared to the 7 series devices. For this reason, most customers should use the MMCM for general clocking. However, leftover PLLs are also available for use.

• The MMCM output clock frequencies can be dynamically changed without resetting the MMCM.

• The definition of clock region has changed. A clock region no longer spans half a device width in the horizontal direction. UltraScale architecture clock regions have a rectangular shape with a fixed width and height and are organized in tiles. Horizontal and vertical clock tracks are segmented at the clock region boundaries.

• The clock capable pins (CC) have been replaced by global clock pins (GC). In addition, the UltraScale+ architecture has high-density (HD) I/O banks. These banks contain four global clock pins called HDGC which can connect to the BUFGCEs.

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。