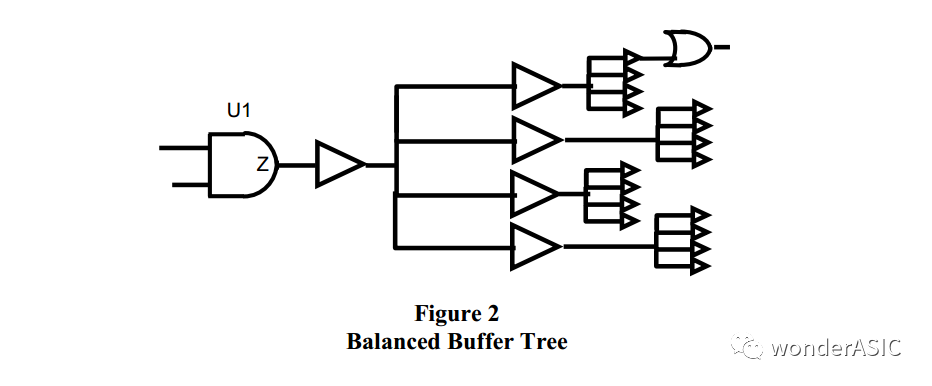

通常,高扇出网络将被缓冲以减少驱动门上的总负载,和网络的过渡时间。 对于具有相同时序要求的信号,例如时钟网络和复位线,可以使用平衡缓冲树,以减少信号边沿的skew。

通常,需要使用后端工具插入平衡缓冲树。对于时钟和复位网络,建议让Design Compiler暂且不管这些高扇出网络,使用专门的时钟树插入工具做这项工作。

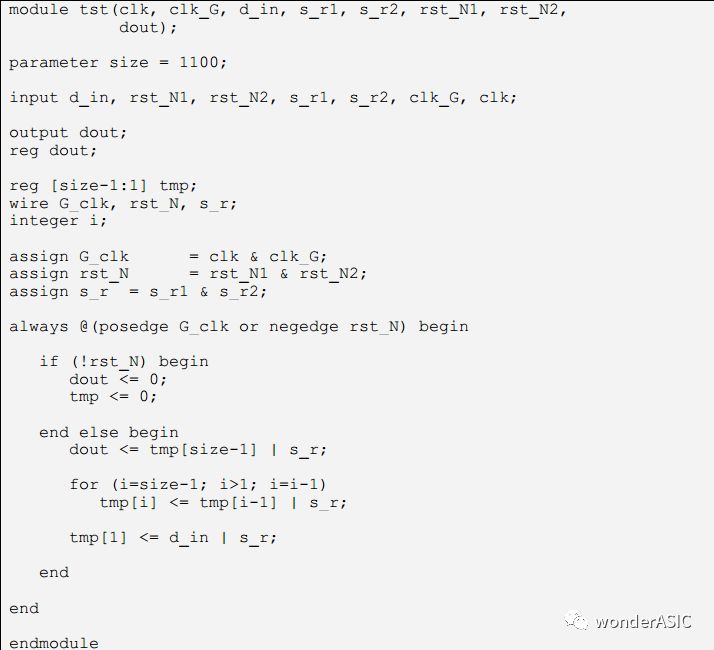

本文将讨论3类高扇出网络:

a)时钟网络;

b)复位网络;

c)一般的高扇出网络

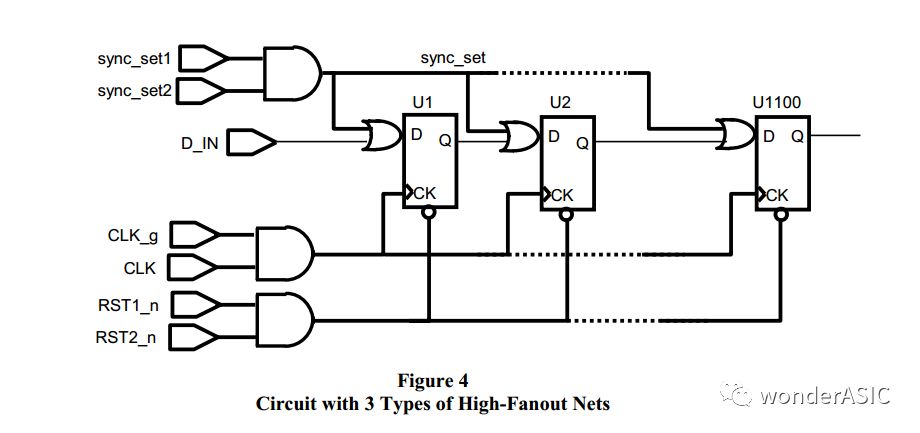

以下分别是示例电路的原理图和verilog描述:

让我们探讨一些帮助我们进行设计的常见规则,以综合包含这些高扇出网络的电路。

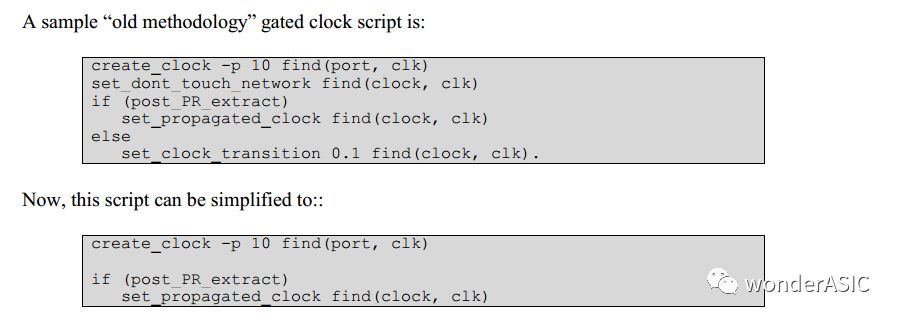

时钟网络是最简单的高扇出网络,Design Compiler 会“足够聪明”地知道这一点,应该将时钟网络留给更专业的工具去处理。

我们来看看,关于Design Compiler 处理时钟网络的一些常见误区:必须将 “set_dont_touch_network”应用于时钟,以确保Design Compiler不会“缓冲”时钟网络,否则Design Compiler将计算一个时钟网络的巨大过渡时间

而现实是,只要你使用了“create_clock”命令, Design Compiler将不会缓冲时钟网络,即使它是被门控的。 此外,Design Compiler将保持时钟网络理想的特性(零转换时间)。

所以,当综合具有高扇出的时钟网络时,只要在时钟上发出create\_clock命令,Design Compiler将不会缓冲时钟网络。在综合之前不需要施加其他的命令来处理高扇出的时钟网络。无论是否存在时钟门控。

理由:Design Compiler在时钟端口上施加了ideal_net属性。 这有效地防止Design Compiler计算时钟网络的DRC(logical DRC),从而防止缓冲时钟网络以修复max_capacitance和max_transition的违例。

ideal_net属性强制Design Compiler使用“理想”的时钟波形,即使是通过了负载很大的时钟门控。

通常,复位网络需要确保满足所有触发器复位引脚的恢复/移除时间。Reset网络同样也是个高扇出网络,需要通过后端工具进行平衡。因此,我们必须告诉Design Compiler,reset网络缓冲将在稍后的流程插入,以及忽略复位网络上的时序和DRC违规。

扇出几百或更少的网络可以通常由Design Compiler处理。由于foundry库中缓冲单元的不同驱动能力,DRC以及时序约束的不同,结果会有很大差异。

使用Design Compiler,您可以在综合之前识别高扇出网络。

report_net_fanout

确定了非常高扇出的网络之后,可以决定是否让Design Compiler缓冲高扇出网络。

Design Compiler默认会使用较小的扇出计算超过扇出阈值的高扇出网络的延迟和DRC。 可以通过Design Compiler的变量high_fanout_net_threshold设置此阈值。 例如,

high_fanout_net_threshold=200

在综合之前,Design Compiler使用扇出值200计算高扇出网络的延迟和DRC。 这将减少高扇出网络的时序和DRC违例,可以大大加快综合时间。 此变量默认为1000.

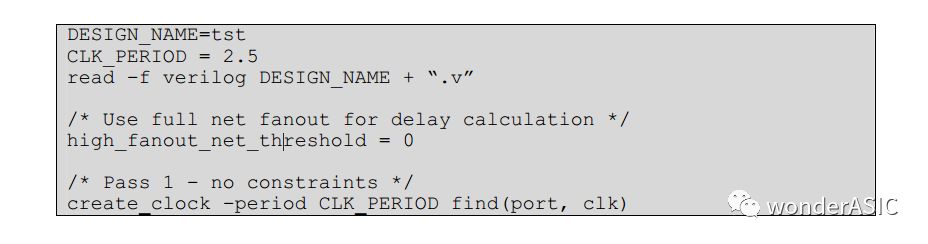

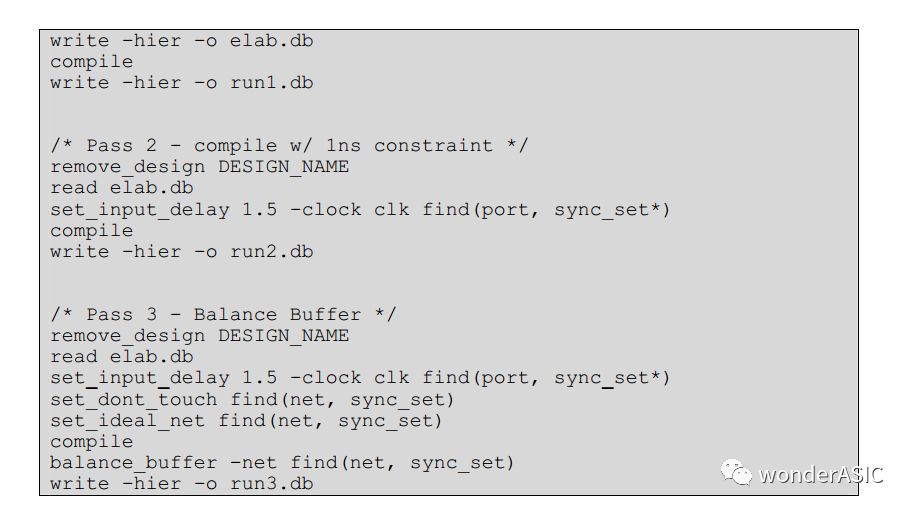

使用3种不同的方法再次综合图4的电路:

a)没有约束;

b)对sync_set输入使用1ns约束;

c)使用balance_buffer命令

用于综合设计的完整脚本如下所示:

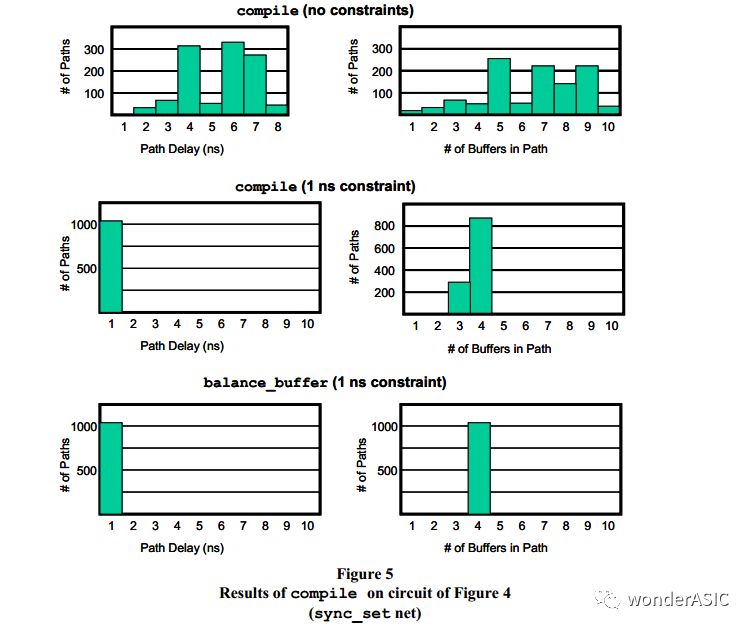

结果的比较如下图所示:

上图显示compile几乎与balance_buffer工作一样好!

作者:iwonder

链接:https://mp.weixin.qq.com/s/jN_RdreuWHUTsDb-pfJS5w

推荐阅读

- 总结我的验证思路:“开门红” Test Case

- 总结我的思路:发现Bug,发现所有的Bug,或者证明没有Bug,是验证存在的唯一目的

- 总结我的验证思路系列二:心有多大,舞台就有多大

- 总结我的验证思路:只有疯子,才能发现隐藏得最深的金子

更多数字IC设计技术干货等请关注数字芯片实验室专栏。添加极术小姐姐(微信:aijishu20)微信可申请加入IC设计交流群。