7.RAS概述

PCIe错误分为可校正的错误(Correctable Error)和不可校正的错误(Uncorrectable Error), Uncorrectable又分为致命的(Fatal)和非致命的(Nonfatal)。可校正错误可以自动地被硬件识别并被自动的校正或恢复。非致命错误可能会导致特定的传输变得不可靠,但是链路和硬件的其他功能不受影响。设备驱动软件提供恢复机制,并不会影响到链路和其他设备的运行。致命错误会导致链路和硬件异常,只有通过系统软件进行复位操作实现恢复。

7.1 硬件故障分类

三类硬件故障(Fault):

- 同步且精确的CPU异常(exception),这些异常可能是由于数据中止、指令预取中止,或由于访问某个故障地址时出现硬件故障而导致的某种形式的总线错误。

- 异步和不精确的CPU异常,可能由CPU内部的不可纠正错误(Uncorrected Error,UE)、可纠正错误(Corrected Error,CE)或外部总线错误触发。

- 异步和不精确的系统异常或中断,这些异常发生在CPU子系统之外,一般通过中断线或者消息中断(MSI)报告给CPU,通知CPU发生硬件故障。

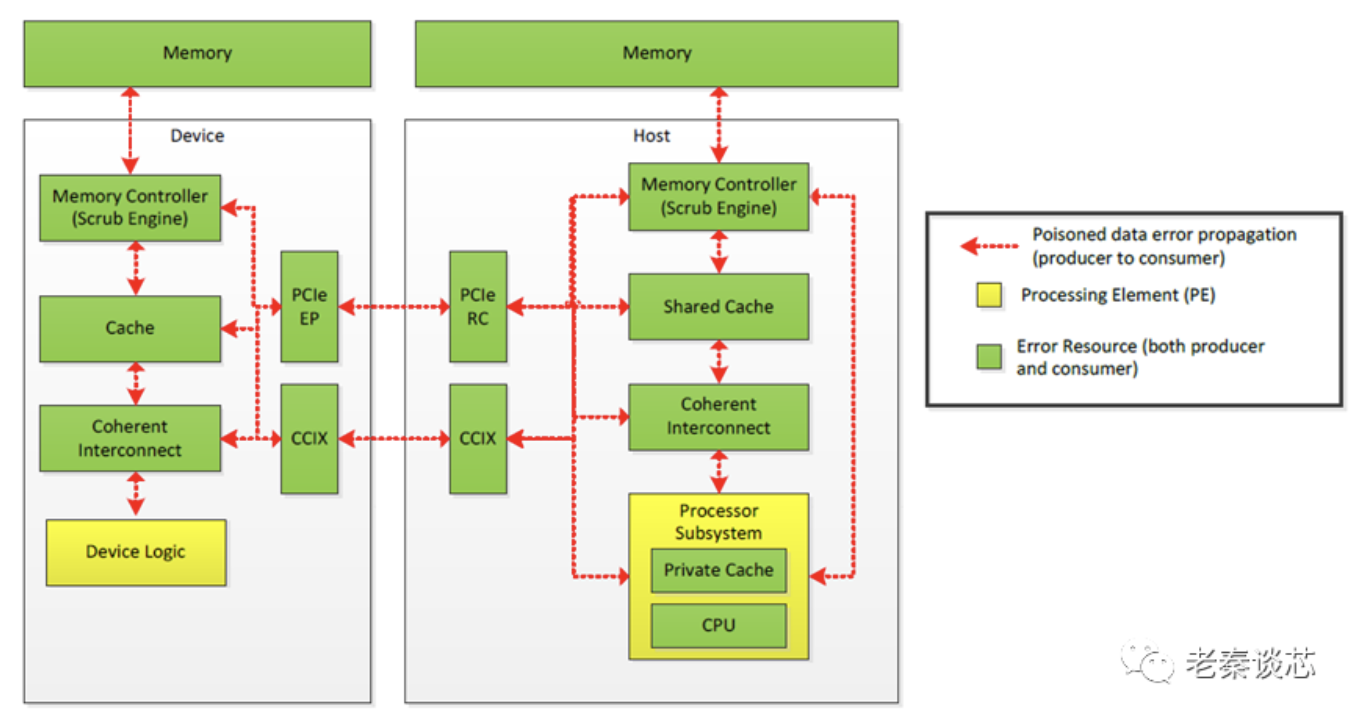

7.2 硬件错误传播

主机系统和CCIX设备可以有类似的组件集:

- 不同类型的存储

- 不同类型的缓存和寄存器堆

- 处理单元(Processing Elements)

- 一致性互连

上述每个组件都可能消耗、产生或是检测硬件错误。这些硬件错误可能与ECC、命令故障、传输错误、解码错误、逻辑错误、超时/看门狗等有关。

当数据中毒(poisoned)时,错误可能会在整个系统中从一个实体传播到另一个实体,这可能是由处理单元,或者缓存/监听逻辑启动的事务触发的。下图展示了有毒数据如何流经连接到CCIX设备的主机系统。

CCIX规范只规定了如何报告和处理CCIX错误。

7.3 CCIX协议错误报告(Protocol Error Reporting,PER)

有两类硬件故障(Fault)可以引起CCIX硬件错误(Error):

- PCIe传输错误,通过标准的PCIe机制报告

- CCIX协议错误(CCIX Protocol Errors ,PER),在设备端通过CCIX PER消息报告,并记录到CCIX DVSEC空间;在主机端,错误被报告给错误代理,错误代理向CPU报告错误

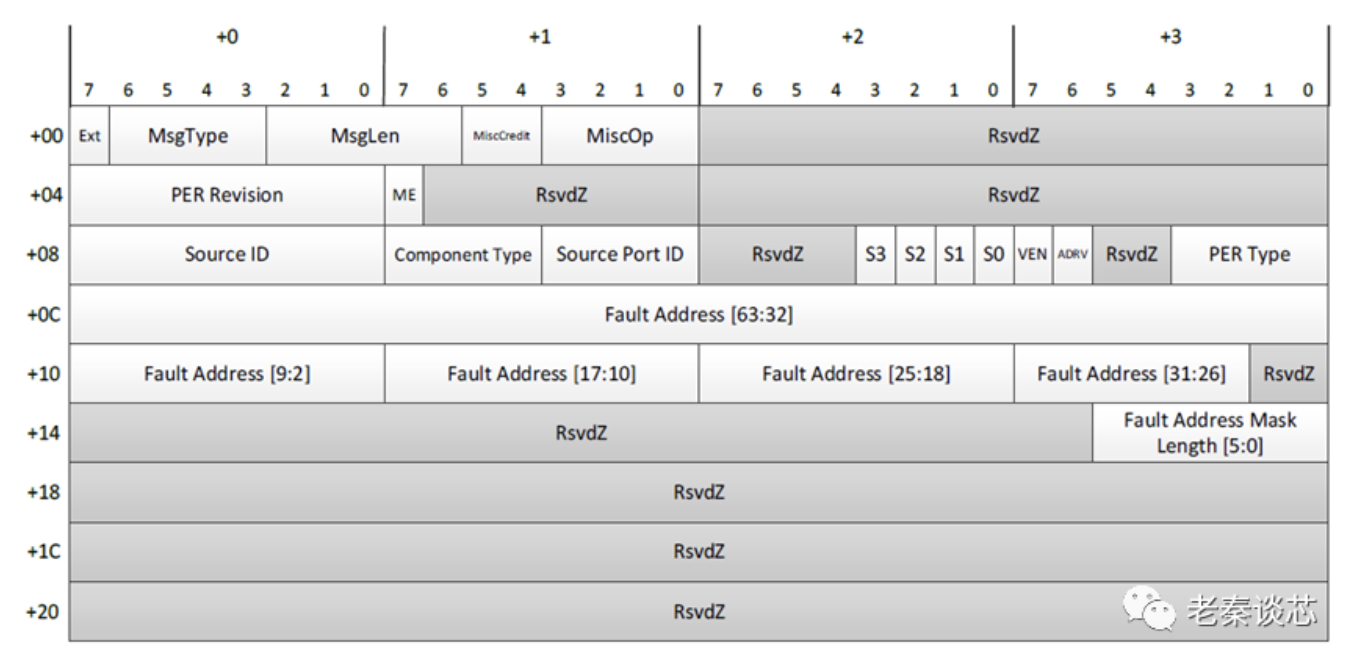

7.3.1 PER消息格式

PER消息格式:

其中的PER Type字段的含义是:

- 0x0:Memory Error Type Structure

- 0x1:Cache Error Type Structure

- 0x2:ATC Error Type Structure

- 0x3:Port Error Type Structure

- 0x4:CCIX Link Error Type Structure

- 0x5:Agent Internal

在规范的7.3.3 – 7.3.8章节有具体介绍。

7.3.2 PER日志结构

CCIX PER日志用于报告会导致协议错误的硬件故障。协议错误通常与特定的CCIX协议组件(即CCIX链路、端口、HA、SA或RA)相关。每个日志结构开始的偏移量(字节数)由各种能力结构的错误日志偏移量表示。

每个日志头由256位组成。DW0和DW1表示错误日志属性字段。DW2和DW3提供错误的故障地址。DW4提供错误的错误地址掩码长度。DW5-7保留供将来使用。后面的具体结构说明全都略去。

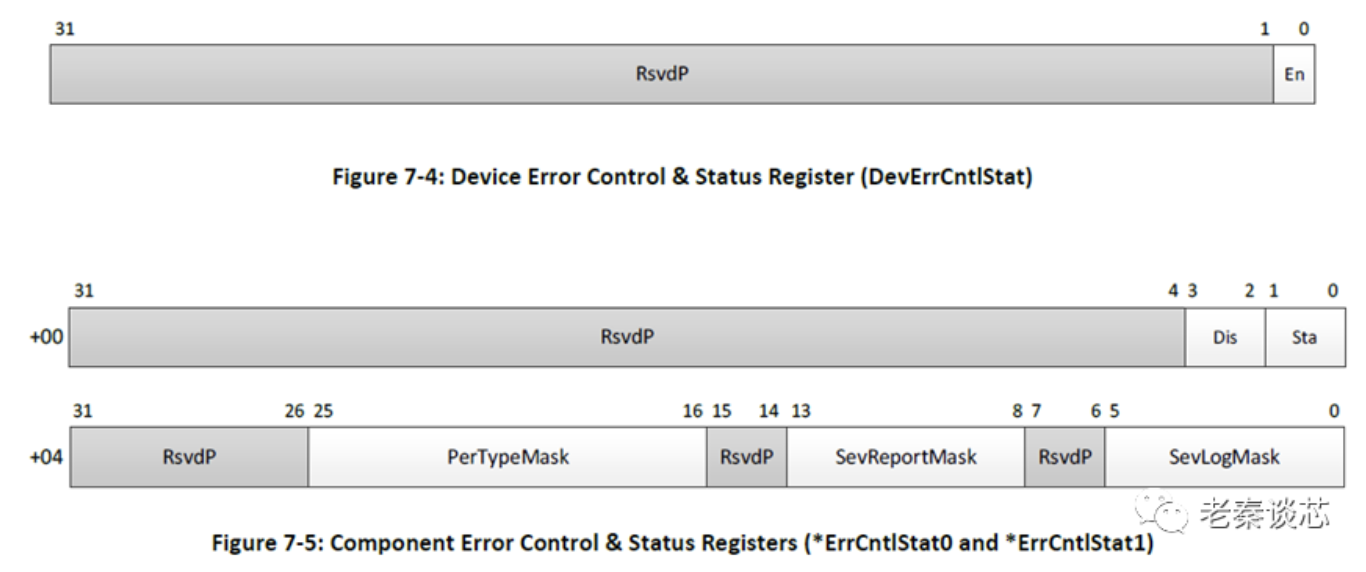

7.4 CCIX错误控制和状态结构

CCIX在两个级别提供错误控制机制:

- Level 1:CCIX设备错误控制和状态(每个CCIX设备)

- Level 2:组件错误控制和状态(根据CCIX协议组件)

必须禁用CCIX设备中所有错误控制和状态寄存器的重置值。主机软件必须明确启用CCIX设备和每个CCIX协议组件的错误报告。启用后,默认情况下,除非软件设置了掩码位,否则错误将被不能被屏蔽。

7.4.1 错误控制寄存器定义

设备和组件的控制寄存器如下:

7.4.2 设备错误控制流程

本章节介绍错误屏蔽规则和启动时启用错误的流程,略过。

8.地址翻译服务(Address Translation Services)

ATS机制是在PCIe中定义的。简单介绍一下,为节省CPU资源,PCIe设备常采用DMA方式访问内存。Root Complex需要将DMA请求进行一次地址转换才能将访问到真实物理存储地址。进行地址转换可以防止非法DMA请求,并且有利于实现虚拟化传输。但是,RC进行DMA地址转换是需要时间的,相较于不进行地址转换,显然进行DMA地址转换会增加DMA访问的时间。为了减小地址转换的影响,设计人员常常在需要进行地址转换的地方添加地址转换缓存(Address Translation Cache,ATC)。需要设备设计出具有良好的ATC机制,包括ATC的预测、地址翻译请求的长度、发送翻译请求的时机等。

8.1 介绍

CCIX请求代理(RA)发出的内存请求时使用的是物理地址。因此与RA关联的加速器功能(Accelerator Functions,AFs)必须向RA提供物理地址。但是软件使用的是虚拟地址,所以AFs需要执行地址转换。

请求代理不可以向CCIX链路发出带有未翻译虚拟地址的内存请求,因为这可能会违反基于页表的安全性或虚拟化。

AF可以使用两种方法来转换虚拟地址。第一种是使用PCIe定义的地址转换服务变体从主机系统获取地址转换。第二种方法是让AF包含一个MMU,以支持主机系统页表格式。

8.2 ATS

PCIe格式的ATS转换请求、转换完成、失效请求、页面请求和页面响应通过VC0发送。除CCIX VC外,可以在任何VC上发送失效响应。

8.3 无效语义

略过。

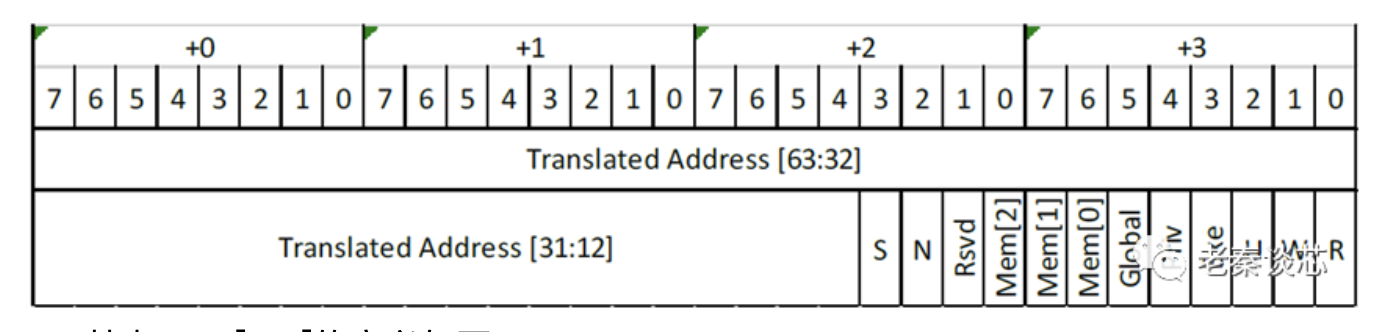

8.4 内存类型

除了获取翻译后的页面地址外,CCIX请求代理还需要内存类型信息,以便与内存正确交互。内存类型信息决定了CCIX链路上支持的操作类型,以及数据是否可以在本地缓存。

带有内存属性的ATS翻译完成的格式和定义如下:

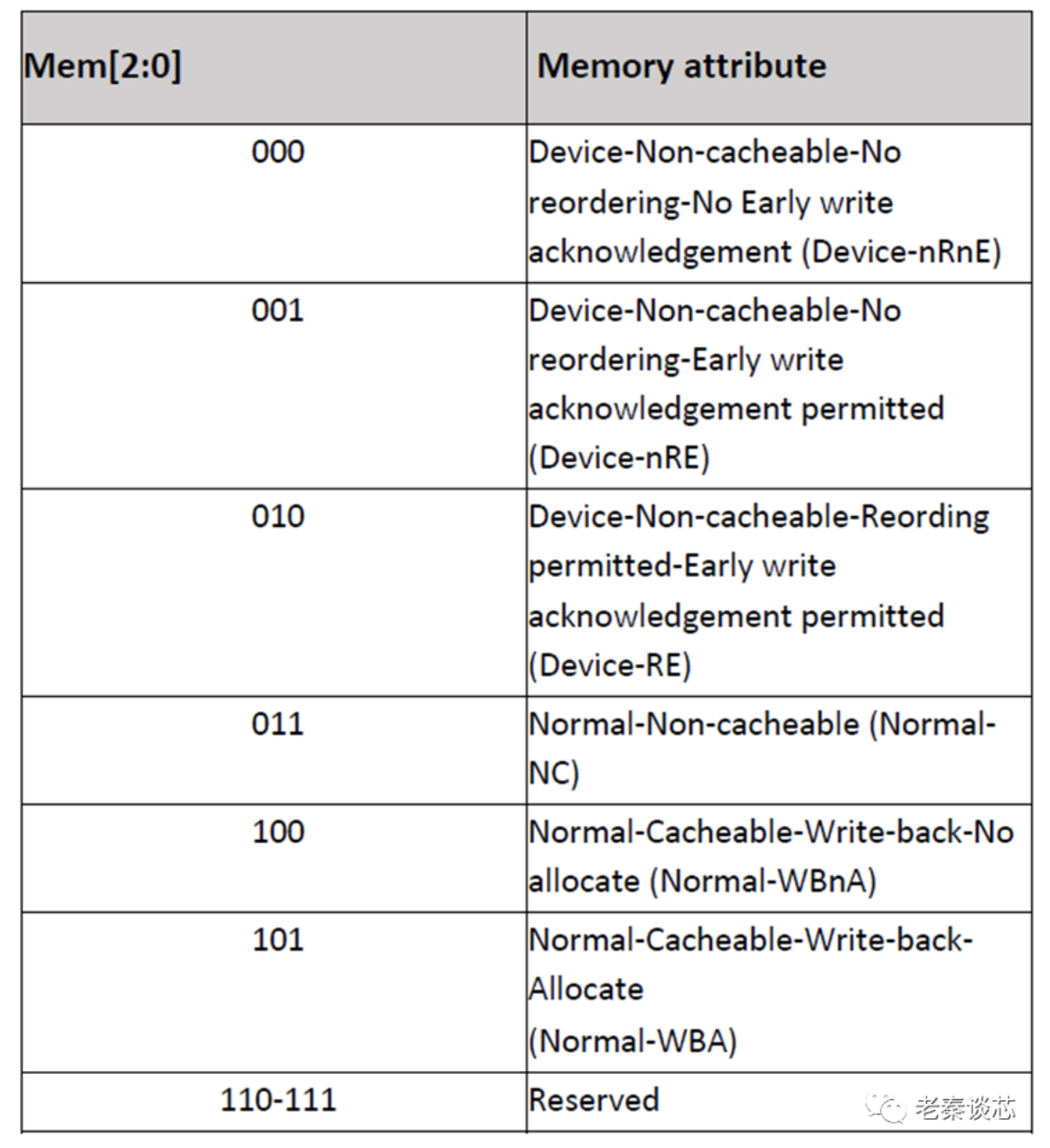

其中Mem[2:0]的定义如下:

关于Reodering,Early write acknowledge这些在之前的文章中介绍过。

至此,CCIX规范的内容大致粗过一遍,其中PCIe部分基本都略过了,有的地方介绍了一点概念性知识。真需要用到CCIX的时候,还是多看协议。

【本系列完】

老秦谈芯

老秦谈芯

推荐阅读

CCIX(八)

CPU设计之Cache -- MSHR

浅谈中断验证(一)

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。