前面的文章中经常提到Armv8-A。那么到底Armv8-A是什么东西呢?这个问题要说简单也很简单,要说复杂也很复杂。今天我们花点时间来简单研究一下。

众所周知,ARM是一家设计并授权处理器和相应IP(比如互连总线,中断处理器,图像处理器等等)的公司,目前其处理器产品分为三类:

- Cortex-A系列:这个系列主要是应用(Application)处理器,这类处理器的特点是高性能,一般支持高速缓存,乱序执行,分支预测,指令多发射等等技术。

- Cortex-R系列:这个系列主要是实时(Real-time)处理器,这类处理器的特点是对于外部事件的响应时间在可控范围,这里的实时并不是说处理器的速度快,而是对外部事件的响应时间可预测。

- Cortex-M系列:这个系列主要是微控制(Micro-controller)处理器,这类处理器一般设计相对简单,芯片规模小,功耗值低,一般作为低成本芯片的控制器使用。

这三个系列的代表字母加起来刚好是ARM,所以这应该是ARM公司故意为之的。其实ARM公司的处理器产品在很早的时候并不是这么命名的,比如很早之前的ARM9,ARM11。现在ARM的处理器产品又增加了Neoverse系列,与A系列的处理器区分开来,不过这都是后话,暂时不用管它,还是认为是三个系列好了。

再返回来说Armv8.x-A,前缀Arm不用解释了;v表示的是版本(version);8表示的是大版本号;x表示的是扩展版本号,也称为小版本号,比如8.4就是大版本是8,扩展版本是4,Armv8-A的基础版本是Armv8.0-A;最后的A表示的是A系列,所以一定还有R和M对不?不过本人对于R和M了解很少,就不介绍了,后面的内容都是以A为基础。

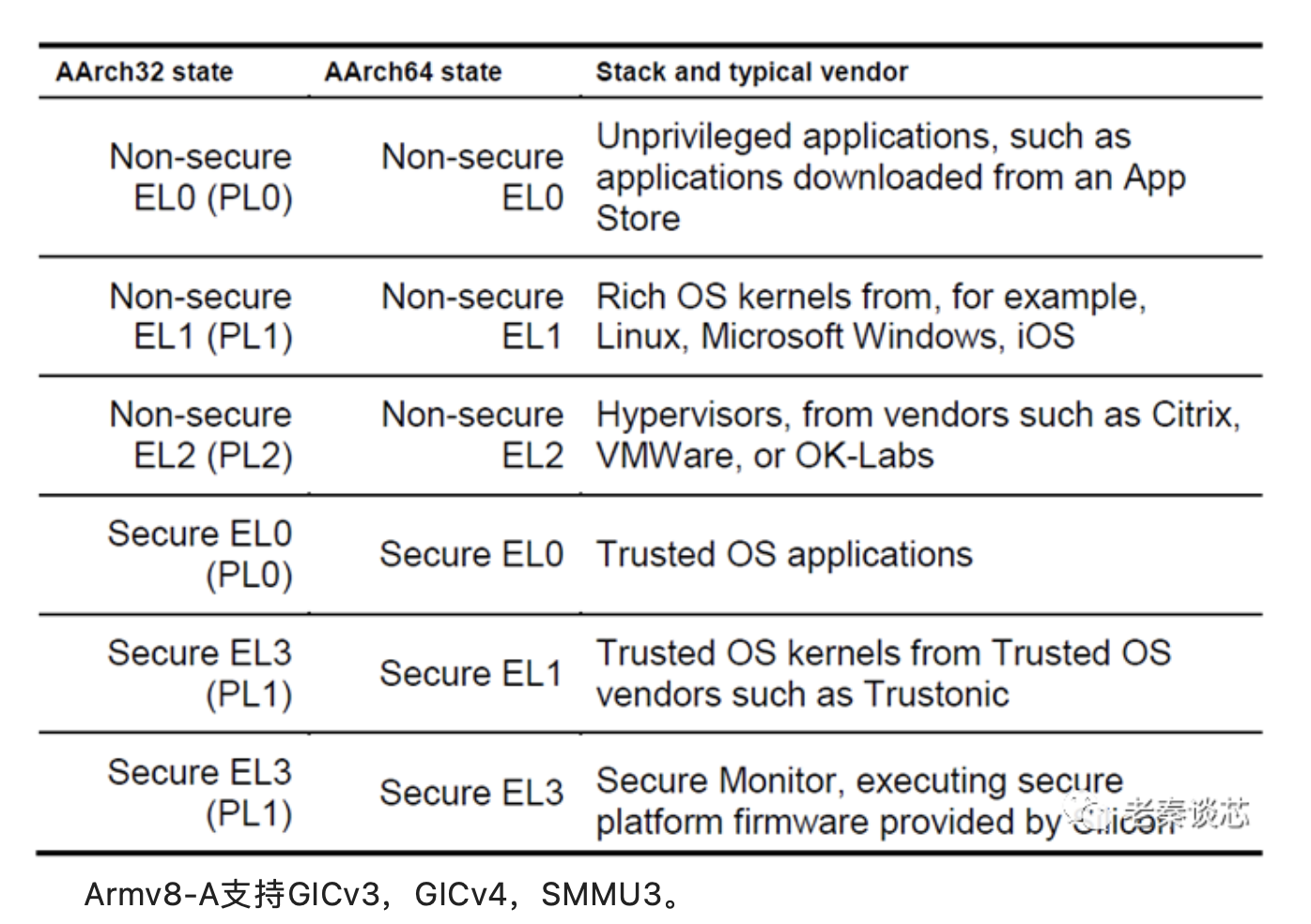

Armv8-A的执行状态有两种,AArch64和AArch32。相应的Armv8-A支持两种指令集:AArch64(A64)和AArch32,其中AArch32又分为A32和T32。A64是固定长度指令集,指令编码32-bit;A32同样是固定长度指令集,32-bit指令编码;T32是变长指令集,16-bit和32-bit指令编码。由于A32和T32主要是为了向前兼容,在Armv8-A中实际应用较少,后面内容基本都是介绍AArch64的相关内容。

AArch64中扩展了一些寄存器,包括以下:31个通用的64位寄存器 (X0-X30),处理器状态寄存器PSTATE及相关的若干寄存器,堆栈寄存器SP等等。以后会找时间专门分析一下这些寄存器。

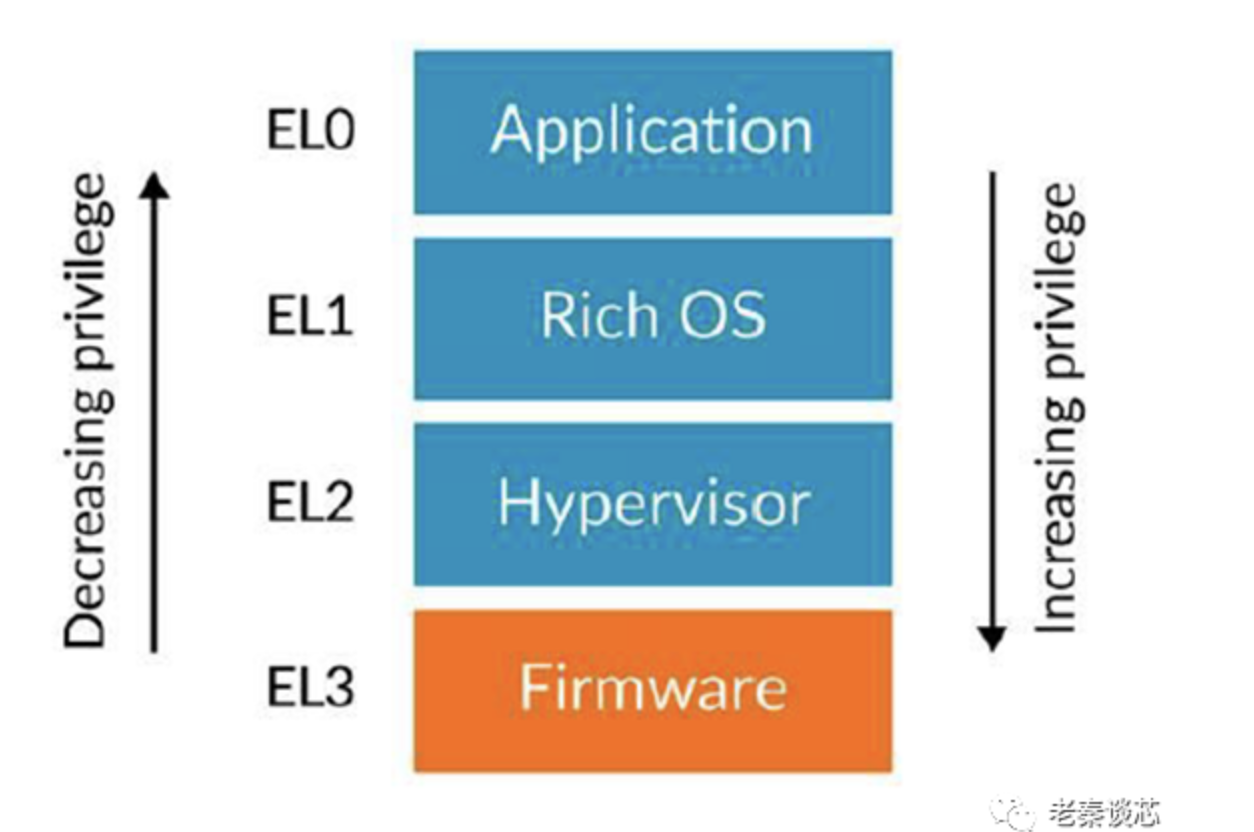

Armv8-A中定义了四种异常等级(Exception Level),这在前面的文章中重复过很多次了。

Armv8-A支持GICv3,GICv4,SMMU3。

对于其处理器具体实现的指令集,ARM有一个约定,比如某个处理器实现了Armv8.1-A,那么该处理器:

- 必须实现Armv8.0-A和Armv8.1-A强制要求的功能

- 可以实现某些Armv8.2-A中扩展的功能

- 不允许实现Armv8.3-A和更高版本扩展的功能

对于Armv8.0-A要求的功能,以后有机会慢慢分析。这不是一朝一夕能完成的,毕竟单其架构文档已经上万页了。今天先简单列一下Armv8.0-A以后的版本所扩展的功能,后面我们再慢慢分析Armv8.0-A的基础功能和这些扩展功能。

1. Armv8.1-A

- Atomic memory access instructions (AArch64)

- Limited Order regions (AArch64)

- Increased Virtual Machine Identifier (VMID) size, and Virtualization Host Extensions (AArch64)

- Privileged Access Never (PAN) (AArch32 and AArch64)

2. Armv8.2-A

- Support for 52-bit addresses (AArch64)

- The ability for PEs to share Translation Lookaside Buffer (TLB) entries (AArch32 and AArch64)

- FP16 data processing instructions (AArch32 and AArch64)

- Statistical profiling (AArch64)

- Reliability Availability Serviceability (RAS) support becomes mandatory (AArch32 and AArch64)

3. Armv8.3-A

- Pointer authentication (AArch64)

- Nested virtualization (AArch64)

- Advanced Single Instruction Multiple Data (SIMD) complex number support (AArch32 and AArch64)

- Improved JavaScript data type conversion support (AArch32 and AArch64)

- A change to the memory consistency model (AArch64)

- ID mechanism support for larger system-visible caches (AArch32 and AArch64)

4. Armv8.4-A

- Secure virtualization (AArch64)

- Nested virtualization enhancements (AArch64)

- Small translation table support (AArch64)

- Relaxed alignment restrictions (AArch32 and AArch64)

- Memory Partitioning and Monitoring (MPAM) (AArch32 and AArch64)

- Additional crypto support (AArch32 and AArch64)

- Generic counter scaling (AArch32 and AArch64)

- Instructions to accelerate SHA

5. Armv8.5-A and Armv9.0-A

- Memory Tagging (AArch64)

- Branch Target Identification (AArch64)

- Random Number Generator instructions (AArch64)

- Cache Clean to Point of Deep Persistence (AArch64)

6. Armv8.6-A and Armv9.1-A

- General Matrix Multiply (GEMM) instructions (AArch64)

- Fine grained traps for virtualization (AArch64)

- High precision Generic Timer

- Data Gathering Hint (AArch64)

7. Armv8.7-A and Armv9.2-A

- Enhanced support for PCIe hot plug (AArch64)

- Atomic 64-byte load and stores to accelerators (AArch64)

- Wait For Instruction (WFI) and Wait For Event (WFE) with timeout (AArch64)

- Branch-Record recording (Armv9.2 only)

5.8 Armv8.8-A and Armv9.3-A

- Non-maskable interrupts (AArch64)

- Instructions to optimize memcpy() and memset() style operations (AArch64)

- Enhancements to PAC (AArch64)

- Hinted conditional branches

Armv9-A是ARM公司最新的架构,但是目前还没有完全公开。

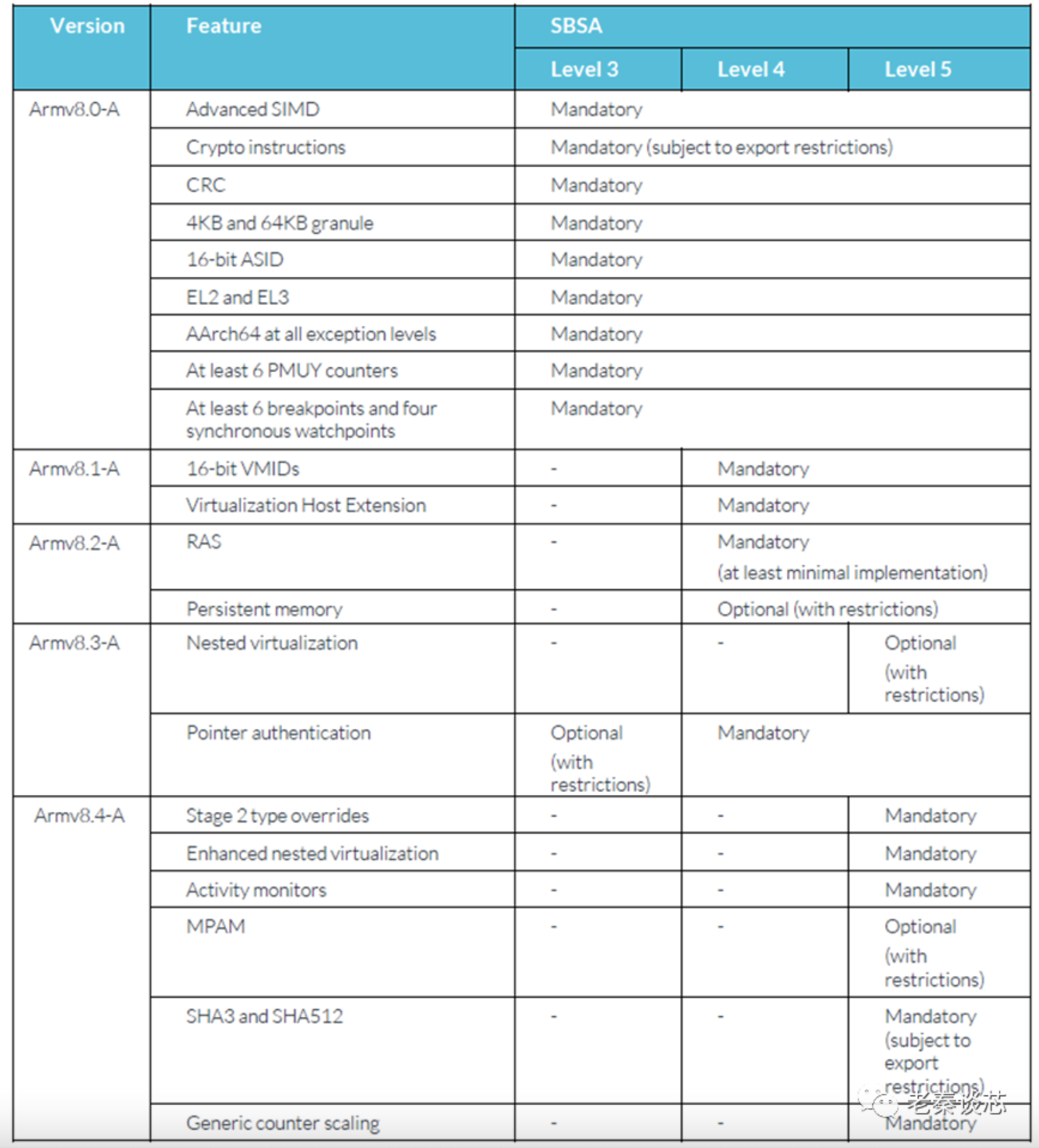

最后提一句,现在基于ARM处理器的多核服务器芯片设计正火,国内外玩家越来越多。ARM公司推出了Server Base System Architecture(SBSA)规范,提出了服务器的硬件要求。下表总结了与Armv8.x-A相关的SBSA要求。

SBSA文档是公开的,感兴趣的朋友可以去官网下载。目前我看到的SBSA文档版本是7.0,在2021年1月发布。

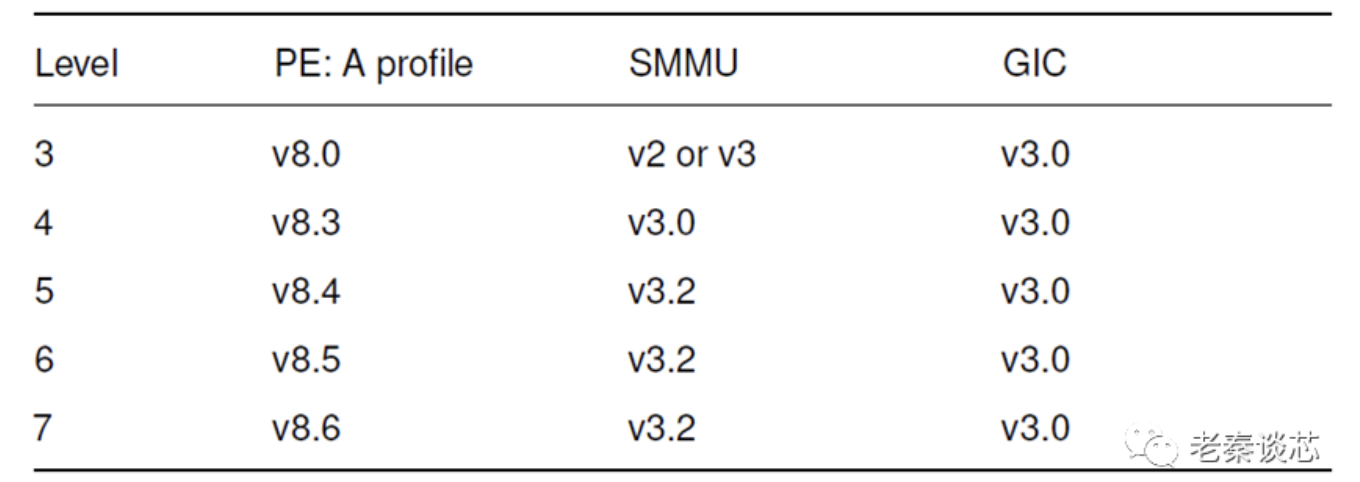

其实SBSA中就是规定了一些规则(rule),对于不同等级有不同的要求。下图是SBSA的不同等级对处理器,SMMU和GIC的要求,可以与上一张图结合看。

终于鼓足勇气,开始啃ARM架构手册。一万多页的文档,咱们慢慢来,日拱一卒,每天进步一点点。

作者: 老秦谈芯

文章来源: 老秦谈芯

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。