摘要

确保将最高质量的产品运往市场,并保证它们在其生命周期内持续工作,是汽车芯片制造商的首要目标。的确,我们需要大力改进和加强制造测试程序,以使整个芯片种群中的潜在故障少之又少。然而,高质量的生产必须遵循现场可靠性;制定战略和活动来面对前方生命周期的关键问题也具有非常高的优先地位。本文的贡献包括以下几个方面的描述和结果:(1)一种非常精确的方法来评估FLASH制造测试的功耗;(2)一种有效的多核基于软件的自检生成策略,面向人工智能的计算机体系结构;(3)一个高水平和非常快速的系统级芯片的架构仿真器,用于原型设计辐照实验和预测运动结果,对处理器和外围核心的单一事件设置具有良好的准确等级。

I.简介

详细介绍了重新调整制造测试流程的最佳做法,通过考虑克服结构测试在线限制的测试技术来达到标准预期,并节省时间和计算资源来评估利用所有系统级芯片(SoC)功能的汽车应用的稳健性,包括CPU和外围核心。

第二节介绍了如何对嵌入式FLASH存储器的制造测试进行非常准确的功率表征。正如后面所详述的那样,该技术的目标是测量一个复合DfT模式的电流吸收,该模式可以通过调整固件来满足不同的期望。为了在测试执行过程中设置正确的测试电压裕度,并允许详细说明与FLASH测试并行进行的其他测试,澄清该评估是至关重要的。Infineon科技公司报告了有关嵌入式FLASH存储器测试的数据,显示了各种测试固件版本的功耗趋势。

第三节说明了如何为一个包括几个计算核心的面向人工智能的设备创建一个基于软件的自我测试套件。网表的大小和复杂性是这个方向的主要关注点;可能的自动化和巧妙的分级程序是本节讨论的关键点。Dolphin设计公司对其汽车AI芯片所报告的结果表明,基于软件的自我测试策略是可扩展的,并适用于大型多处理器设备的适当在线测试策略。然而,产生的功能测试程序可用于补充制造测试期间的结构方法,即查看系统级测试覆盖率。

第四节完成了本文所描述的方法和策略的概述。在这一部分,重点是瞬态故障的影响,并提出了一种方法来估计可能影响整个系统级芯片(SoC)的单一事件颠覆的影响。所描述的解决方案是基于一个仿真引擎,能够快速重现包括处理器和外设核心在内的SoC的行为;在特殊情况下,Xilinx Zynq UltraScale+ MPSoC是通过使用QEMU平台进行仿真的,QEMU平台是以这样一种方式进行检测的,它可以在应用程序的执行过程中注入瞬时故障效应。通过使用这样的环境,有可能获得快速、略微不准确的关于瞬态故障对功能的影响的的估计。因此,这种方法可以对辐照实验中观察到的故障水平进行原始但非常便宜的预测。

第五节得出了一些结论,并强调了汽车主题的合理看法。

II.嵌入式FLASH的功率表征测试

每个内存测试的特点是有一定的电流消耗水平。通常,这种水平在测试执行过程中不是恒定的,而且在许多情况下,峰值可能会出现在平均水平上。了解产生这些峰值的原因是很重要的,即识别相关的IR-droop问题可能会减少矫枉过正,并使更多的测试并行化,可能允许在同一时间测试不同的芯片部件,以减少测试时间。

在这些段落中,我们专注于FLASH存储器测试,特别是寻找有关所谓的 "验证测试 "技术的功率信息,该技术旨在测试存储在片上系统(SoC)中的FLASH存储器阵列。对测试步骤中的功耗水平进行认真的调查,也可以对测试条件的余量达到更高的置信度,这也是达到大批量制造质量的一个不可缺少的因素。

随着测试场景变得复杂,超出功率限制的风险也会相应增加。如今,集成在SoC中的嵌入式可测试性设计(DFT)功能可能是非常复合的,因此功率表征可能会被所有这些组件污染。为了更好地了解每个角色者在所考虑的测试场景中的贡献,调试设置变得非常重要。在接下来的段落中,我们将描述如何收集英飞凌Aurix系统在多种条件下运行时的重要功率测量数据。

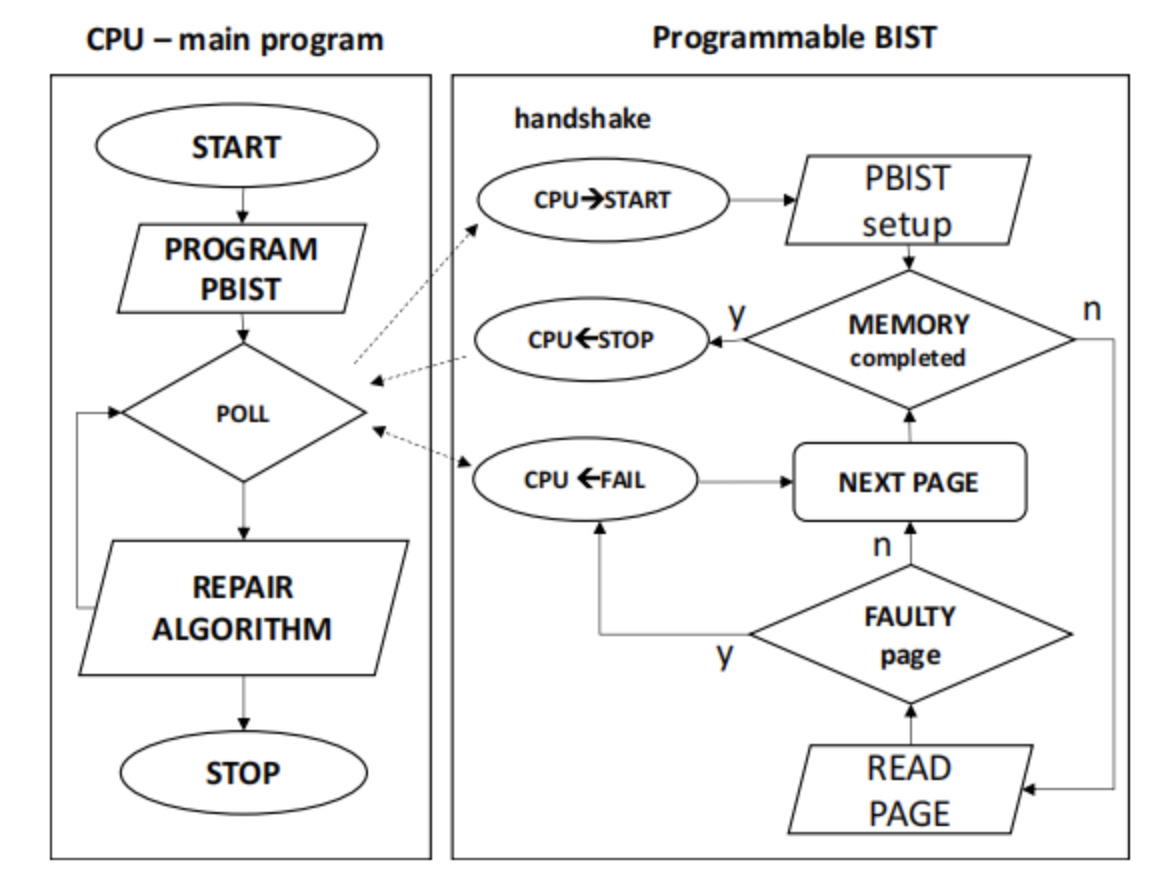

图1 总体环境和工作原则

如图1所示,Aurix FLASH存储器测试涉及许多电路。高速和背对背的访问是由一个可编程的内置自检(可编程BIST)授予的,它由一个Tricore处理器核心控制。PBIST功能允许在不同条件下进行验证测试,如内部电压和频率参数。

在我们的工作中,主要调查了CPU组件行为的影响,因为它在纯PBIST功率特性方面引入了一个额外的电流消耗因素。为了识别功率峰值并确定其最大振幅,我们评估了几个CPU固件版本。图2总结了一组测量的构架:

1) 未经优化的CPU固件版本,该版本

- a) 不断地轮询PBIST以获取故障信息

- b) 包括调试功能,如跟踪特殊用途寄存器的读写操作

- c) 实施高水平的嵌套功能,以达到重复使用的目的。

2) 减少对PBIST的轮询频率

3) 利用在轮询事件之间进入的空闲模式

4) 通过 "简化 "的代码(但不太通用)最小化上下文切换事件。

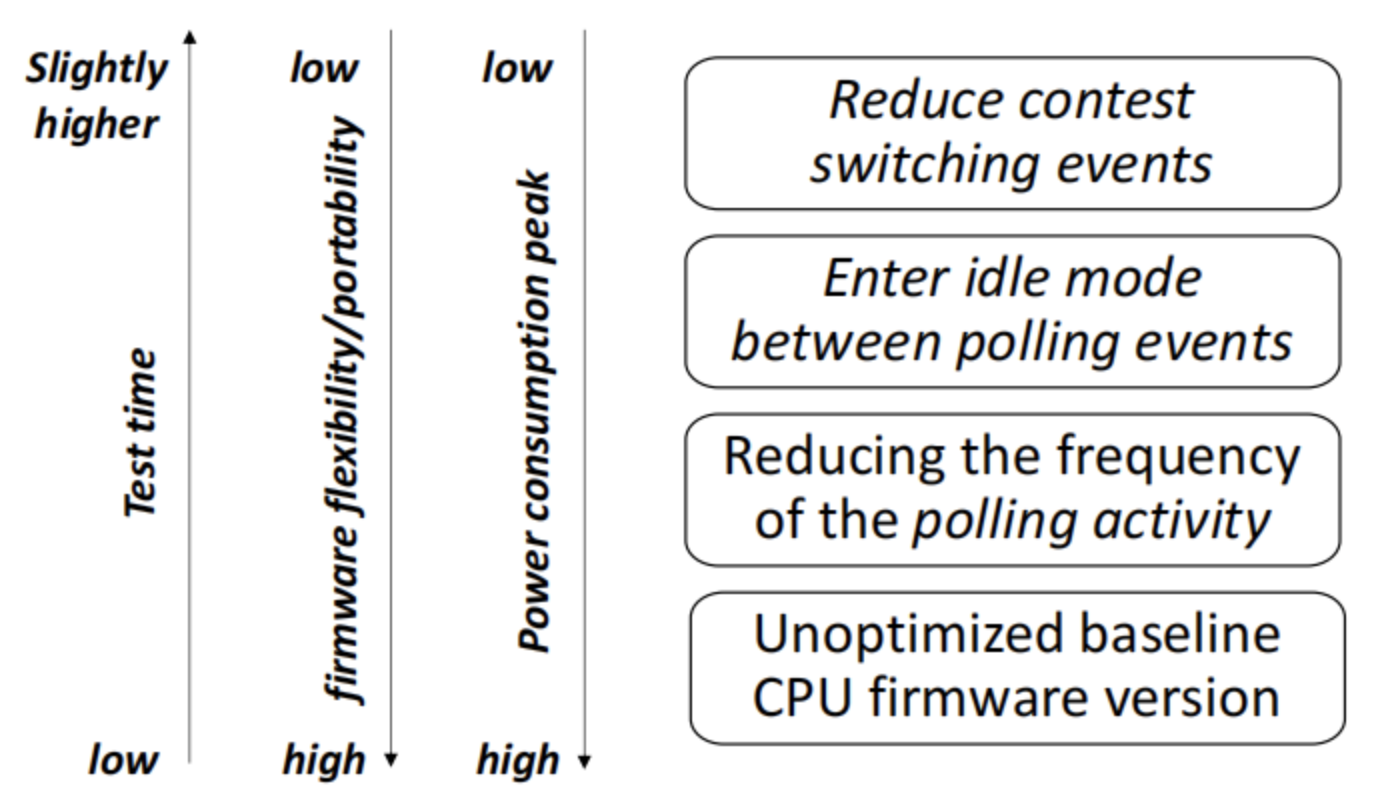

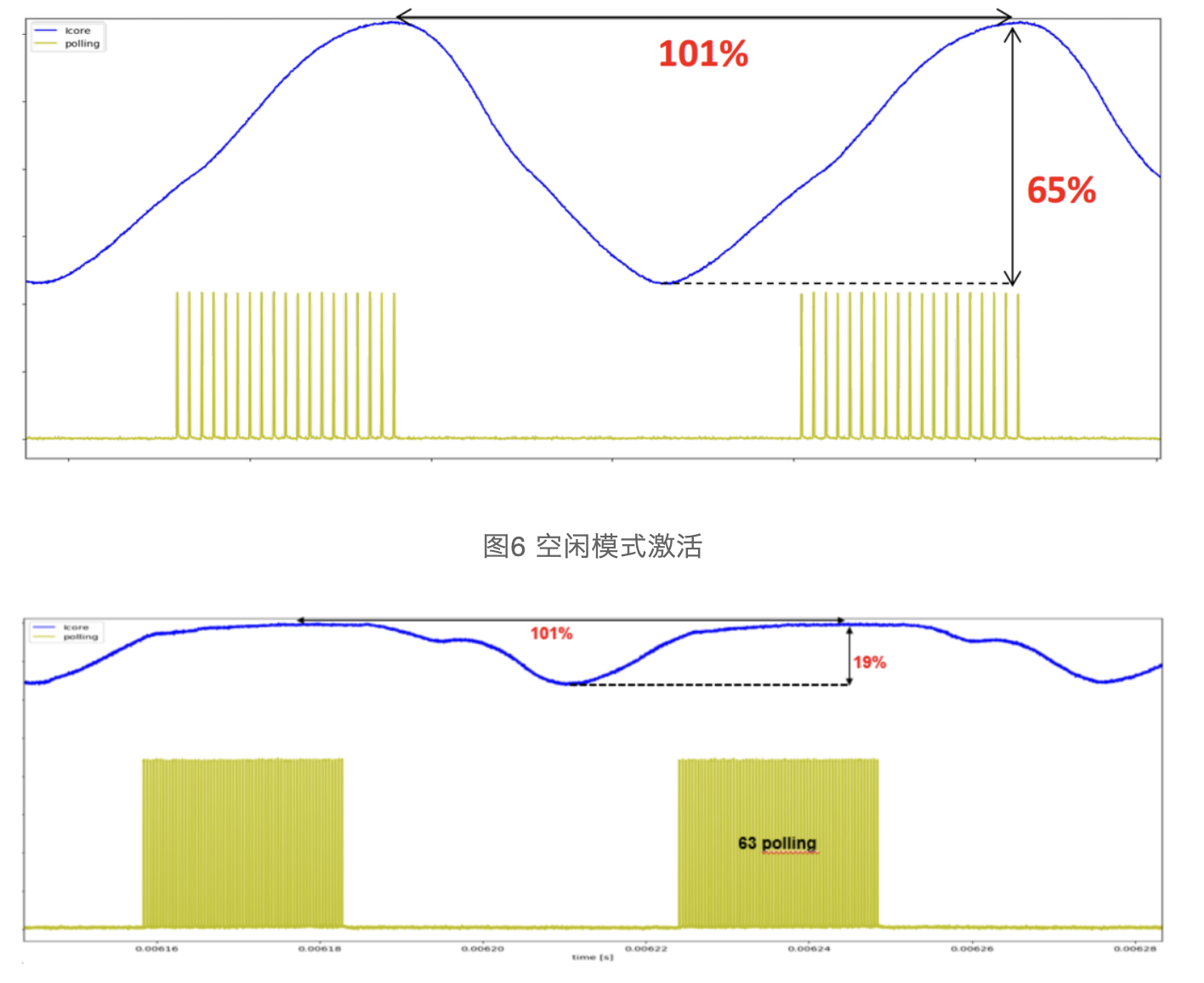

图2 固件级别探索及其利弊

图2说明了优化级别,并已经报告了一些权衡的结果。随着我们引入优化,功率消耗的峰值往往会减少很多。这是一个主要目标,但它也带来了一些重要的缺陷。在每一个优化步骤中,我们都观察到CPU固件的灵活性和可移植性的损失。同样,闲置空闲能力时。

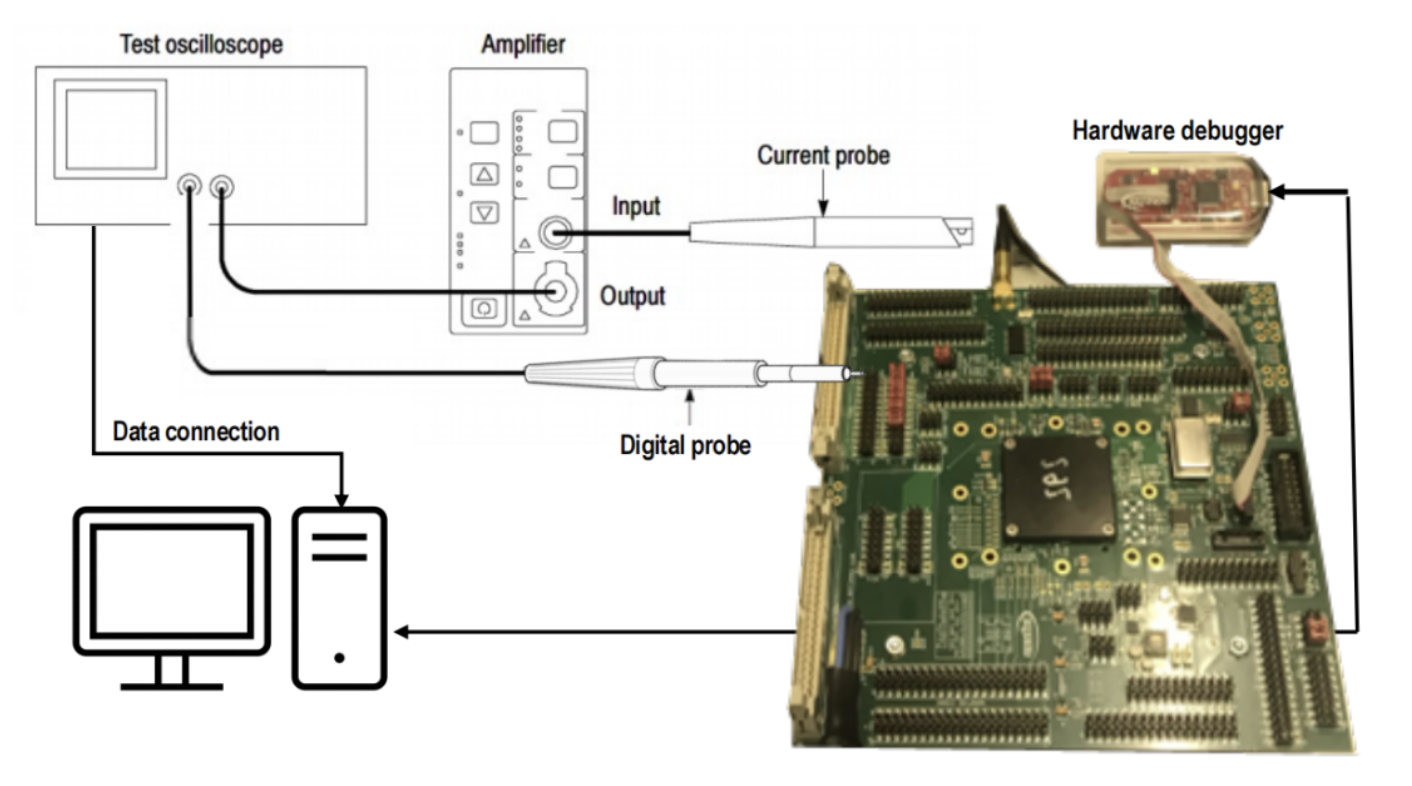

为了进行目标测量,我们准备了图3所示的装置。安装的基础是一个开发板,包括一个用于承载芯片样本的螺丝插座。这样的板然后连接到几个控制和测量工具。

图3 实验装置

一个硬件调试器被连接到电路板上,以便主机启动和控制CPU功能的执行。

然后,电路板通过两种类型的探头连接到示波器上。电流探头用于测量测试执行过程中的电流变化:这种探针 "窥探 "了沿测试执行过程中给磁芯供电的电源线。此外,一个数字探针被用来捕捉数字引脚的值。这种操作对于确定正确的时间来观察测试流程中的功耗变化非常重要。在以下图表中,我们报告了与FLASH存储器两个连续扇区的测试有关的测量。数字探头用于识别轮询间隔,用黄色报告,而用电流探头测量的功耗趋势用蓝色报告。

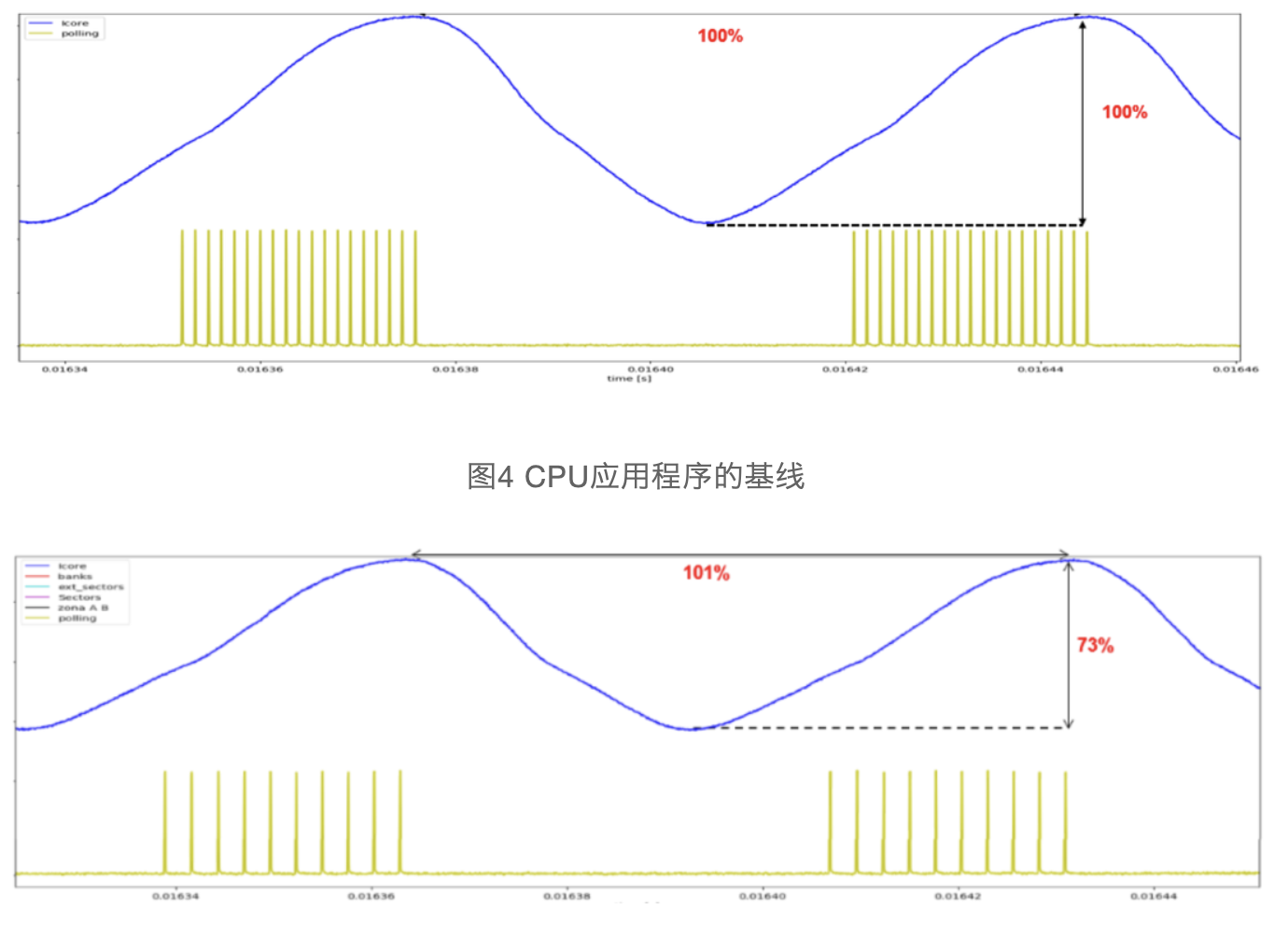

图4显示了基线CPU固件的应用。我们用百分比来做一个公平的比较,在这种情况下,功率峰值振幅和测试时间是100%。

图5 减少轮询活动频率

图7 减少了上下文切换事件

总的来说,我们观察到,有几种方法可以用来减少功率峰值的振幅,这对于安全地规划其他测试与FLASH内存测试程序的并行化至关重要。以灵活性和可移植性为代价,减少CPU的 "无用 "活动(例如,通过减少代码中对函数的嵌套调用数量来最小化上下文切换)看起来是最有效的方法,它对测试时间没有影响。

另外,基于空转的方法可以节省较少但显著的电流输入,并且对测试时间影响有限。

III.基于软件的自测试开发和AI芯片的分级

汽车的功能安全标准,如ISO26262,要求使用硬件和软件技术对潜在的故障进行现场测试。基于软件自检(SBST)的软件测试库(STL)是一种灵活的潜伏故障测试解决方案,可替代基于可测试性设计(DfT)特征的硬件方法。STL可以被集成到任务操作系统中,并在空闲时间定期执行。然而,在为基于多核处理器的人工智能芯片开发STL时,彻底优化故障分级过程和用适当的软件模块管理STL的执行是至关重要的。

在下面的小节中,描述了经典案例,STL的开发策略,以及如何将它们集成到系统中。最后,展示了故障仿真结果。

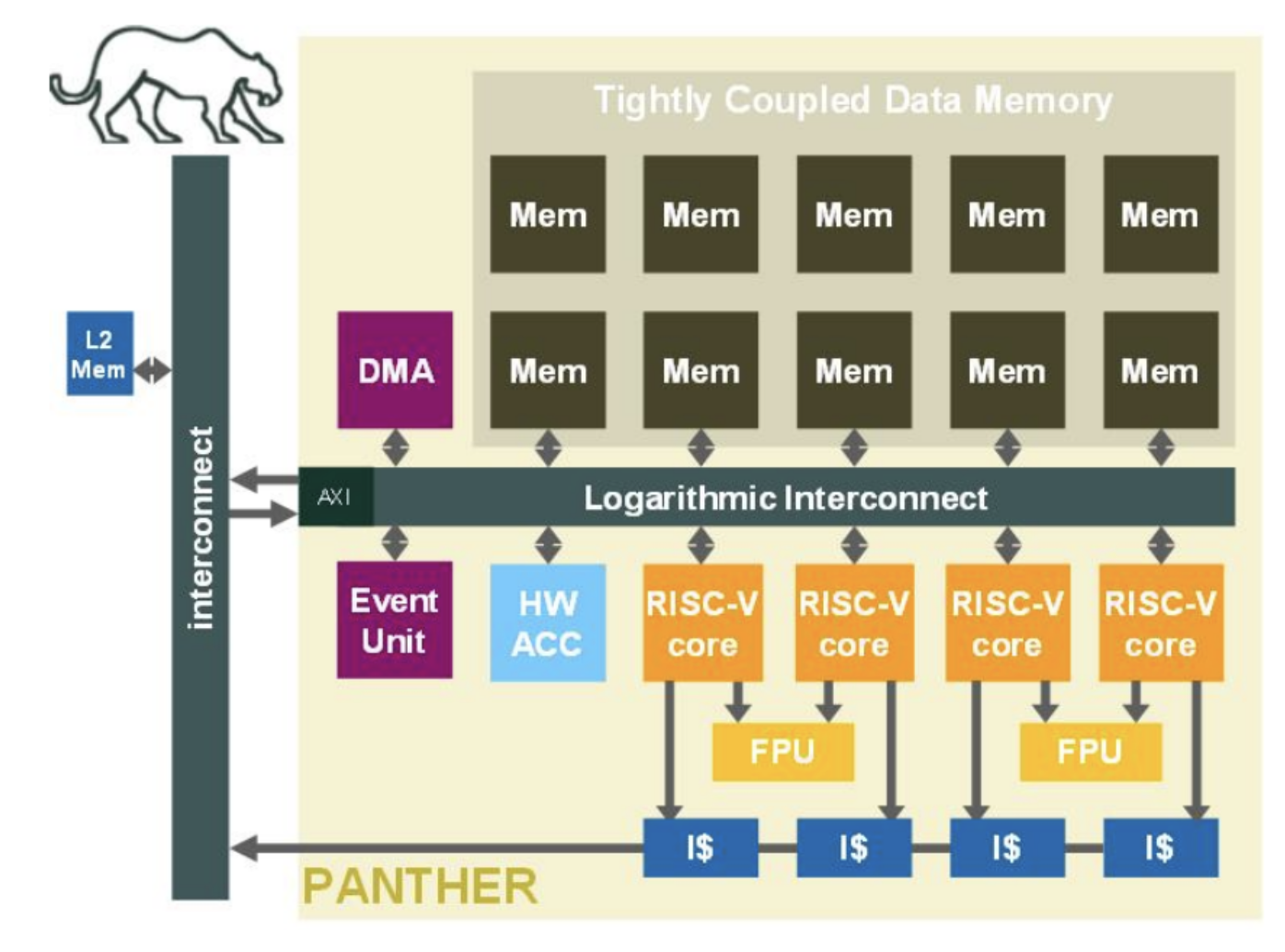

A.经典案例

该经典案例是由Dolphin Design公司开发的一个多核人工智能芯片,用于加速神经网络所需的操作(见图1)。该模块包括一个由16个PULP-NN RISC-V核(Core0 - Core15)组成的集群,有128kB的L1内存。指令是在一个与集群外的二级存储器通信的指令缓存内获取的。外部总线提供了与内部L1的通信,并可由核心0或通过DMA访问。内部总线负责连接所有的内部模块,为并发的访问提供调解。事件单元提供硬件事件来协调集群内部的操作。最后,一个共享浮点单元(FPU)包含8个计算核心,用于浮点之间的“经典”操作,以及一个用于DIV和SQRT的计算核心。

图8 多核AI设计框图的案例研究

软件开发工具包(SDK)可用于配置和编程SoC。使用SDK,用户可以决定如何安排测试和组织测试程序作为操作系统(OS)的任务。

B.STL 开发

整体的STL开发被分割成几个测生成,使用较小的故障列表。一些模块(如CPU核,或FPU共享子单元)被多次复制,可以通过专注于一个模块,然后通过在其他模块上做测试程序的移植来解决。关注每个子模块可以减少执行故障模拟和评估目标模块测试程序质量所需的时间。对于特定部件,为其他模块开发的测试产生的副作用是不可忽略的(例如,在互连的仲裁和多路复用逻辑上); 通过在目标模块上模拟这些测试程序,可以精简故障列表,减少生成时间。

测试策略包括在对RTL设计进行仔细分析后,使用伪随机和ATPG约束方法产生的模式。每个测试程序首先通过考虑所有子模块的主要输出(Pos)进行故障模拟,并细化直至达到目标故障覆盖率;最后对程序进行重新模拟,掩盖数据结果传播过程中所没有的所有POs;测试程序将测试结果压缩为一种形式的签名,保存在内存位置,并在测试结束时与预期的结果进行比较。

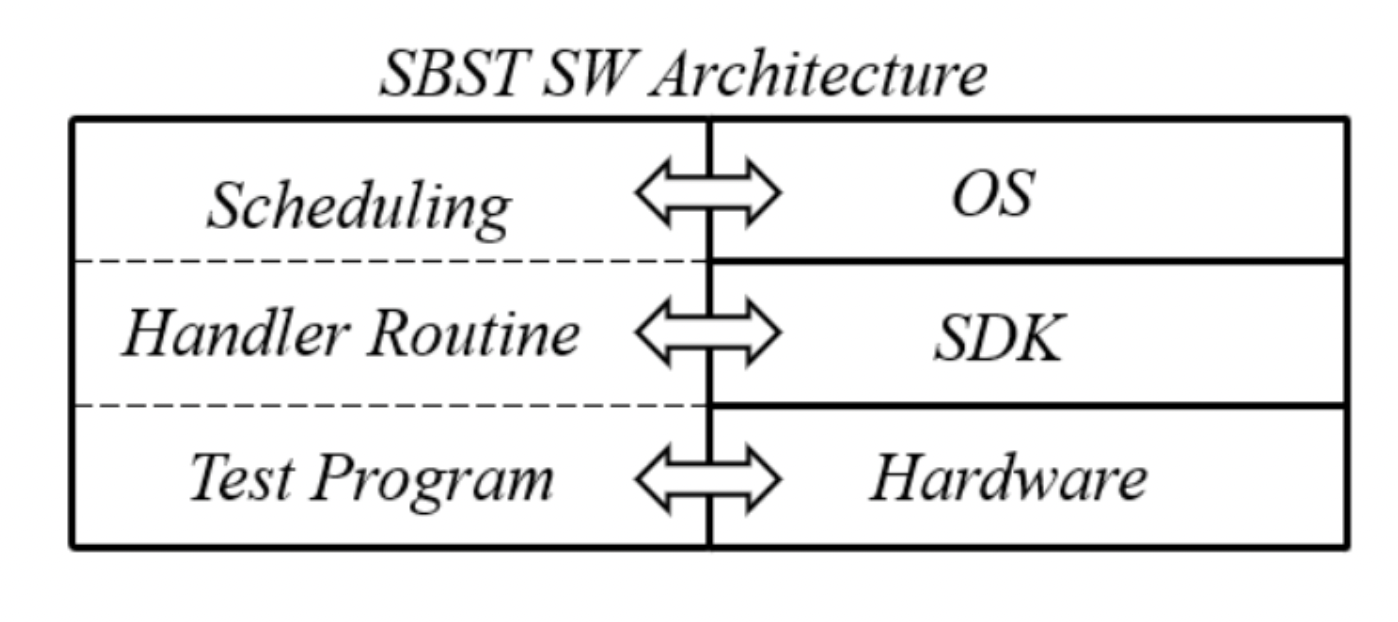

C.STL 集成

软件测试库的结构分三个层次,如图9所示:

1) 最底层包括用C语言和汇编开发的测试程序,以更好地运行内部模块。

2) 中间层直接与SDK进行沟通,以协调和评估整个集群内的测试操作。

3) 最高层与操作系统同时工作,在任务运行期间安排测试阶段。

图9 STL架构

为了保证稳健性,软件必须考虑到所有可能的故障,这些故障的存在会导致系统死锁:

● 当测试操作启动时,软件会使用内核软件提供的适当程序来处理上下文切换。

● 由于在失败的情况下会出现异常,所以必须修改相对处理程序,以便与影响测试结果的测试软件沟通。

● 最后,在开始测试阶段之前,必须初始化一个看门狗定时器,以便在发生不可预见的事件时强制停止测试。

测试程序的并行执行是通过在L1内存中保留一个专用空间来实现的,其中包含有关测试程序状态的参数结构。通过访问这些内存区域,可以利用内核功能在内部集群核心和外部之间进行同步操作。

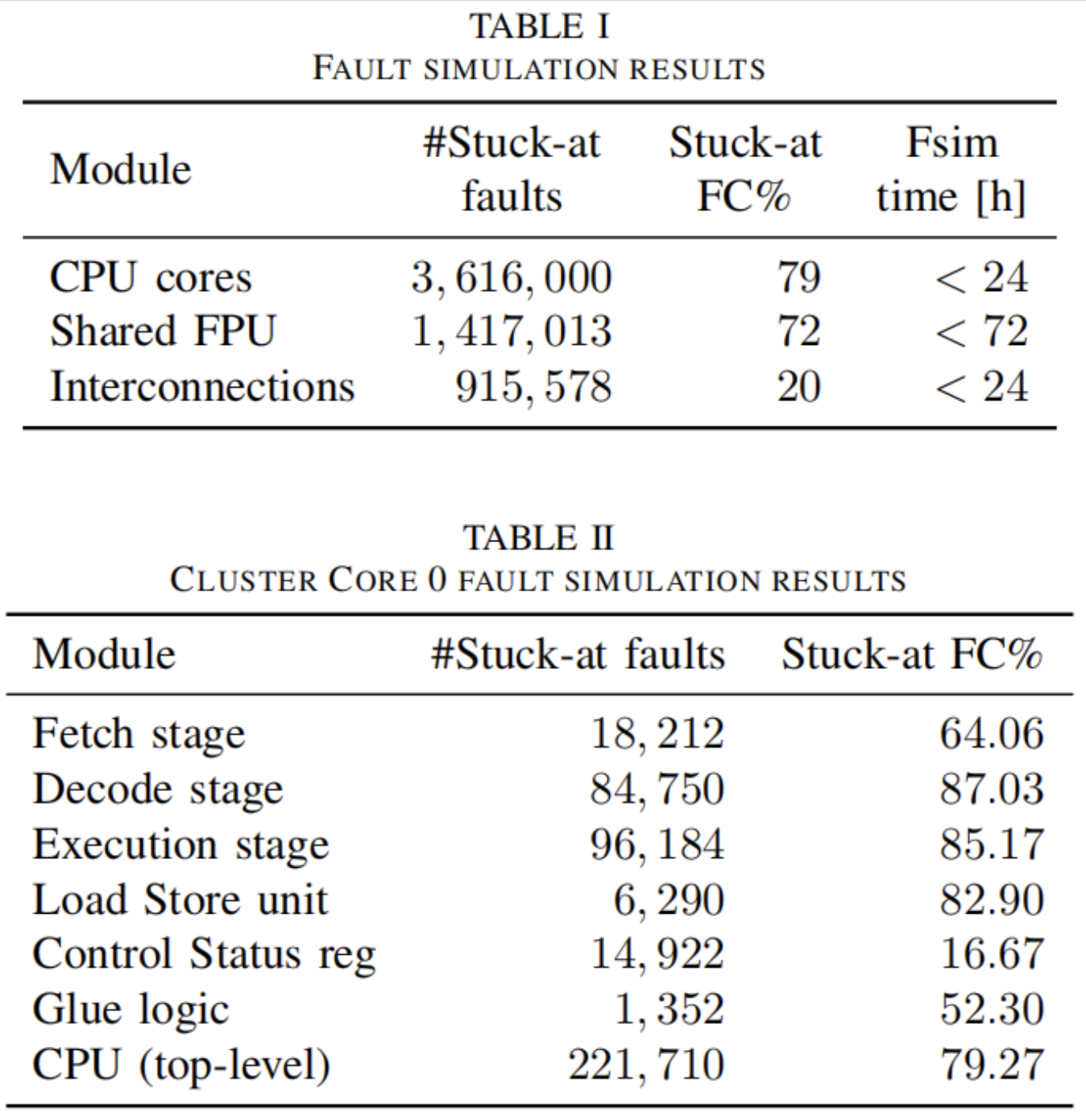

D.故障模拟结果

实验是在Xeon Gold 6126工作站的4个核心上使用商用顺序故障模拟器进行的,该工作站配备128GB RAM。

在对每个集群的子模块进行故障仿真后,通过逻辑仿真验证了STL的功能;为了加快这一过程,使用RTL描述对外部芯片进行仿真,同时为集群保留门级。

表一报告了16个CPU核、FPU和互连的故障模拟结果。对于每个模块,我们报告了卡住故障的数量、故障覆盖率和故障模拟时间。

该表显示,所有内核区域的故障覆盖率都很好,共享FPU的故障覆盖率为离散值。我们通过运行为其他区块编写的测试程序来计算互连上的FC。

表二中报告了一个CPU核心(Core 0)的子模块的细节。其他CPU核显示了类似的结果,尽管故障列表有轻微的差异。

整个STL在16个CPU核心上同步运行的测试应用间在100MHz下约为8ms,大小约为20KB,这验证了在实时系统的现场测试中采用这种测试技术的可能性。

IV.用于汽车应用可靠性评估的高级故障注入

在接下来的段落中,描述了一种基于高级软件仿真和QEMU仿真引擎,快速评估复杂SoC上单次事件颠覆(SEU)影响的方法。这一策略被用来对运行在Xilinx Ultrascale+ MPSoC上的几个应用进行分级。SEU是由电离粒子击中SoC中的敏感点(如CPU寄存器、外设寄存器或互连)而引起的位缺陷。根据执行的程序和涉及的外围模块,这些位缺陷可能会对系统造成影响。

评估SEU对运行在特定设备上的应用的影响通常是一项非常困难的任务。辐照测试,即设备在离子流下运行,是最精确的测量,但也非常昂贵。此外,在离子流下的实验失败可能会导致沉重的额外费用。无论如何,测试和可靠性工程师需要提前验证他们的实验流程,以证明准备的设置是有效的,不会导致收集无用的数据。

在这方面,基于仿真的方法近年来被广泛使用;在这种情况下,需要使用网格列表,而实验在CPU时间和内存方面要求极高,往往导致不可行。因此,进一步减轻这些初步评估成本正成为一个首要目标。我们建议采用一种替代性的模拟方法,以软件仿真为代表。软件仿真器,如QEMU引擎,运行的不是电路的一对一模型,而是程序员对设备的模型行为的精确模型,并非常迅速地再现系统的功能。

当使用仿真器时,程序员仍然可以看到用户手册中描述的所有寄存器,这些值与真实电路的行为是一致的。

这是提出的方法的出发点。我们对Xilinx Ultrascale+ MPSoC的QEMU版本进行了检测,在CPU和外围模块的寄存器中注入SEU。

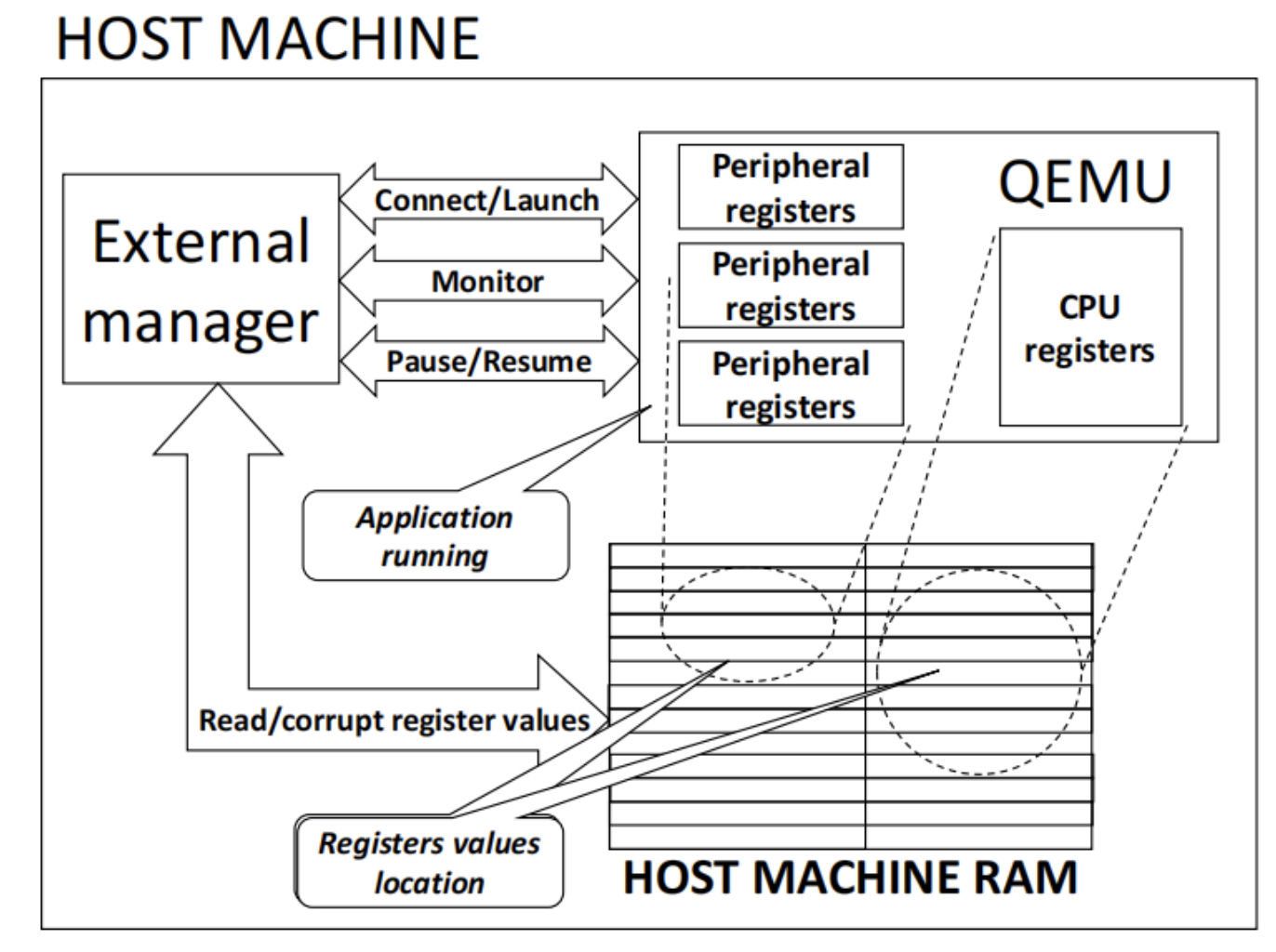

图10 总体环境和工作原理

图10说明了该方法的总体情况。我们开发了一个外部管理器,它连接到QEMU进程,以启动应用程序的并监测其行为。外部管理器还负责处理SEU的注入,方法是暂停应用程序,破坏其中一个可用的资源(通过作用于主机RAM内存内容),并恢复正在运行的程序的执行,以观察故障效应是否导致故障发生。

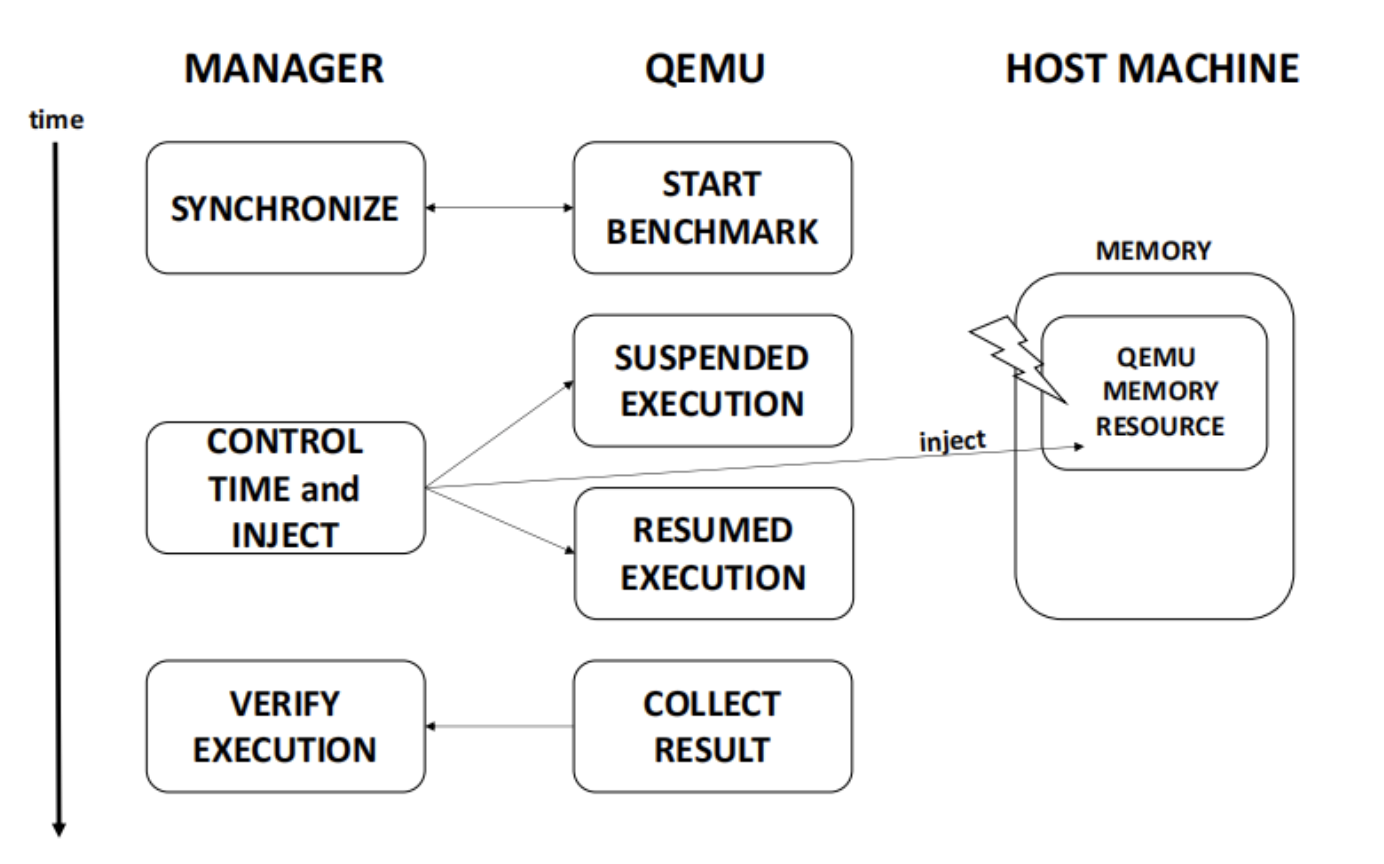

图11进一步说明了注入流。 外部管理器暂停TA的执行并注入一个故障。然后,它恢复执行并监控结果。结果被分成三类:错误的回答、没有效果、和基于程序运行结果的超时。

图11 基于QEMU的注入方法的总体视图

重要的是要注意,故障注入不仅是在CPU寄存器上进行。我们的环境可以注入映射在设备内存中的外围寄存器。在下面的实验结果中,将看到一些破坏其中一个集成DMA的寄存器的例子。我们在一个 Fast Fourier Transform (FFT)程序上实验了这个设置,该程序也与它的反FFT程序相连接。我们也用它来验证关于SoC外围设备注入的环境。

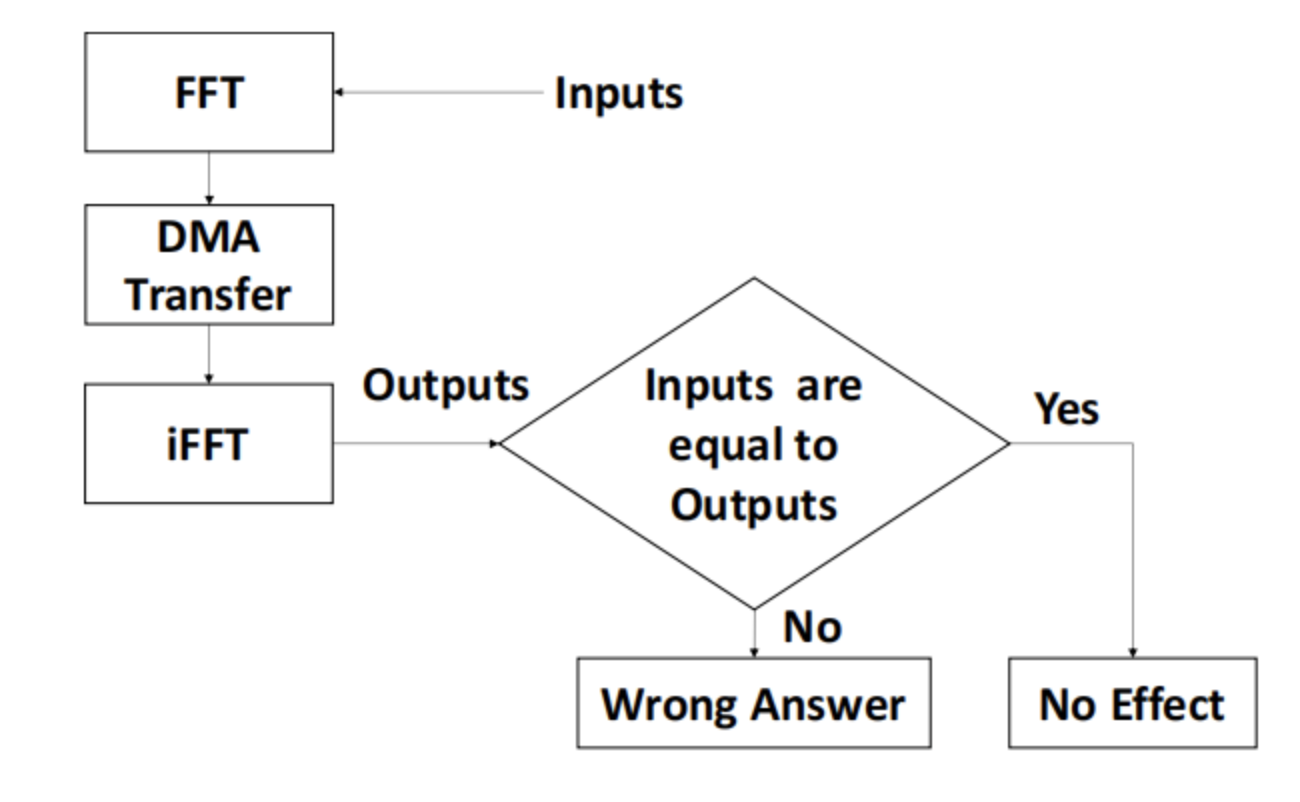

图12展示了应用程序的流程。在一个循环中,执行以下一组操作:

1) 所用的CPU对给定的一系列数值执行FFT,产生结果值

2) 触发DMA传输,将FFT的结果移动到内存中的一个新位置

3) 然后通过使用转移的FFT结果执行iFFT

4) 最后将iFFT结果与原始结果进行对比测试。

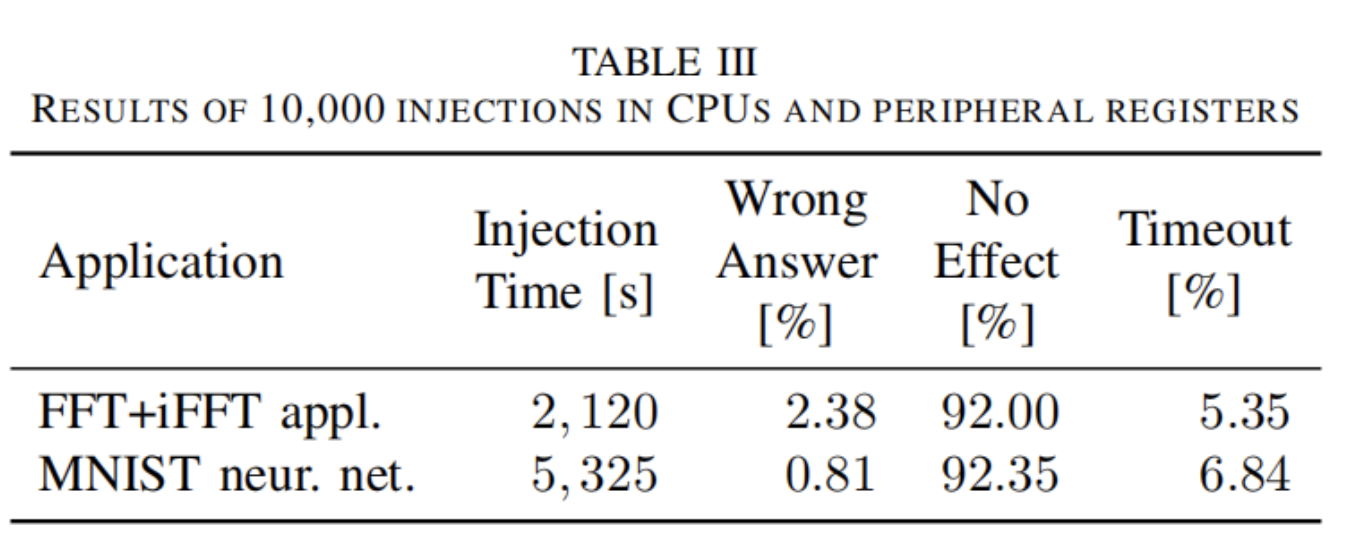

如果这个最终的检查结果显示最终的数值与原来的不同,那么就有一个错误的答案。如果程序进入了循环或陷阱,那么就有一个超时。其他的所有情况下,归结为无效果。表三 包括在随机寄存器和随机时间点中注入10000个SEU的结果,这些结果收集在一个故障列表中。在注入每个SEU后,观察程序运行的结果。然后重新启动系统,继续处理故障列表中的下一个SEU。

图12 FFT+iFFT应用

从表中可以看出,注入10,000个故障需要35分钟左右,主要是因为超时的数量相对较多。此外,我们对一个神经网络应用的软件实施了注入故障,该软件经过训练,可以识别来自修改后的国家标准和技术研究所(MNIST)数据库的手写数字。

与没有错误的黄金执行相比,我们将每个做出不同猜测的执行都标记为错误答案。从表III中可以看出,神经网络似乎对SEUs很有弹性,在10,000次随机注入的CPU寄存器上,只有0.81%的错误答案。注入的时间达到89分钟。这是由于要执行的程序的复杂性,以及发现的超时次数造成的。

作为最终数字的验证,并了解用QEMU模拟得到的结果是否能代表辐照测试结果,我们将其与[13]中的结果进行了比较,并观察到有很强的相关性。当然,仿真不能取代辐照活动,但它可以用来描述即将被辐照的应用的特征,或对许多应用进行比较,以预测哪一个是最敏感的。

综上所述,该方法允许在辐照实验前快速运行应用程序评估,以预测应用程序本身的敏感性或表征技术,或在部署用户应用程序之前。

值得注意的是,这种方法不需要芯片的网表,因此既可以被芯片供应商采用,以提前表述其设计,也可以被终端用户采用,后者可以快速运行其应用程序,并在辐照芯片之前获得近似的结果进行分析。

V.结论

本文描述了汽车领域的重要参与者所使用的一些方法和技术,以达到不可缺少的可靠性水平要求的最新标准。图示的典型案例与汽车芯片在其生命周期中所包含的几个测试阶段有关,包括制造结构和功能测试,以及确保在现场使用期间有可靠行为的方法。

作为一个经验教训,对最合适的测试程序进行准确的评估和规划,可以使高质量的汽车产品符合半导体生产商以及更高层次的期望。

参考文献:

[1] H.-G. Stratigopoulos, F. Su, A. Coyette, C. He, E. Faehn, and D. Tille, “Panel: “New automotive design methodologies for catching latent defects and detecting anomalies online”,” in 1st Automotive Reliability and Test in Europe (ARTe 2021), 2021.

[2] A. Ciarci, D. Tille, and P. Bernardi, “Towards an Automated Flow for Implementation of Dedicated LBIST Scan Chains for Functional Safety,” in 33rd GI / GMM / ITG-Workshop Test Methods and Reliability of Circuits and Systems, 2021.

[3] S. Ravi, “Power-aware test: Challenges and solutions,” in 2007 IEEE International Test Conference, 2007, pp. 1– 10.

[4] N. Mamikonyan, N. Melikyan, and R. Musayelyan, “IR Drop Estimation and Optimization on DRAM Memory using Machine Learning Algo- rithms,” in 2020 IEEE East-West Design Test Symposium (EWDTS), 2020, pp. 1–4.

[5] A. Manzini, P. Inglese, L. Caldi, R. Cantoro, G. Carnevale, M. Coppetta, M. Giltrelli, N. Mautone, F. Irrera, R. Ullmann, and P. Bernardi, “A Machine Learning-based Approach to Optimize Repair and Increase Yield of Embedded Flash Memories in Automotive Systems-on-Chip,” in 2019 IEEE European Test Symposium (ETS), 2019, pp. 1–6.

[6] ISO, “Road vehicles – Functional safety,” 2011.

[7] P. Bernardi, M. Grosso, E. Sanchez, and O. Ballan, “Fault grading of software-based self-test procedures for dependable automotive applica- tions,” in 2011 Design, Automation Test in Europe, 2011, pp. 1–2.

[8] A. Garofalo, M. Rusci, F. Conti, D. Rossi, and L. Benini, “PULP- NN: accelerating quantized neural networks on parallel ultra-low-power RISC-V processors,” Philosophical Transactions of the Royal Society A, vol. 378, 2019.

[9] P. Bernardi, R. Cantoro, S. De Luca, E. Snchez, and A. Sansonetti, “Development Flow for On-Line Core Self-Test of Automotive Micro- controllers,” IEEE Transactions on Computers, vol. 65, no. 3, pp. 744– 754, 2016.

[10] F. Wang and V. D. Agrawal, “Single Event Upset: An Embedded Tutorial,” in 21st International Conference on VLSI Design (VLSID 2008), 2008, pp. 429–434.

[11] L. Cassano, H. Guzman-Miranda, and M. A. Aguirre, “Early assessment of SEU sensitivity through untestable fault identification,” in 2014 IEEE 20th International On-Line Testing Symposium (IOLTS), 2014, pp. 186– 189.

[12] E. Jenn, J. Arlat, M. Rimen, J. Ohlsson, and J. Karlsson, “Fault injection into VHDL models: the MEFISTO tool,” in Proceedings of IEEE 24th International Symposium on Fault- Tolerant Computing, 1994, pp. 66– 75.

[13] O. Ballan, P. Maillard, J. Arver, C. Smith, R. Petersson, A. Griessing, and F. Venini, “Evaluation of ISO 26262 and IEC 61508 metrics for transient faults of a multi-processor system-on-chip through radiation testing,” Microelectronics Reliability, vol. 107, p. 113601, 2020.

END

作者: L. Degli Abbati

来源:智能汽车开发者平台

微信公众号:

推荐阅读:

更多汽车电子干货请关注汽车电子与软件专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。