FPGA项目开发之时钟规划

当我刚开始我的FPGA设计生涯时,我对明显更小、更不灵活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常简单的时钟规则之一是尽可能只使用单个时钟。当然,这并不总是可能的,但即便如此,时钟的数量仍然有限。

多年来,当我们转向功能更强大的设备和工具后,我们经常能发现自己的设计具有复杂的时钟结构,其中包括有源同步设备,如连接到处理器的 AXI 时钟、信号链时钟,并且需要处理跨时钟域问题(在视频应用中尤其常见)。

这意味着我们有一个复杂的时钟环境——一个很容易出现时钟错误的环境。这将导致时序很难收敛或更产生糟糕的情况,例如引入无意的时钟域交叉错误,从而导致数据或控制信号跟随损坏。

我们将从 7 系列FPGA开始我们的旅程。当我们考虑时钟规划时,我们需要确保使用设备内最合适的资源并了解其内部时钟架构。我们只需要简单的确保时钟信号连接到 IO 上适当的时钟引脚的日子已经一去不复返了。

时钟规划有两个方面。第一个来自设计本身的架构。在这里,在这个架构中,我们决定设计有多少时钟以及它们之间的关系。理想情况下,除了尽量减少使用的时钟数量外,我们还希望尽可能少地执行跨时钟域。

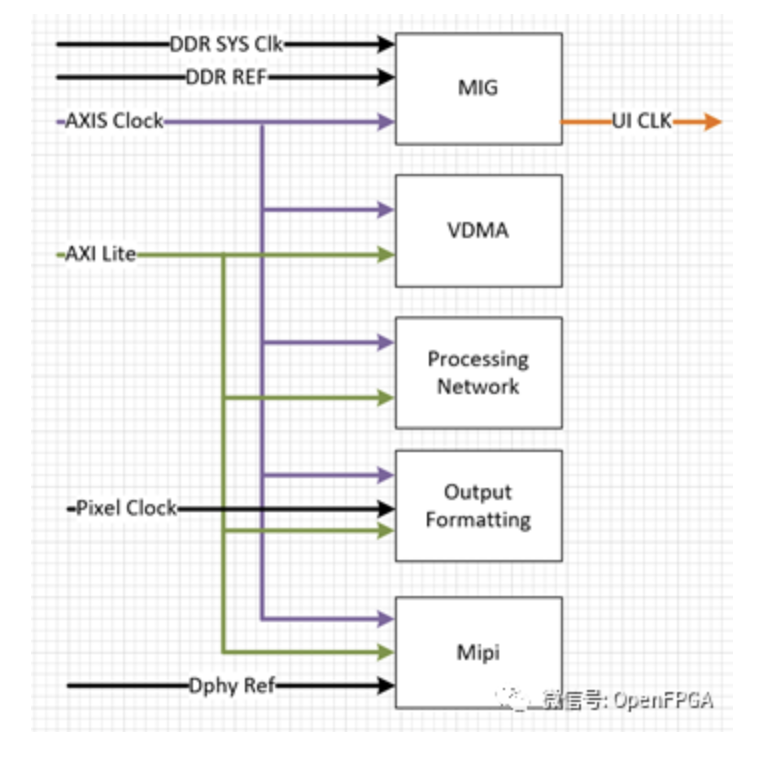

正是在这个时钟规划期间,我们可以绘制我们的初始时钟架构和相关的复位架构。时钟架构也是我们展示时钟域之间交互的地方,这是我们在编写第一行 HDL 或打开 Vivado 之前应该创建的东西。我们可以从一个简单的图表开始,如下图所示,它显示了主要时钟元素,然后随着设计的发展而进一步细化这个图。

一旦我们有了时钟架构,我们就可以将这些时钟映射到目标设备的资源中。7 系列器件具有以下范围的时钟资源。

- 支持时钟的输入引脚(Clock capable input pins)——支持单个或多个时钟区域

- 全局时钟(Global clocks )——能够为整个设备提供时钟

- 区域时钟(Regional clocks)——能够为一个区域(和相邻区域)的时钟提供时钟

- IO 时钟(IO clocks)——能够为 IO 结构提供时钟

- 时钟管理模块(Clock management tiles)——提供先进的时钟结构,例如 MMCM 和 PLL

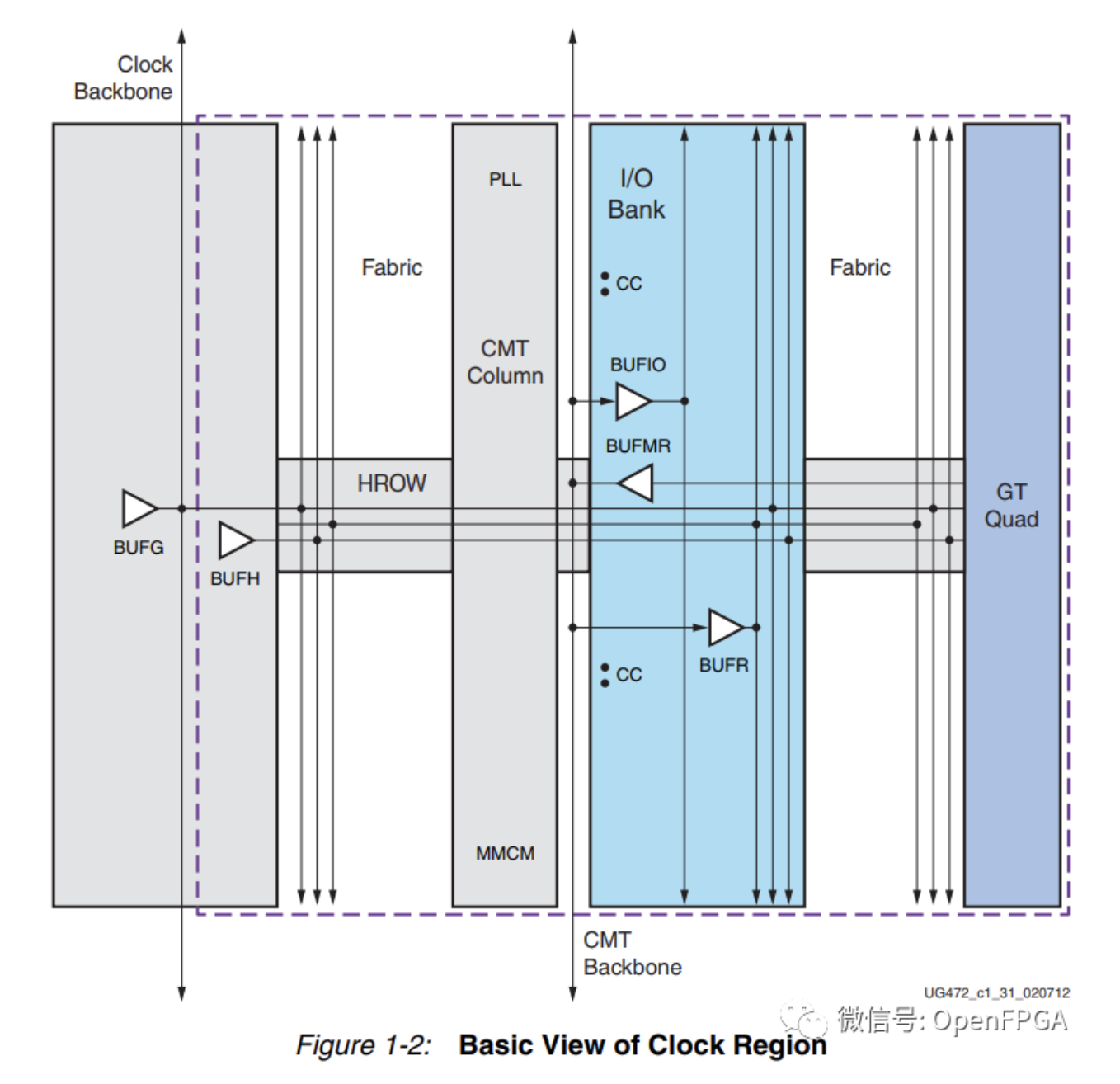

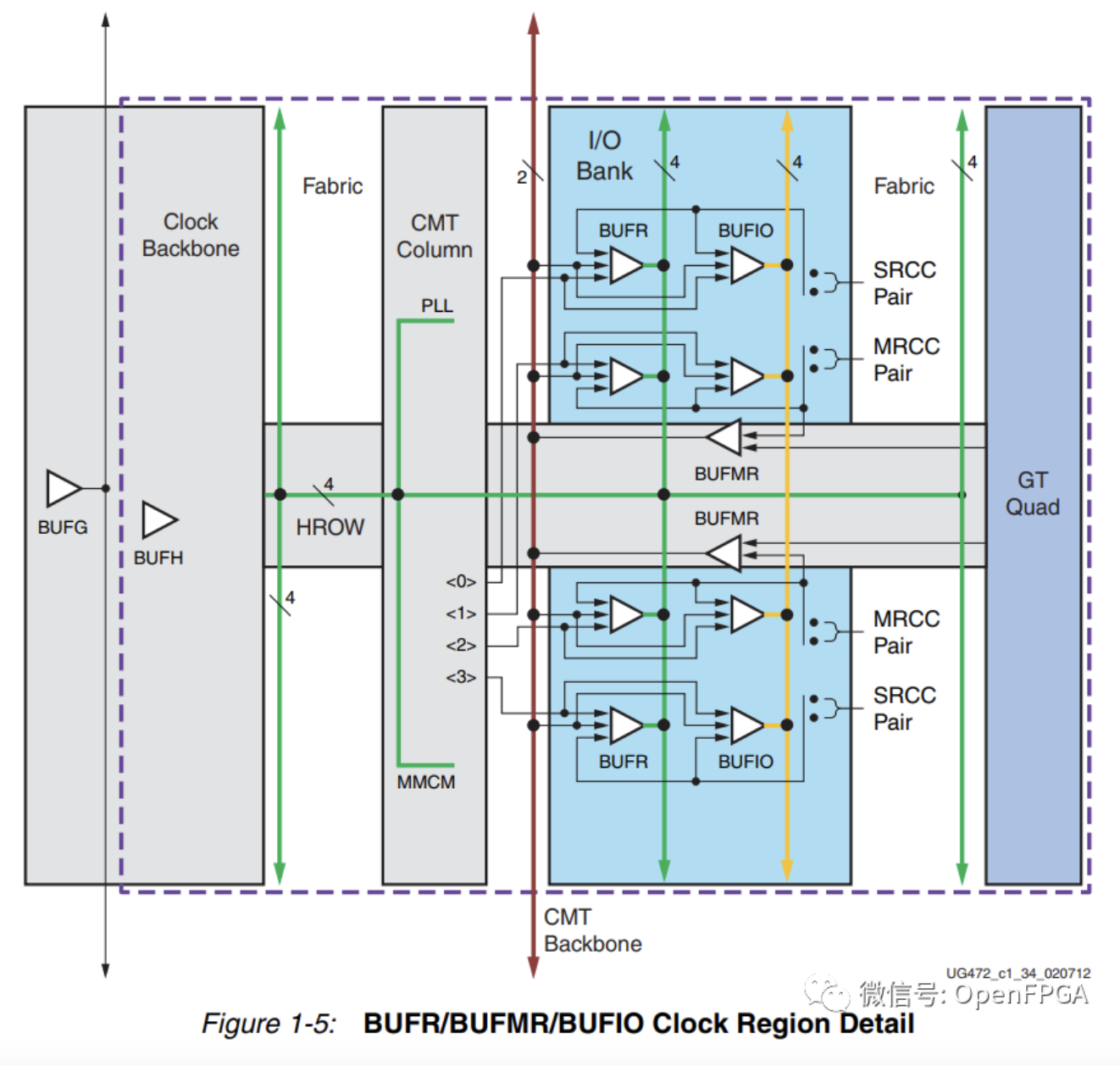

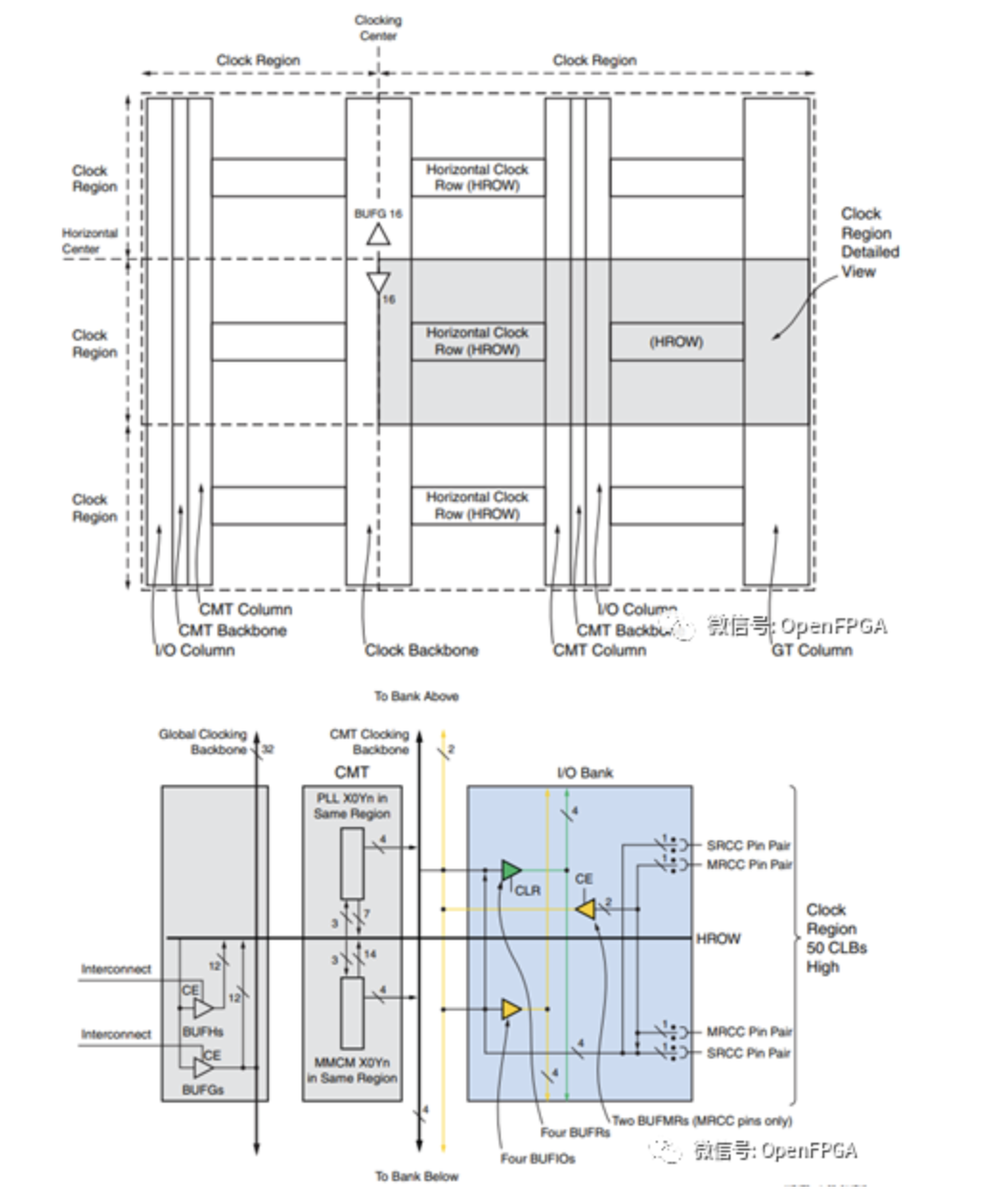

在内部,FPGA本身被分成几个时钟区域,其中包含 CLB、BRAM、DSP、GT、I/O 和其他功能。每个区域还包含多个时钟资源,包括支持以下内容的功能:

- 12个全局时钟

- 2个跨区域时钟(multi-region clocks )

- 4个区域时钟(regional clocks)

- 4 个 IO 时钟

要访问这些,我们使用以下几种缓冲区类型:BUFG、BUFR、BUFIO、BUFMR。还有一个BUFH,它是水平时钟(horizontal clock)。全局时钟包含在垂直运行的时钟主干中,水平时钟为时钟区域提供 BUFG 和 BUFH。BUFG 不必位于时钟区域内。

下面的图表可视化的展示了FPGA和区域内的时钟资源。

更多可以查看《UG472》~

我们可以通过时钟架构和对可用资源的充分了解,来确保我们的项目可以得到最佳设计,但是这会对引脚规划产生影响。有一个这样的例子是,如果我们使用 DDR 和 MIG,我们应该确保时钟输入和 CMT 在我们实现 MIG 时位于同一区域。

与所有设计一样,我们需要知道工具是如何实现设计以及使用了哪些资源。

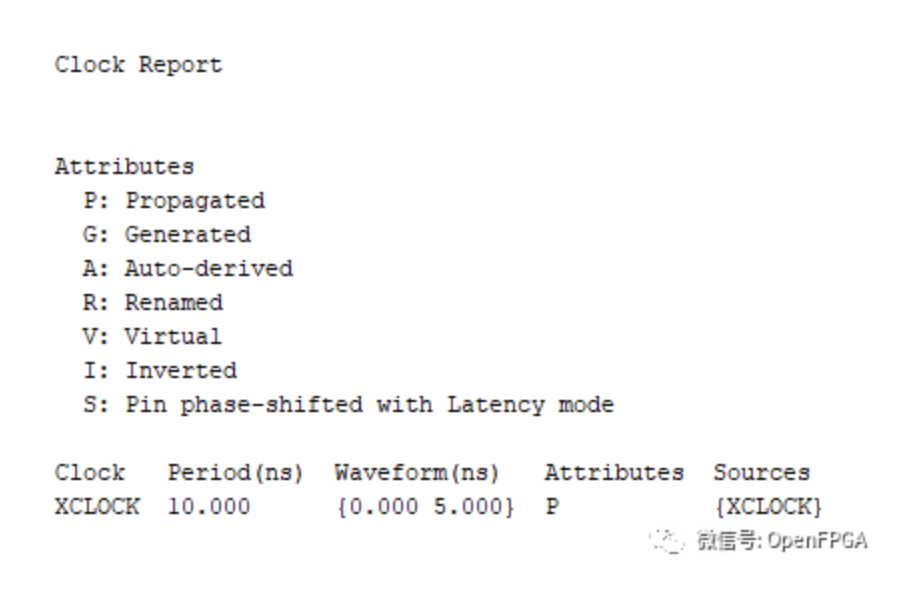

我们可以使用 Vivado 时钟报告(TCL 窗口中的report_clocks)来分析 Vivado 检测到的时钟。将会生成定义时钟。

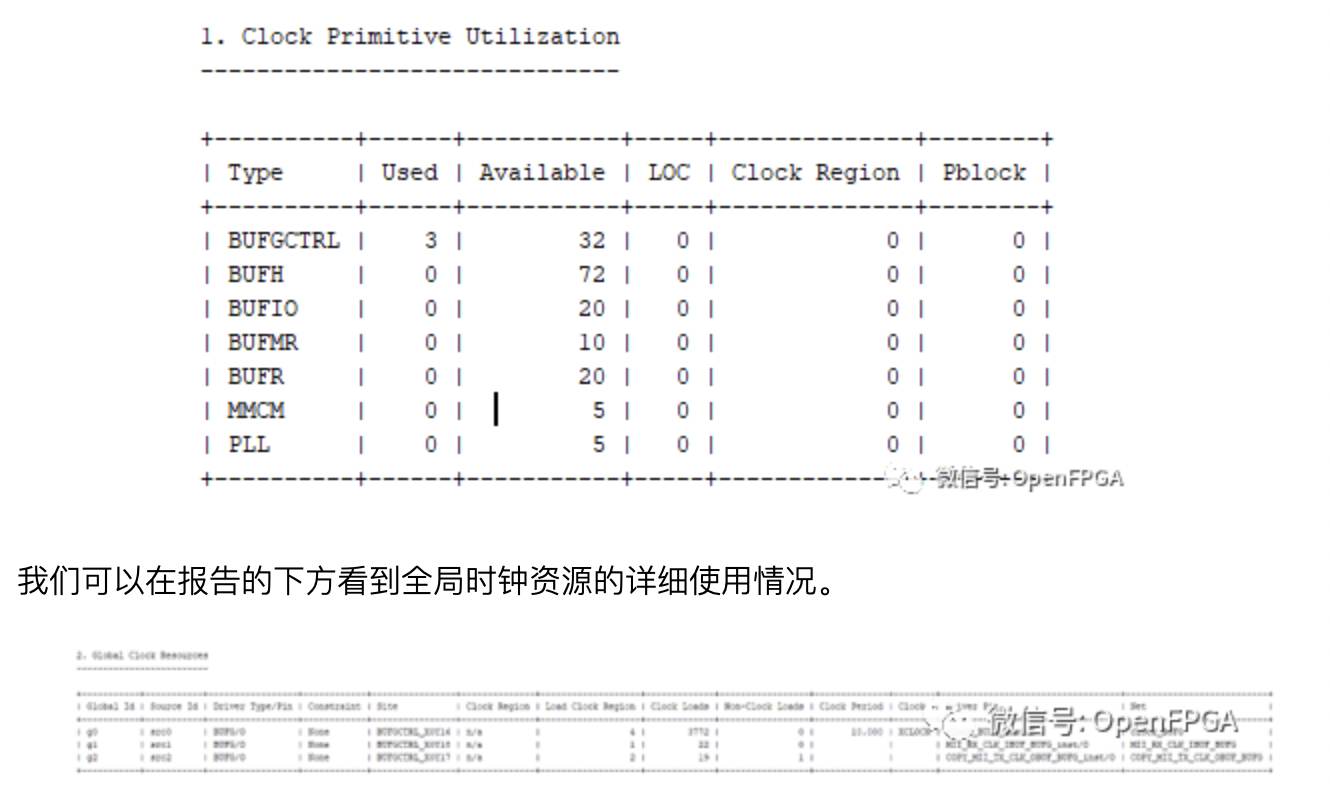

我们还可以做的一件事是运行时钟利用率报告 (report_clock_utilization),它将显示时钟分配给可用资源的情况。

在 SpaceWire 设计示例中,可以看到设计中只使用了几个 BUFG。

该报告将使我们能够确定我们是否以我们初始架构的方式植入了时钟架构。如果没有,我们需要确定目前工具实现的方式和我们设计的时钟树有什么区别,并分析哪种方式更优。

我们可以运行时钟交互报告和 CDC 报告来帮助了解时钟网络中可能出现的问题。这些报告还可用于确保我们的约束是否生效,尤其是在与设计分析报告和结果质量报告一起运行时。

关于时钟设计后续我们继续以专题方式分享,请持续关注~

原文:OpenFPGA

作者:碎碎思

相关文章推荐

- 【Verilog我思我用】-generate

- FPGA/HDL 人员开发利器-TerosHDL(开源 IDE)

- 在 Vivado 中使用 HLS 创建的IP

- 乒乓操作实例讲解-FIFO

- 使用Vitis HLS创建属于自己的IP

更多IC设计干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。