Data Types

Verilog提供了reg和wire数据类型,但是对于功能验证来说远远不够,所以SystemVerilog提供了很多更加丰富的数据类型,下面将一一介绍。

我们先来考古下,一开始Verilog中的“reg”是用来建模时序逻辑(触发器或者锁存器)的,后来对这个概念进行了扩展:

reg就是一个变量,也可以用来建模组合逻辑。

Systemverilog进一步进行了扩展,引入了logic变量,从此大一统。

另外,追随潮流。SystemVerilog还支持了面向对象的特性,以支撑功能验证环境的模块化和可重用需求。

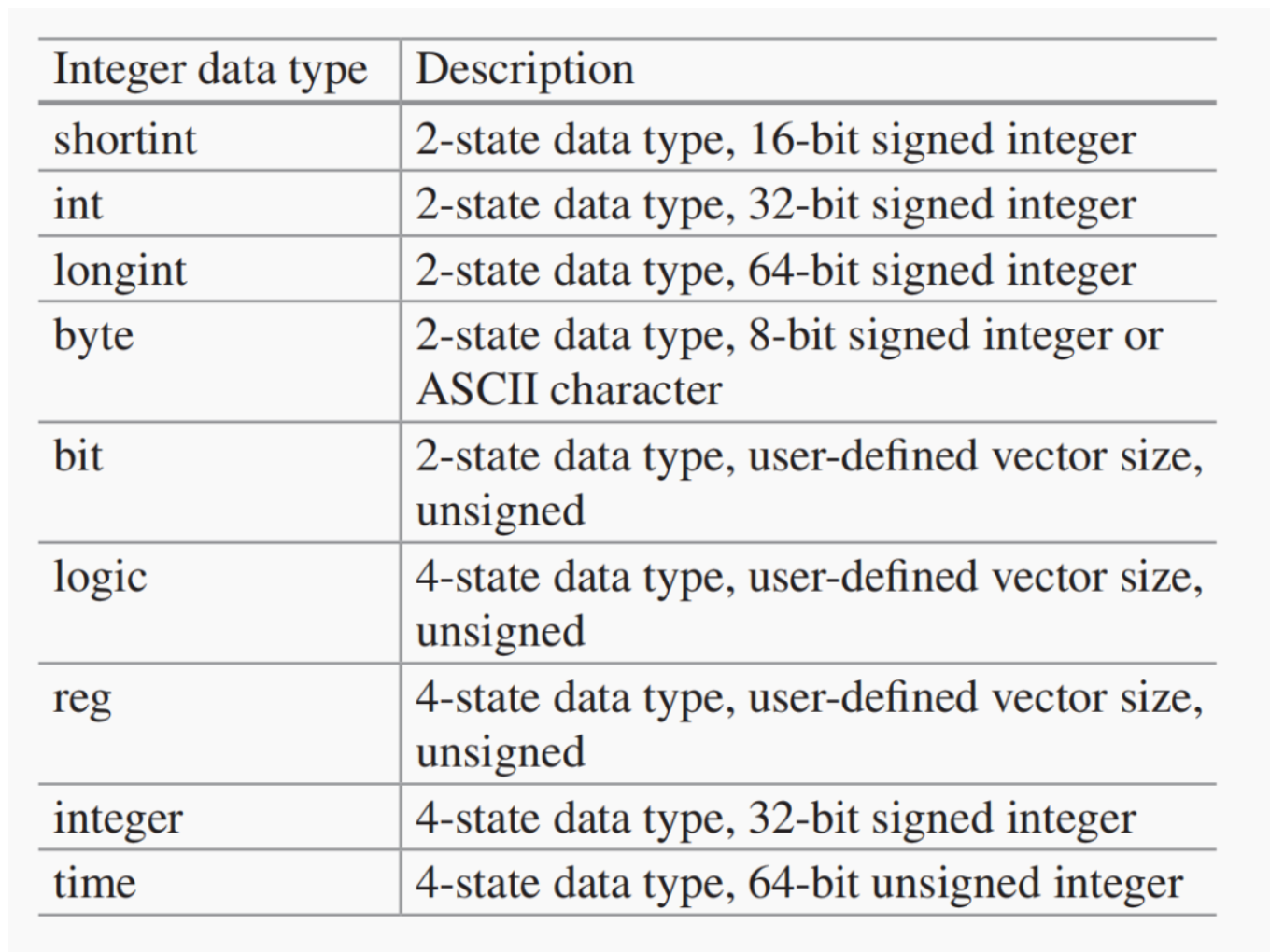

Integer Data Types

整数数据类型可以不同维度进行划分:

- 2-state vs. 4-state类型(4种状态是“0”“1”“x”和“z”;2种状态是“0”和“1”)

- signed vs. unsigned类型

Integer, int, longint, shortint, logic, byte, reg

- int、longint和shortint是2-state signed整数数据类型

- “integer”是4-state signed整数数据类型

- “reg”和“logic”是 4-state unsigned的整数数据类型

下面是一个关于整数数据类型的示例:

integer a; //4 state - 32 bit signed

int b; //2 state - 32 bit signed

shortint c; //2 state - 16 bit signed

longint d; //2 state - 64 bit signed

logic [7:0] A1; //4-state - unsigned ‘logic’

logic signed [7:0] sl1; //4-state - signed ‘logic’

byte bl1; //2-state signed ‘byte’

reg [7:0] r1; //4-state - unsigned ‘reg’

initial

begin

a = 'h xxzz_ffff; //integer - 4 state - 32 bit signed

b = -1; //int - 2 state - 32 bit signed

c = 'h fxfx; //shortint - 2 state - 16 bit signed

d = 'h ffff_xxxx_ffff_zzzz;

//longint - 2 state - 64 bit signed

A1 = -1 ; //signed assignment to unsigned 'logic’

sl1 = -1; //signed assignment to signed 'logic'

bl1 = -1; //signed byte

r1 = 8'b xzxz_0101; //'reg' - unsigned 4-state

end

initial

begin #10;

$display("a = %h b = %h c = %h d = %h", a, b, c, d);

$display("A1 = %0d sl1=%0d bl1 = %0d r1 = %b",A1,sl1,bl1,r1);

#10 $fnish(2);

end

endmodule

在本例中,

- 将a、b、c和d分别定义为integer、int、shortint和longint类型。

- 将“A1”定义为8-bit unsigned logic类型。

- 将“sl1”定义为“signed logic”类型

- 将“bl1”定义为“signed byte”类型

- 将“r1”定义为8-bit “unsigned reg ”类型

在testbench中,我们为每个变量赋值不同的数字。其中一些赋值中有“x”,以显示2-state vs. 4-state变量如何处理“x”。

我们还为一些变量赋值正负值,看看signed vs. unsigned 变量的区别:

仿真log:

a = xxzzffff

b = ffffffff

c = f0f0

d = ffff0000ffff0000

A1 = 255

sl1= -1

bl1 = -1

r1 = xzxz0101

V C S S i m u l a t i o n R e p o r t

- 赋值a='hxxzz_ffff,其中" a "是unsigned 4-state的整数类型(integer)。因此,仿真日志显示“a”保留“x”为“x”,“z”为“z”。

- 赋值b =−1,其中“b”是signed 2-state类型(int)。由于我们将“b”显示为十六进制值,因此“b”仿真log打印为“ffffffff”,相当于十进制−1。也就是说,因为b是有符号的,它的有符号赋值依然保持为有符号。

- 赋值c = ' h fxfx,其中" c "是一个2-state signed类型(shortint )。因此,仿真显式“c”的值是“f0f0”。因为“x”被转换为“0”,因为在2-state变量中没有“x”状态。

- 赋值d = ' h ffff_xxxx_ffff_zzzz,其中“d”是一个2-state signed类型(longint )。将“x”转换为“0”,将“z”转换为“0”。因此仿真显示值为“ffff0000ffff0000”。

- 赋值A1 =−1,其中“A1”是unsigned logic类型。注意,“A1”是无符号的,但是我们给它赋了一个负值。因此,它将把-1转换为255,仿真log显示A1 = 255。

- 赋值sl1 =−1,其中“sl1”是signed logic 类型。因此,“- 1”的赋值保持为“- 1”。

- 赋值bl1 =−1,其中bl1是2-state signed数据类型(byte)。因此,被赋值的负值也被保持。

- 赋值r1 = 8'b xzxz_0101,其中r1是unsigned 4-state类型“reg”。因为它是一个4-state类型,它将保留" x "和" z "。

unsigned 4-state “logic” 和unsigned 4-state “reg”是等价的,它们之间没有区别。“reg”被保留是出于历史遗留的原因。

此外,还可以显式地将有符号的数字赋值给变量。例如,1 'sb1是有符号数赋值,而1 ' b1是无符号赋值。

logic [7:0] L1 ;//unsigned logic type

L1 = 4’sb1001; //= 8’b11111001 //Sign extension

L1 = 1’sb1; //= 8’b1111_1111 //Sign extensionL1 = 8’sb1; //= 8’b0000_0001 //NO sign extension because of //explicit width being same as vector declaration

L1 = 8’sbX; //=8’bxxxx_xxxx作者:验证哥布林

来源:芯片验证工程师

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。添加极术小姐姐(微信:aijishu20)微信可申请加入IC设计交流群。