目录

14.3 链路训练与状态控制状态机(LTSSM)

14.3.1 概要

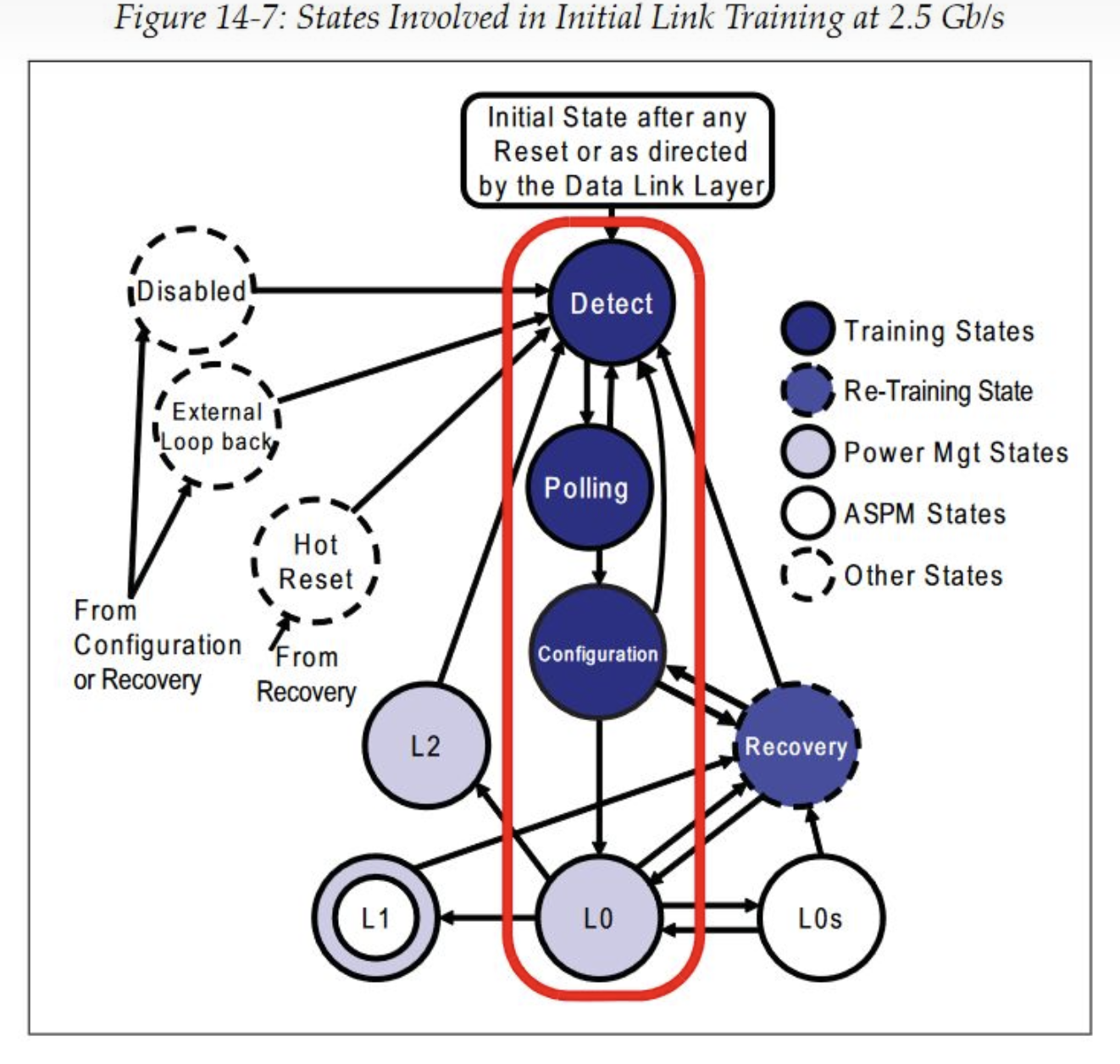

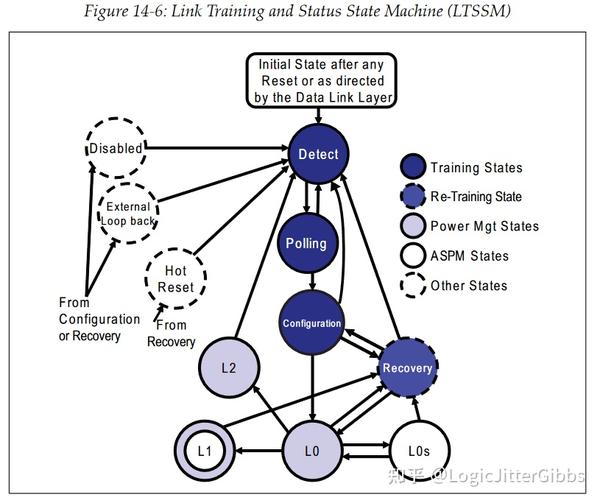

原文 519 页图 14-6 展示了 LTSSM 和链路训练的高层次抽象结构。每个 LTSSM 的状态中又划分为若干子状态。在基础复位(Fundmental Reset),即冷复位(Cold Reset)和暖复位(Warm Reset),或者热复位(Hot Reset)释放后,进入的第一个状态是 Detect 状态。

LTSSM 总共有 11 个顶层状态,(所谓的顶层状态,即与顶层状态下的子状态区分),他们分别是:

- Detect

- Polling

- Configuration

- Recovery

- L0、L0s、L1、L2

- Hot Reset

- Loopback

- Disable

他们可以划分为五大类:

- 链路训练状态

- 重训练状态,即 Recovery

- 软件驱动的电源管理状态

- 主动电源管理(ASPM,Active-State Power Management)状态(即硬件驱动的电源管理状态)

- 其他状态

在任意复位释放后,LTSSM 即进入了训练类状态(Link Training states),一切正常的话,会按照 Detect => Polling => Configuration => L0 的顺序跳转状态。待进入 L0 状态后,即可以进行正常的数据报文收发操作。

进入链路重训练状态,也即是链路恢复(Recovery) 状态的原因很多,比如从像 L1 这样的低功耗链路状态(low-power Link state)中恢复,或者正准备进行链路带宽切换(速率或者链路宽度切换)。在链路重训练状态中,链路会重复类似于训练状态的操作,来解决链路中的问题,并最终回到 L0,这一正常工作的状态。

设备中的功耗管理软件在进入低功耗设备状态(low-power device state)后,比如 D1、D2、D3Hot 或者 D3Cold 之后,会强制链路进入低功耗软件管理链路状态(low-power Management Link state),比如 L1 或者 L2 。

译注:注意区分这里的低功耗设备状态(low-power device state)与低功耗链路状态(low-power Link state)

如果链路上很长时间都没有报文需要发送,ASPM 硬件逻辑会使链路自动进入低功耗 ASPM 状态(low-power ASPM Link state),比如 L0s 或者 ASPM L1。

此外,软件可以直接使链路进入一些其他状态,比如禁用状态(Disabled),回环状态(Loopback)或者热复位(Hot Reset)状态。这里,这些状态被归纳为其他状态。

图 14-6 LTSSM 状态跳转图

14.3.2 LTSSM 状态概要(链路训练与状态状态机状态概要)

以下是对 11 个 LTSSM 状态的高层次概要介绍。

- 检测状态 Detect: 复位释放后进入的初始状态。在这个状态中,本方设备从电气特性的角度,检测链路对端设备是否存在。在穿行传输的领域中,一般无需检测对端设备是否存在,但是设置 Detect 状态的目的在于增加测试的便利性(It's done to facilitate testing),我们将在 Detect 之后的 Polling 阶段验证这一观点。除了复位释放之外,还可能从别的 LTSSM 状态进入 Detect。

- 轮询状态 Polling:在轮询状态中,发送方将以 2.5Gbps 的速率向对端发送 TS1 以及 TS2 序列,使用协议最低速率以实现对早期协议的后向兼容。接收端可以使用接收的 TS1/2 序列实现以下功能:

- 完成位锁定

- 完成符号锁定或者块锁定(Gen3)

- 如有必要,校正通道极性翻转

- 得知通道支持的链路数据速率

- 在测试条件下,发起兼容性测试序列:之所以能够进入兼容性测试模式,是因为如果一个接收方在 Detect 阶段能够被识别,但是没有返回任何流量,链路能够凭借这个现象将对端识别为一个测试负载(Test load)。在识别对端为测试负载后,发送方会发送特定的兼容测试图样(Pattern),以方便测试。这项特性能够使测试设备快速地验证链路的电压、BER(Bit Error Ratio)、时序以及其他指标在链路容忍范围之内。

- 配置状态 Configuration:上游(Upstream)和下游(Downstream)器件将分别按照他们上下游的角色,以 2.5Gbps 速率,交换 TS1 和 TS2 序列,来实现以下的目标:

- 协商决定链路的宽度

- 为各通道指派编号

- 检测通道是否需要顺序或者极性交换,在本地恢复这些交换

- 补偿各个通道之间的时序偏斜

从这个状态开始,可以关闭加扰,并可进入 Disable 或者 Loopback 状态。此外,会记录在 TS1 和 TS2 序列交换时达成共识的 N\_FTS,也就是从 L0s 状态进入 L0 状态所需的 FTS 序列数量。

- L0 状态:L0 是一个链路全功能正常运行的状态,此时链路上会进行正常的 TLP、DLLP 报文和有序集的交换。L0 状态下,链路的速率可以比 2.5GT/s 更高,但只能在进入 Recovery 状态,经历一次链路速率变化程序之后,才能切换到更高的速率。

- 恢复状态 Recovery:当链路需要重训练时,会进入 Recovery 状态,这可能是以下原因导致的:L0 状态中发生了错误、从 L1 低功耗状态中恢复到 L0 全功能正常状态、从 L0s 状态恢复到 L0 时,无法通过 FTS 序列重新完成训练。在 Recovery 状态中,会重新进行比特锁定和字符/块锁定,锁定的过程和 Polling 状态中的那次相同,但是一般来说,这次锁定的过程会更快。

- L0s 状态:L0s 是一个由硬件控制的 ASPM 低功耗状态,L0s 状态的目标是在节约一定功耗的同时,能够快速地恢复到 L0 状态。进入 L0s 的条件是,在 L0 状态下,链路其中一方发送 EIOS 序列。退出 L0s 状态时,会通过 FTS 序列重新完成比特和字符/块锁定。

- L1 状态:L1 状态能够比 L0s 状态降低更多的功耗,代价在于需要更长的时间恢复至 L0 状态(详见原文 735 页的 “Active State Power Management (ASPM)” 节 )。进入 L1 状态需要链路双方进行协商,并一起进入 L1 状态。尝试进入 L1 状态有两种方式:

- 一种情况是在 ASPM 的控制下,自动进入 L1。当上游端口没有等待调度发送的 TLP 或者 DLLP 报文时,硬件逻辑将自动与下游端口协商,一起将链路转为 L1 状态。如果下游端口同意,那么链路进入 L1 状态。否则,上游端口将单方面进入 L0s 状态(如果可以的话)。

- 另一种情况是功耗管理软件命令设备进入低功耗状态(D1,D2 或者 D3Hot),因此,上游端口通知下游端口他们必须一起进入 L1 状态,下游端口会响应该通知,链路进入 L1 状态。

- L2 状态:L2 状态是更显著的功耗节约状态,因为此时设备的主电源都将被切断。L2 中,大部分的逻辑都会因为没有电源供应而关闭,只是少部分响应唤醒事件的逻辑会依靠辅助电源 Vaux 继续工作。拥有唤醒能力的上游端口会发送低频的 Beacon 信号,下游端口能够将其转发给 RC,告知上层系统。(详情可见原文 483 页的 "Beacon Signaling" 节)通过 Beacon 信号或者边带信号 WAKE#,设备能够触发系统唤醒事件,使主电源恢复。[另外还存在有 L3 状态,不过 L3 状态和 LTSSM 就没有关系了。 L3 状态下所有电源都会被切断 ,包括主电源和辅助电源,因此 L3 状态下不会响应唤醒事件。]

- 回环状态 Loopback:回环状态定义为一种测试状态,但是协议中没有详细定义接收方的行为(比如接收方哪些逻辑会参与回环测试)。回环状态中基本的行为很简单:回环发起方(Loopback Master)发送 TS1 有序集给回环接收方(Slave),并置位 TS1 训练控制字段(Training Control)中的回环(Loopback)比特。当接收方连续接收 2 个 回环比特置起的 TS1 序列后,进入回环状态,将接收到的任何内容都重新发送给发起方。发起方会检查接收到的内容,和先前发送的内容进行比较,如果内容经过双方的 8b/10b 编码(解码)后校验一致,说明链路可以通过环路验证,完整性没有问题。

- 禁用状态 Disable:Disable 状态允许将链路配置为禁用状态,该状态下发送逻辑为电气空闲状态,接收逻辑为低阻状态。在某些情况下,比如链路状态变得不可靠,或者对端设备被意外移除,此时 Disable 是表示这些意外情况的必要状态。另外,软件也可以通过链路控制寄存器(Link Control Register)中的禁用比特(Disable bit),将设备配置为禁用状态。设备被禁用后,会连续发送 16 个链路禁用比特(Disable Link bit)置位的 TS1 序列,位于 TS1 的训练控制域(Traning Control Field),通知接收方进入禁用状态。

- 热复位状态 Hot Reset:软件可以通过置位桥控制(Bridge Control)寄存器的配置次级总线复位(Secondary Bus Reset)比特,复位链路。软件配置后,桥的下游端口会发送训练控制域(Traning Control Field)热复位(Hot Reset)比特置位的 TS1 序列。(详情可见原文 837 页的 “Hot Reset (In-band Reset)” 节)当接收方接收到两个 TS1 序列后,必须复位自身设备。

14.3.3 介绍,示例与状态/次状态

本章剩余的内容会对每个 LTSSM 状态进行介绍和讨论。基于每种状态不同的复杂度,讨论会包括一些介绍,通用的背景知识,部分状态/次状态还会有对应的示例。基于具体的需求,读者可以只浏览某个状态简介的部分,而跳过详细讨论的部分,本章的组织结构是完全支持读者这么做的。

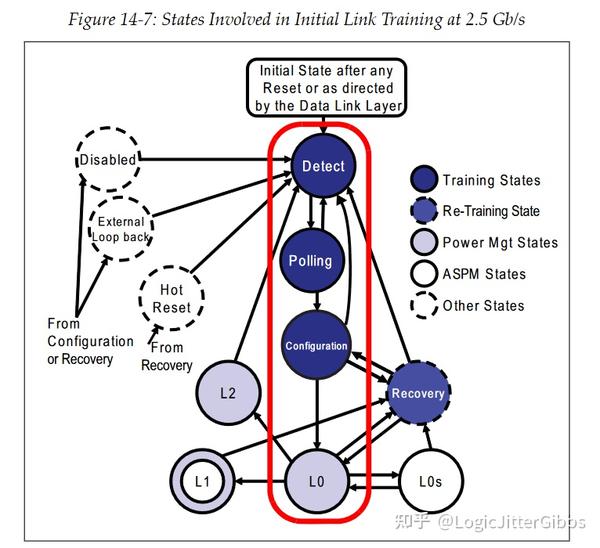

每个设备都必须以基础的 2.5GT/S 速率,进行初始链路训练。图 14-7 高亮了初始链路训练过程中涉及的状态。支持更高速率 5.0 或者 8.0 GT/s 的设备,必须进行 Recovery 状态,才能够进行速率切换。

图 14-7 2.5Gb/s 速率下,初始链路训练涉及的状态

14.4 Detect State // 检测状态

14.4.1 简介

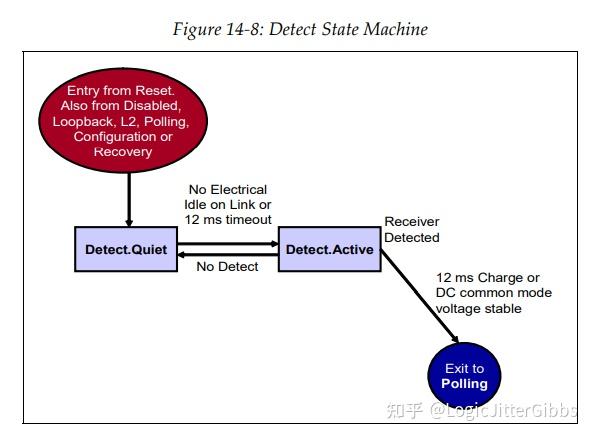

图 14-8 展示了与 Detect 状态相关的状态跳变,以及 Detect 状态的 2 个次状态。 Detect 状态下的链路行为是发送方不断检测链路对端是否有接收方存在。因为 Detect 只有 2 个次状态,所以行为比较简单,本节就直接讨论两个次状态的细节,不再讨论 Detect 状态本身了。

图 14-8 检测状态机

14.4.1 详细的 Detect 子状态讨论

14.4.1.1 Detect.Quiet

Quiet 次状态是除了功能级复位(FLR,Function Level Reset)之外所有复位,或者上电事件(Power-up)之后的初始状态。并且,协议规定必须在复位之后的 20ms 之内进入该状态。当然,也可能从其他状态进入 Detect 状态,往往是因为在这些状态中遇到了阻碍,无法正常进入下一个状态,只能进入 Quiet 次状态。(图 14-8 中描述了这些状态,他们包括:Disabled,Loopback,L2,Polling,Configuration 或者 Recovery)Quiet 次状态的属性有以下这些:

- 发送机以电气空闲(Electrical Idle)的状态启动(但是此时直流共模电压不需要在通常规定的范围内)。

- 目标数据速率为 Gen1 的 2.5GT/s。如果进入该状态时的速率不是 2.5GT/s,LTSSM 必须要在该子状态内等待 1ms,然后再将速率切换至 Gen1。

- 物理层的状态比特 LinkUp 为 0 时,向数据链路层表示链路尚未就绪。LinkUp 状态比特是一个内部信号(没有见诸标准配置空间),同样地,在链路训练完成后,LinkUp 转变为 1 ,通知数据链路层以及流控逻辑开始初始化。(详情可见原文 223 页的 “流控初始化流程”节)

- 任何先前的均衡(Eq., Equalization)状态会在置位 4 个 2-bit 链路状态寄存器后清除,他们分别是 Eq.Phase 1/2/3 Successful 以及 Eq.Complete

- 变量

- 几个变量会在 Quiet 状态清除:

- directed_speed_change = 0b

- upconfigure_capable = 0b

- equalization_done_8GT_data_rate=0b

- idle_to_rlock_transitioned=00h

- select_deemphasis 变量的处理方式取决于端口的类型

- 对于 Upstream 端口,变量的值由硬件指定

- 对于 Downstream 端口,变量的值使用链路控制寄存器中保存的 selectable Preset/Deemphasis 的值

- 由于上述的变量是在 PCIe 2.0 协议之后引入的,仅支持更早期协议的设备不存在这些值。对于这些设备来说,他们的行为相当于

- directed_speed_change = 0b

- upconfigure_capable = 0b

- idle_to_rlock_transitioned=FFh

退出状态进入 "Detect.Active"

下一个次状态是 Detect.Active, LTSSM 会在 12ms 超时或者任意一个通道退出电气空闲状态后,转入下一个次状态。

14.4.1.2 Detect.Active

Active 状态由 Quiet 状态进入。在 Active 状态中,发送机会通过将直流共模电压设置为一个合理范围内的任意电压值,接着再继续变化这个电压值,来测试各个通道上是否有接收端连接。接收端检测逻辑会观测电压变化的速率,也就电压充电的单位时间,并将其于对照值比较。这个对照值一般是没有接收端连接的情况。如果有接收端连接,那么充电的速率会大大降低,两者之间巨大的差距使检测的结果十分容易观察到。(关于这部分内容更详细的信息,可以参考接收端检测的章节:Receiver Detection,原文 460 页)。为了便于表示,下文中将本状态中检测到接收端的通道称之为:检测完成的通道(Detected lanes)。

退出状态进入 "Detect.Quiet"

如果没有任何一个通道检测到接收端存在,那么会返回 Detect.Quiet 状态。只要没有检测机,状态机会一直每隔 12ms 在这两个次状态之间进行一个循环。

退出状态进入 "Polling"

如果所有通道上都正常检测到接收端,那么会进入下一个状态:轮询。此时通道上的直流共模电压必须在 0-3.6V (V TX-CM-DC)

特殊情况

如果只有其中一些通道检测到了接收端,而有些通道没有(比如 x4 设备连接到一个 x2 设备的情况),那么将等待 12ms 再进行一次检测。如果检测的结果仍然相同,那么进入 Polling 状态,否则返回 Detect.Quiet 状态。在 Polling 状态中,对于那么没有接收端的通道,有两种可能的处理方式:

- 如果这些通道能够以独立的通道运作(见原文 541 页的 “设计支持链路聚合设备” 节),会使用另一个 LTSSM 对这些通道重复检测过程。

- 如果不存在另一个 LTSSM,那么这些通道将不会是链路的一部分,需要设置为电气空闲状态。

- *

原文: Mindshare

译者: LJGibbs文章来源:https://zhuanlan.zhihu.com/p/571868354

《PCI Express Technology 3.0》翻译系列

- PCI Express Technology 3.0 : 链路初始化与训练 1-2 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3 节(完)

- PCI Express Technology 3.0:PCIe配置概述 3.1-3.7 节

- PCI Express Technology 3.0:PCIe配置概述 3.8-3.14 节(完)

- PCI Express Technology 3.0:地址空间与事务路由4.1-4.2节

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。