你们有没有这样一个疑问,就是CPU的主频怎么做到几个GHz呢?

每一秒要给处理器几亿个脉冲,就拿11代I7处理器来说,它的基本频率就可达2.5GHz,但在我们常规的认知中,频率的大小取决于晶振的频率,比如这个晶振的频率是16MHz,那么这个芯片的工作频率就是16MHz。那就电脑CPU来说,虽然它的主频是2.5GHz,也就是2500MHz,但是也没有这么高频率的晶振。

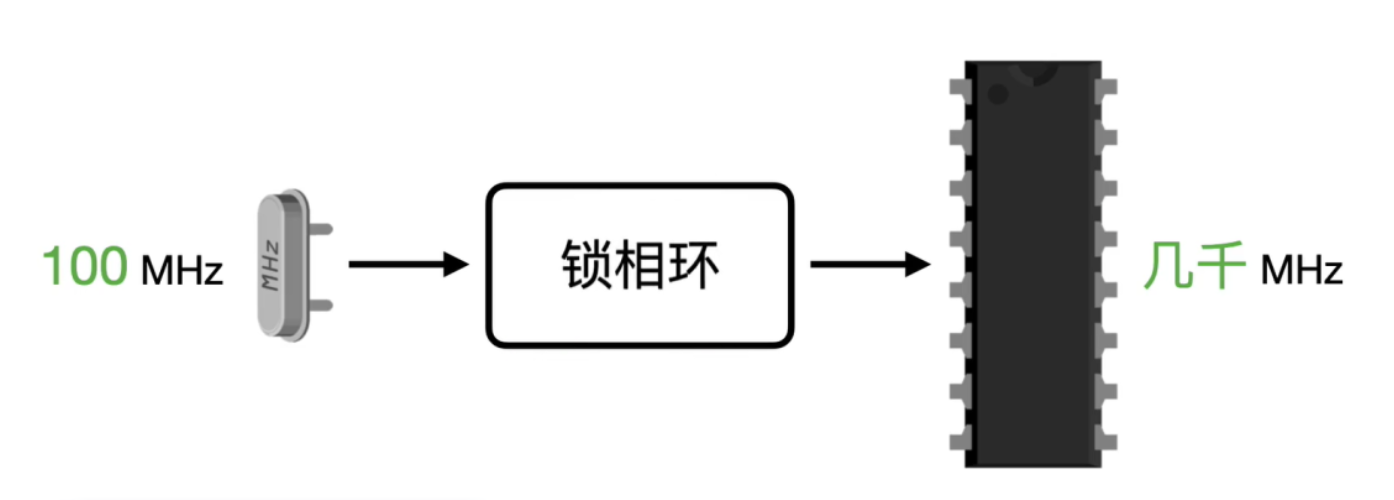

一般常用晶振的频率是4MHz、8MHz、16MHz等等,最高频的晶振也才100到200MHz。那CPU的上千兆的主频又是怎么来?

比如我们的晶振是100MHz,CPU主频却能上千兆,这就需要中间有锁相环,它能把晶振的频率进行加倍,然后再给CPU。

它的应用极其广泛,就拿我们熟知的STM32来说,它采用的晶振虽然是8MHz的,那我们可以把它的时钟设置为72MHz,它就是经过了内部的锁相环电路进行了九倍频,然后我们的时钟就从8MHz变成了72MHz。

01 锁相环到底是什么?

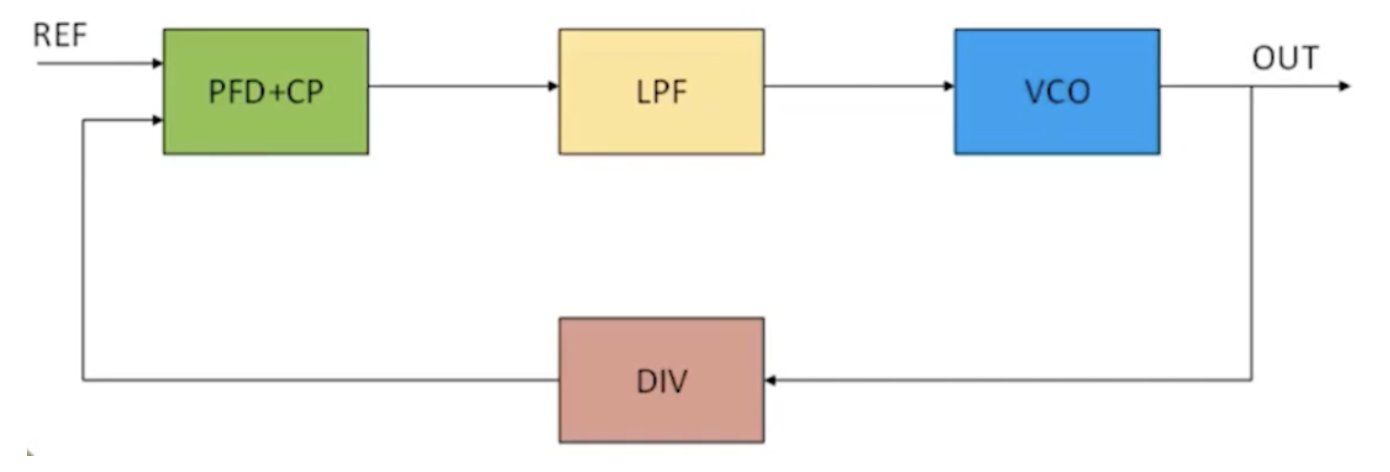

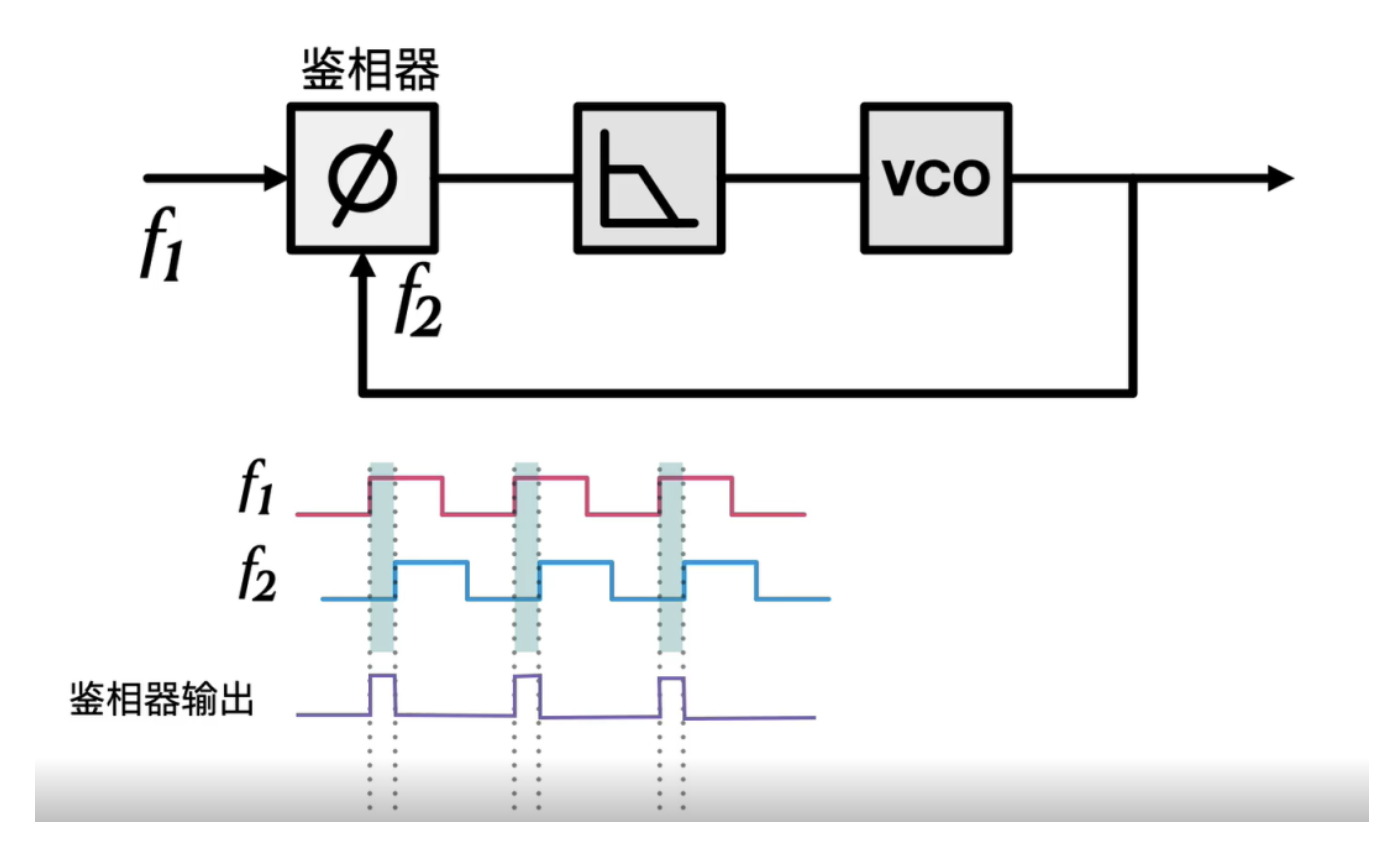

PLL(锁相环)是一个反馈控制电路,它通过反馈不断调整环路内部振荡信号的频率和相位使其跟随外部输入的参考信号。

当外部输入信号为时钟时,PLL可作为频率综合器用于产生时钟信号,也可以作为相位的滤波器过滤输入信号的相位噪声。

当外部输入信号为数据流时,PLL可作为数据时钟恢复电路用于跟踪恢复数据。

02 锁相环它是怎么进行倍频的?

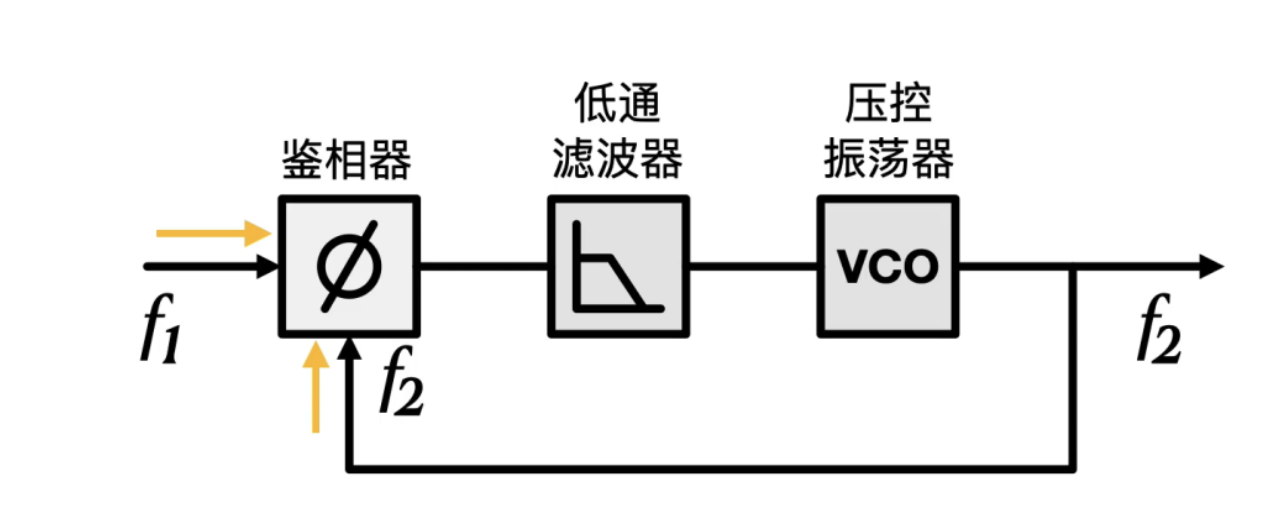

首先锁相环需要有一个参考频率,可以是温补晶振,也可以是恒温晶振,更可以是卫星授时的秒脉冲,这都是依据频率准确度来挑选的。另外有一个输出频率。参考频率为f0,输出频率为f1。然后f0与f1同时输入一个叫做鉴相器的装置中,然后将比较相位后得到的低频信号通过低通滤波器后得到一个比较平滑的电压值,作用在压控振荡器上形成输出频率,这个频率就是f1,与f0同步。但此时的f0 = f1。

如果要倍频怎么办呢?其实很简单,就是对输出的f1做N分频,分频之后的频率为f2,如果将分频器划分到压控振荡器的模块中的话就比较容易理解了,及此时的f2相当于原来的f1,即f2 = f0。那真正的压控振荡器输出的频率是多少呢?即f1 = N f2 = N f0,实现了倍频。

其实说到这里,有的人还是没有明白,这怎么就实现了倍频了呢?秘密就在于分频之后的频率f2与参考频率f0之间的相位比较。要锁相环变得稳定,就只要输入的参考频率f0与分频后的频率f2之间的相位差值为一常数,而这个相位常数会使鉴相器输出不同的电压值,经过低通滤波器(即环路滤波器)后作用在压控振荡器,使输出频率发生改变,这样就实现了倍频了。

03 锁相环升值必备的技能!

由于做锁相环对于系统的更深理解,在职业发展中也更容易晋升为项目领导者。因为学习锁相环会更多并且更容易接受到收发机,进而掌握整个系统架构。

作者:芯博士

文章来源:IC 芯博士

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。