一点关于可测性设计的理解!

1. 可测性设计背景(为什么)

任何一项技术或岗位的兴起,都对应于业内的需求。而可测性设计的出现就是为了检测到芯片量产过程中出现的带有各种制造缺陷的片子,从而为顾客提供性能更稳定的产品,降低DPPM(每百万芯片缺陷数量),从而为公司产品保证良好的口碑。

传统情况下,设计和测试过程是分开的,测试仅在设计周期末端才会考虑到。但是随着芯片集成度的日益增加和Fin-FET结构在IC设计中的使用,会导致测试成本占芯片设计整个周期测试成本的20%-30%,传统的功能性测试已渐渐无法满足芯片设计的要求。因此,现代的设计流程中,测试与设计在芯片设计早期就已经结合在一起,对应衍生了一个可测性设计流程。其中, 可控制性和可观察性是可测性设计电路的重要指标。

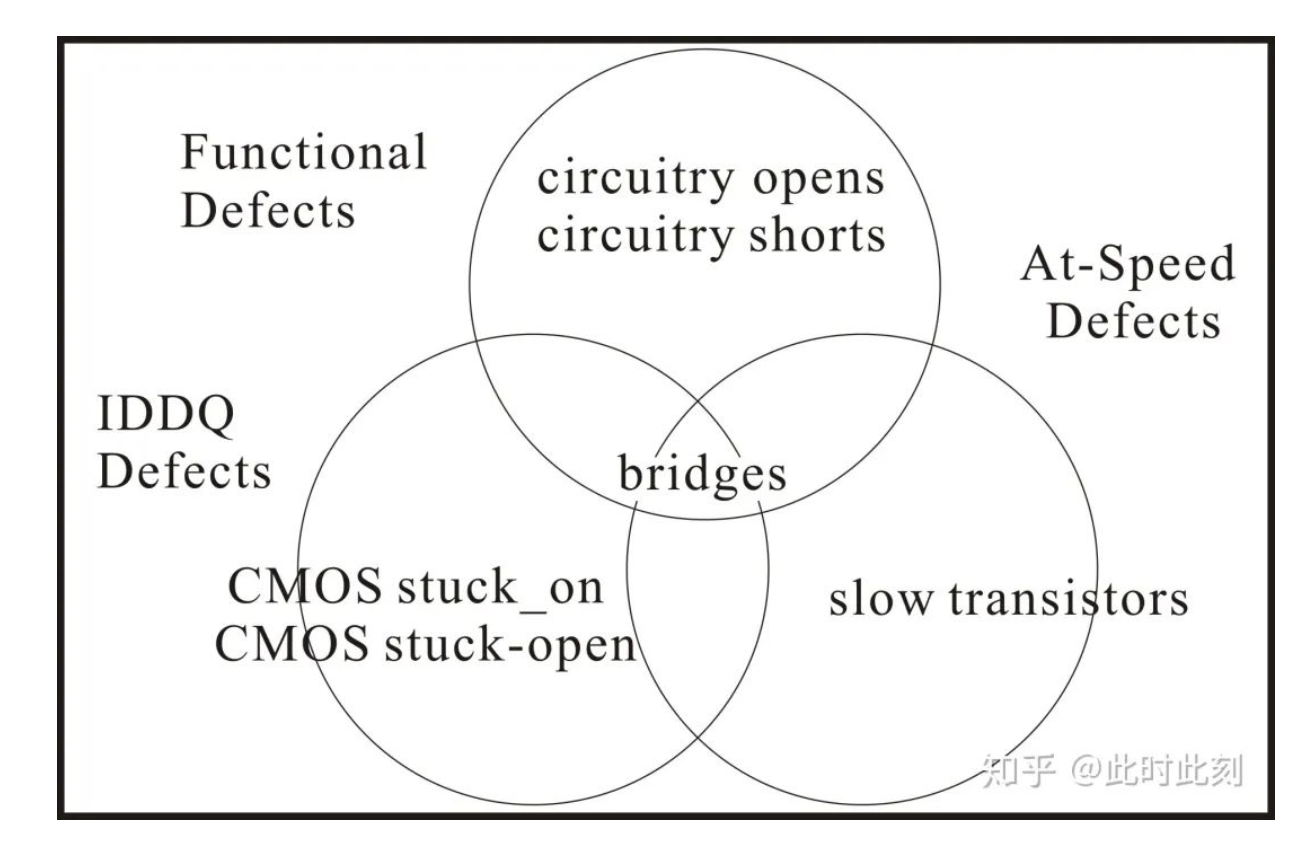

芯片设计中常见的制造缺陷

2. 可测性设计概论(是什么)

可测性设计即通过在芯片设计过程中引入测试逻辑,并利用这部分测试逻辑完成测试向量的自动生成,从而达到快速筛选量产芯片的目的。在设计中,通过在芯片初始输入端给定特定的值来测试芯片初始输出端的输出值是否与期望值相符来确定内部电路是否可以正常工作。

具体工作内容包括:

· 在芯片设计前期参与DFT架构规划

· 在RTL级别设计测试电路

· 在验证阶段验证测试电路

· 在综合阶段实现测试逻辑的插入

· 在测试阶段提供无时序问题的仿真测试向量

· 在ATE阶段协助ATE工程师调试测试向量,尽快帮助芯片Bring up,并帮助Slilcon learing及fauilure analysis。

3. 可测试设计使用范围(工作对象)

DFT可用与针对芯片上所有逻辑的测试。主要包括:

**1. 片上存储器

2. 模拟模块(如锁相环,LDO, IDV等)

3. 系统控制模块

4. 时钟控制模块

5. 电源管理模块

6. 寄存器 **

DFT基本参与了所有芯片的功能,需要提供芯片初始化时FUSE的管理;需要设计协调时钟,复位,电源等控制逻辑确保测试功能的实现,同时不影响芯片正常的工作模式。对于片上存储器,由于其分布的复杂性,需要统筹设计MBIST的分布,以最小的代价实现测试覆盖率。除此之外,芯片中功能模块的每一个寄存器都是扫描链测试的工作对象。任何一个寄存器,或者寄存器之间的组合逻辑发生故障,都可被DFT检测方法侦测到。

4. 可测性方法(怎么做)

Ad Hoc DFT:

该方法在不对设计风格做出主要改变的情况下,使用好的设计来改善一个设计的可测性,常见方法有:

**· 最小化冗余逻辑

· 最小化异步逻辑

· 从逻辑电路中隔离时钟

· 增加内部的控制点和观察点**

在整个设计过程中使用这些实践方法可以提高设计的整体可测性。但是,使用基于Mentor Graphics的结构化DFT技术工具可以对设计的可测性产生更大的改善。

Structured:

结构性测试提供了一种更加系统化和自动化的方法来改善设计的可测性,其目标在于增强电路的可控制性和可观测性。常用方法如下:

· 扫描设计技术

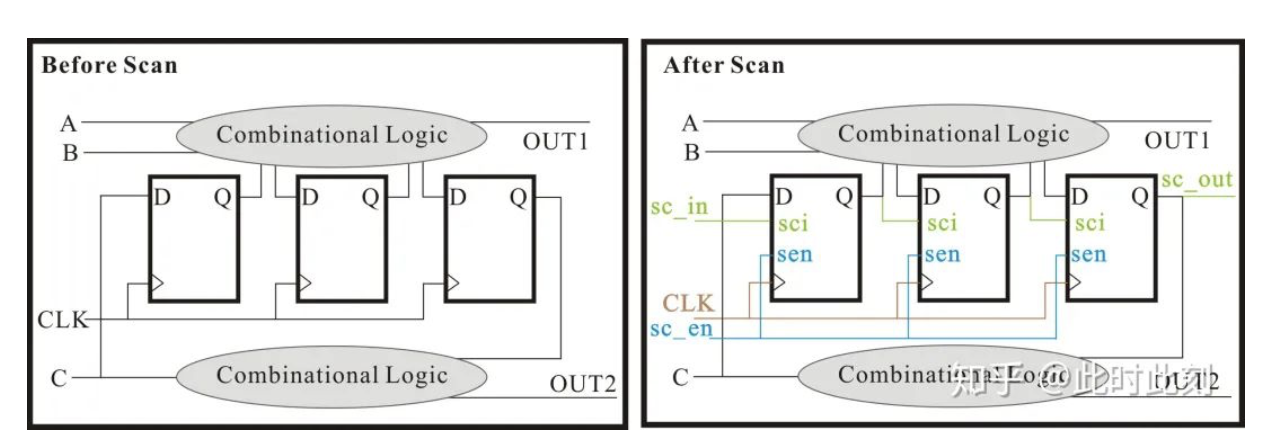

扫描单元的替换和连接

通过用一个可扫描的等效物替换设计中所有的存储器元件,然后把这些扫描单元连接为扫描链,利用多个时钟脉冲将特定的输入值一拍一拍打入到扫描链上所有的时序触发器,同时在扫描输出端通过多个时钟脉冲得到这些触发器的测试响应。将得到测测试响应值与工具给定的期望响应值对比可以帮助快速找到发生缺陷的位置,实现对量产芯片的筛选。这一方法通过控制和观察设计中所有存储元件的值,从而使得时序电路的测试向量生成和仿真变得和组合逻辑一样简单。

· 内建自测试方法

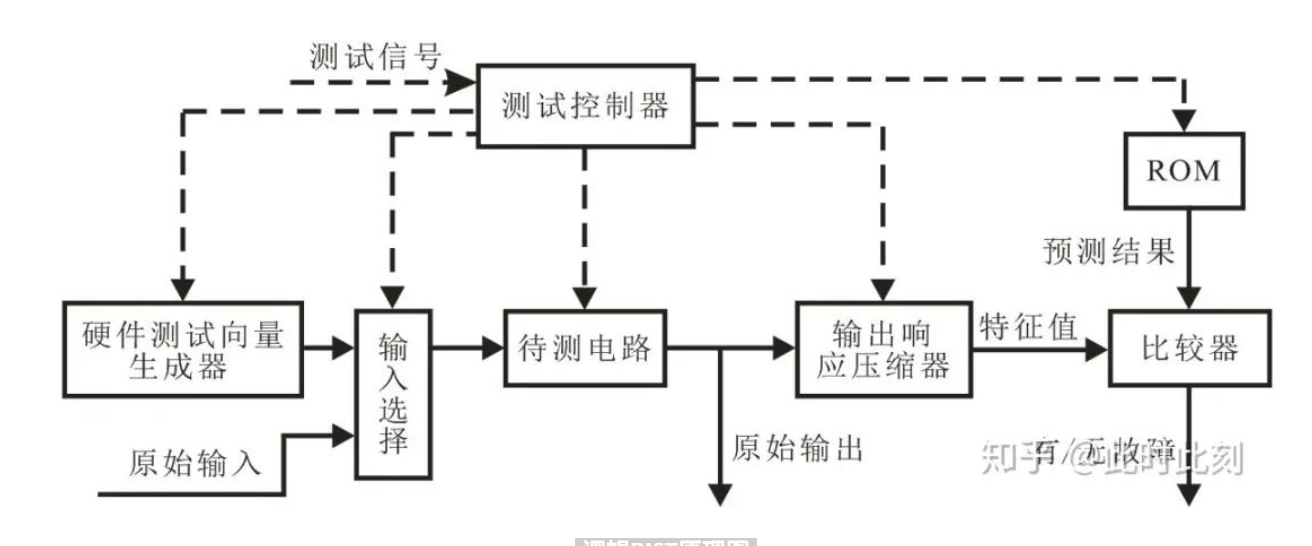

逻辑BIST原理图

近年来,芯片工作频率越来越高,ATE测试机台速度渐渐无法满足芯片测试的要求,高速测试变得越来越困难。BIST测试主要通过在电路内部插入逻辑电路,使电路自己生产测试向量来对电路进行测试,虽然会导致芯片面积增加,但相较于不增加测试电路带来的测试时间和成本还是具有很大的优势,因此成为一种备受关注的测试方式。

· 边界扫描技术

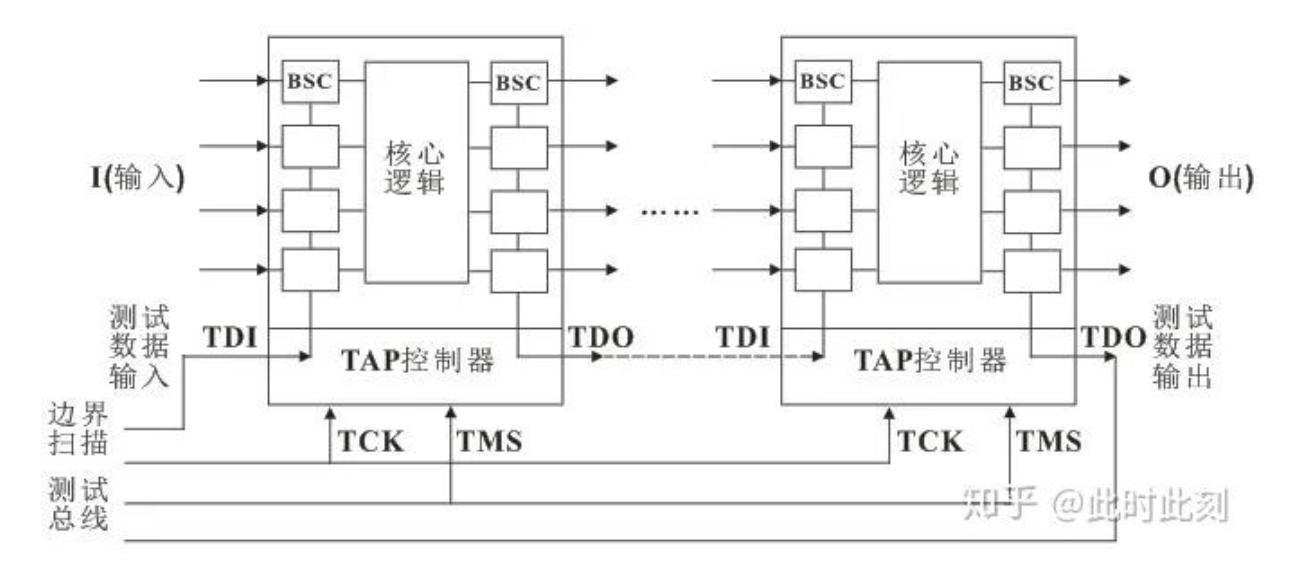

边界扫描原理图

上图给出了多个器件相连接的JTAG测试:系统的测试总线TCK和TMS共享给电路中所有需要测试的器件,这些信号由TAP控制器统一控制,第一个器件的输入端作为整个测试的整体输入端,前级器件的输出作为后级器件的输入,最后一个器件的输出端作为整个测试的整体输出端,通过这种方式将所有待测器件的引脚连接起来,测试者可以通过给定输入端特定的输入值并为各输出端设定对应的期望值,通过比较输出端实际测到的值是否与期望值相符来确定电路是否存在缺陷,达到测试芯片的目的。

5. 可测性设计故障模型

为了检测到芯片电路中的故障,1959年Eldred提出了故障模型的概念,即一个试着捕获物理缺陷对电路行为的逻辑功能的影响的结构模型。从那之后,固定型故障模型被用来生成高效的测试向量集,常用的故障模型分为以下几类:

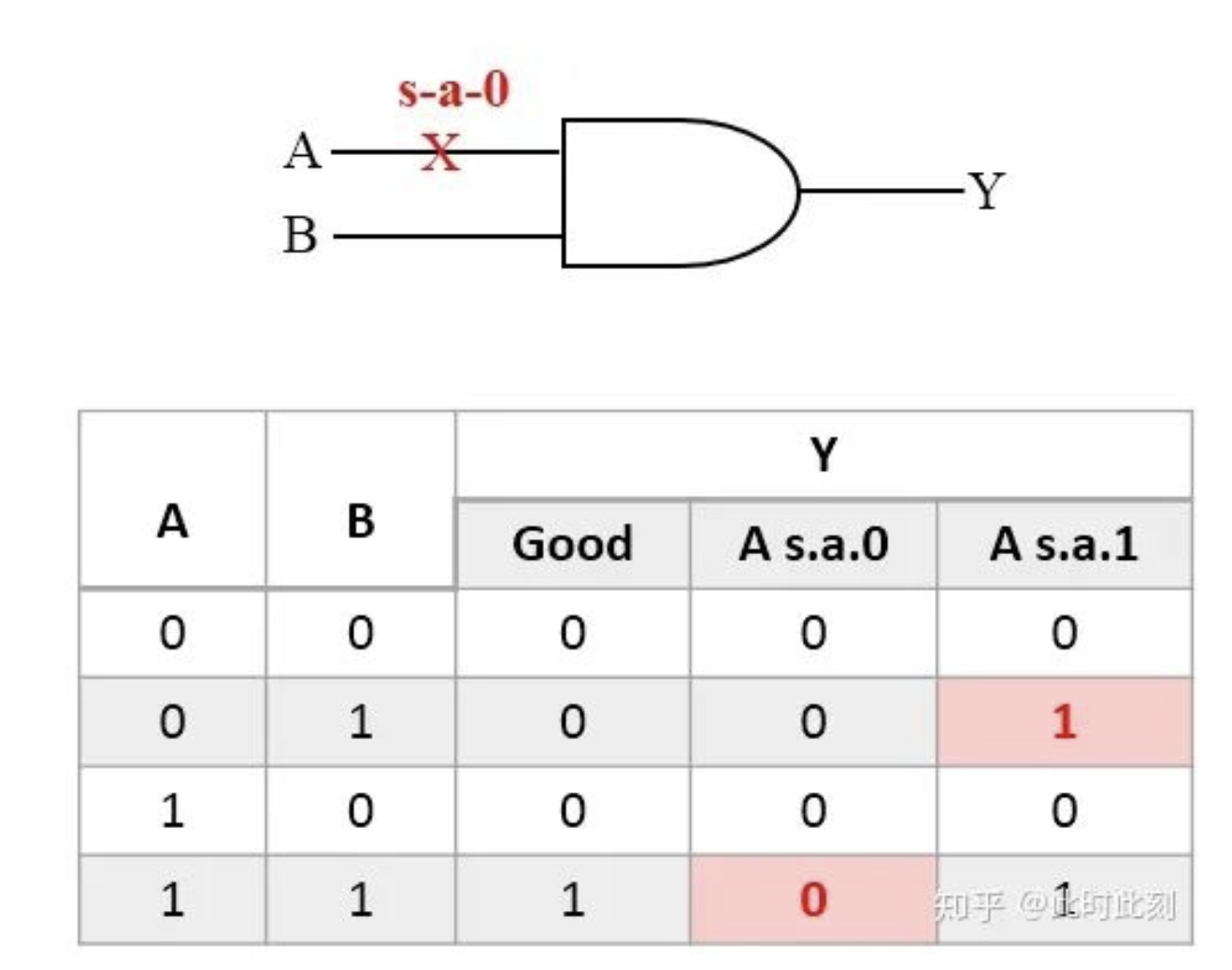

· 单固定型故障模型

单固定型(single stuck-at)故障模型原理图

功能性测试常常使用单固定型故障模型,由于其在定位很多常见缺陷类型中表现出的高效性,它也是故障仿真中最常见的故障模型。当电路中某个门或终端处于高(固定到1)或低(固定到0)电平时,该模型会为它进行建模。该故障模型的故障点包括初始例化单元的引脚。上图以二输入与门的A输入端口为例,当A端口短接到地时,其值为0,为了测试到A端口处的故障,我们需要给A端口设一个相反的值1,为了使A的输入传到Y端口,B端口的输入端值应设为1,那么如果A端口无故障,Y端口值应为1,如果A端口处有故障,Y端口处值应为0。因此当A=1,B=1,Y=0可以作为一组测试向量检测A处是否有固定到0的故障。这组向量也可以检测B处固定到0的故障。同理,我们可以推断出检测A处固定到1的故障的测试向量为:A=0, B=1.Y=1。为了降低测试的复杂性,实际测试中,最常使用的是单固定型故障模型,即假设一个电路同一时刻只有一处有故障。

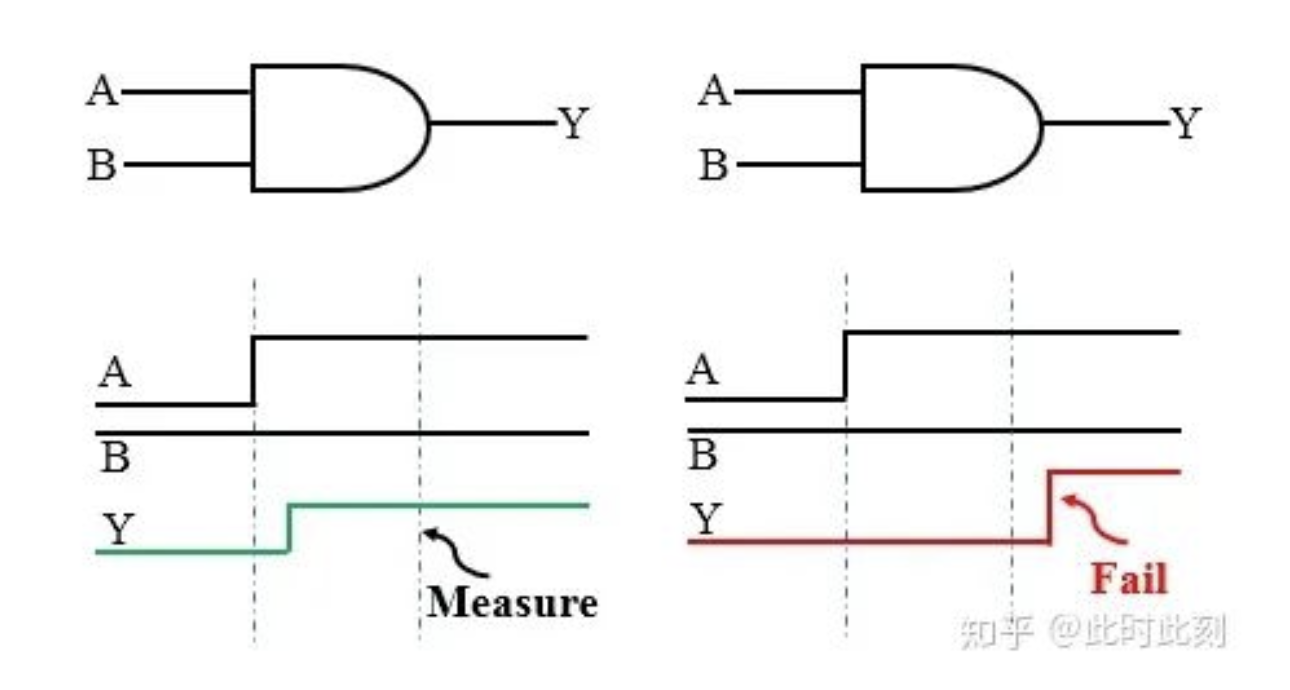

· 传输故障模型

传输(transition delay)故障模型原理图

传输故障分为两种情况:缓慢上升节点(Slow-to-rise node)和缓慢下降节点(Slow-to-fall node)。缓慢上升是指信号从低电平变为高电平所需的时间超过了给定的时间造成了电路功能的实效。缓慢下降同理。转移故障模型通常应用于高速测试中,主要测试电路的总延时。它主要检测部分导通晶体管和互连线上的缺陷它的使用包括两个周期,发射周期和捕获周期。上图以一个简单的与门为例,描述了转移故障模型的原理,为了检测端口A是否存在转移故障模型,可先把端口B设为高电平,然后在两个周期交接处把端口A处电平由0变为1,随后在下一个周期处观测二输入与门输出端Y的电平值,如果此时Y=1.说明A处无缺陷,反之,如果此时Y=0,说明A处存在缺陷。该图以简单的例子说明了传输故障的作用原理。

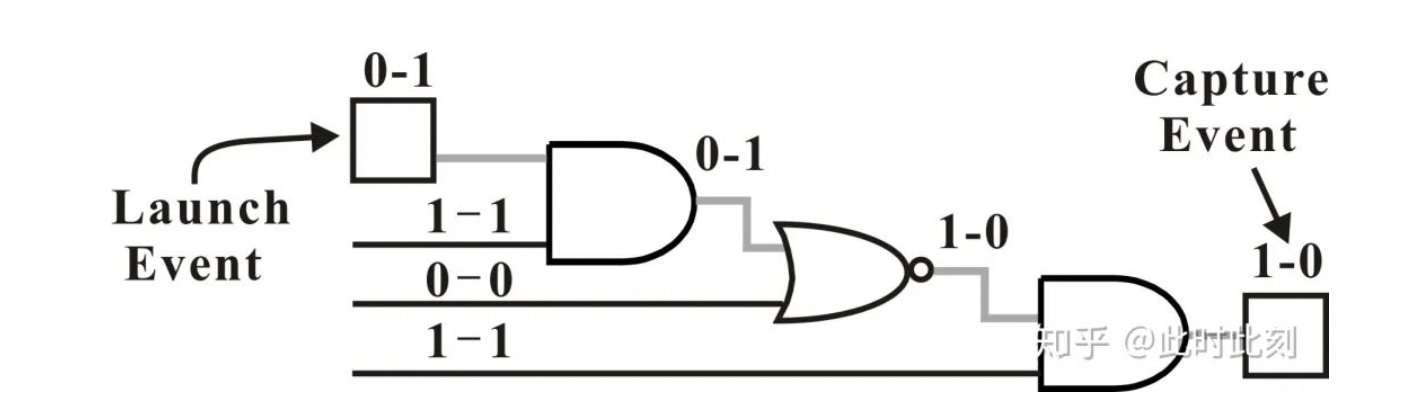

· 路径延时故障模型

路径延时(path delay)故障模型原理

路径延时故障模型针对电路路径上的缺陷进行建模。不像其他的故障类型,路径延时缺陷没有本地化的故障点,相反,他们与测试通过特定路径(通常为关键路径)的所有门的组合延迟有关。路径拓扑和边缘类型可识别路径延迟故障,路径拓扑描述用户指定的路径从开始(发射点),通过组合路径到结束(捕获点),发射点要么是主输入,要么是状态元素。捕获点要么是主输出,要么是状态元素。用于发射或捕获点的状态元素要么是扫描元素,要么是符合时钟顺序处理条件的非扫描元素。路径定义文件定义要生成模式的路径。

该模型分为两类:缓慢上升路径和缓慢下降路径。以下图为例,首先定义一条路径,随后将某个输入端的数字由0变为1,其他输入为它让路,保证它的变化能够传到这条路径的输出端。输入端从0到1的变化称为launch,输出端由1到0的变化称为capture。

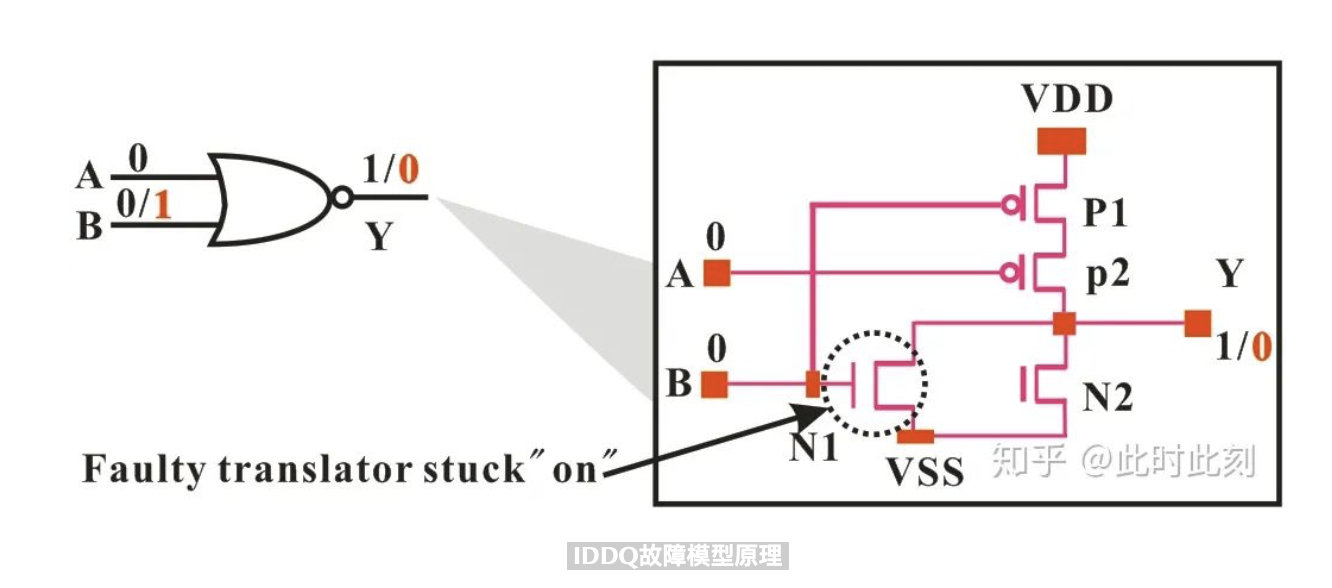

· IDDQ故障模型

IDDQ故障模型原理

IDDQ测试用来测量通过电路器件的电流。IDDQ测试测量的是静态电源电流而不是引脚电压,通过功能性测试不容易检测到器件的缺陷如CMOS晶体管的固定开路缺陷或相邻桥接缺陷。IDDQ测试设备会施加一组测试向量到设计中,让电流稳定下来,然后测量过大的电流。产生过大电流的器件可能存在内部制造缺陷。IDDQ测试可以覆盖到很多桥接缺陷和开路缺陷,但电路测试置入速度较慢,电流阈值往往由经验所得。此外该故障模型还会在电路中引入模拟参数即通过/失败电流阈值,这一参数会使得区分好坏器件变得困难。静态电路故障模型测量电路稳定状态下,电源电流的值。这种故障模型比较花时间,但通常也可以达到80-90%的测试覆盖率。主要检测CMOS晶体管卡在一些固定开路情况下的缺陷,此外还有桥接缺陷和部分导通晶体管缺陷。

此外还有桥接(Bridge)故障模型,CMOS Stuck-open等多种故障模型。

6. 使用工具

针对可测性的需求,Synopsys公司和Mentor公司各自开发了对应的工具来完成相关的可测性工作,利用工具可使得可测性设计工作更加高效和自动化。

· Synopsys:

通过TetraMAX工具实现扫描链的插入,压缩以及各种对应的功能。

· Mentor:

开发了一整套Tessent工具用于实现扫描和ATPG(自动测试向量生成)。

其中各个需要实现的功能都称为是Tessent的一个feature。

包括测试向量的插入,扫描链压缩,测试向量生成,仿真都是基于Tessent工具实现。

仿真debug利用Verdi和Mentor公司的 VI工具进行debug。

7. 小结

本文针对DFT做了一个简单的综述,简单介绍了DFT产生的原因背景、作用原理、工作对象、作用方式、故障模型等。本文大部分内容摘自本人硕士毕业论文,少部分取自微信公众号DFT精英,希望能给需要的人做一些简单的普及,有时间会继续更新。

作者:此时此刻

文章来源:知乎

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向