来源:EETOP编译自semiwiki

作为首屈一指的高速通信和系统设计会议,DesignCon 2023提供了来自各种专家对一些技术主题的深刻见解。在高速通信领域,多年来,PCIe在支持越来越高的通信速度方面发挥了至关重要的作用,每一次新的修订都是如此。6.0修订版是该通信接口标准的最新修订版,使系统设计者能够在数据中心部署人工智能推理引擎和协处理器方面取得进步。因此,PCIe 6.0是会议上的一个热门话题,不仅是为了64GT/s的速度,也是为了了解可靠地提供这一速度的工程挑战。

PCIe 6.0给工程师带来了一系列苛刻的芯片和系统设计挑战。为了可靠地提供PCIe 6.0的全部优势,需要协同合作,以规范PCIe卡、电缆、连接器组装、测试方法、测量和工具以及PCIe PHY和控制器IP等领域的规范。讨论这些话题的专家小组包括泰克公司的David Bouse、是德科技(Keysight)的Rick Eads、Samtec的Steve Krooswyk、Synopsys的Madhumita Sanyal和Intel的Timothy Wig。小组会议由是德科技的 Pegah Alavi主持。

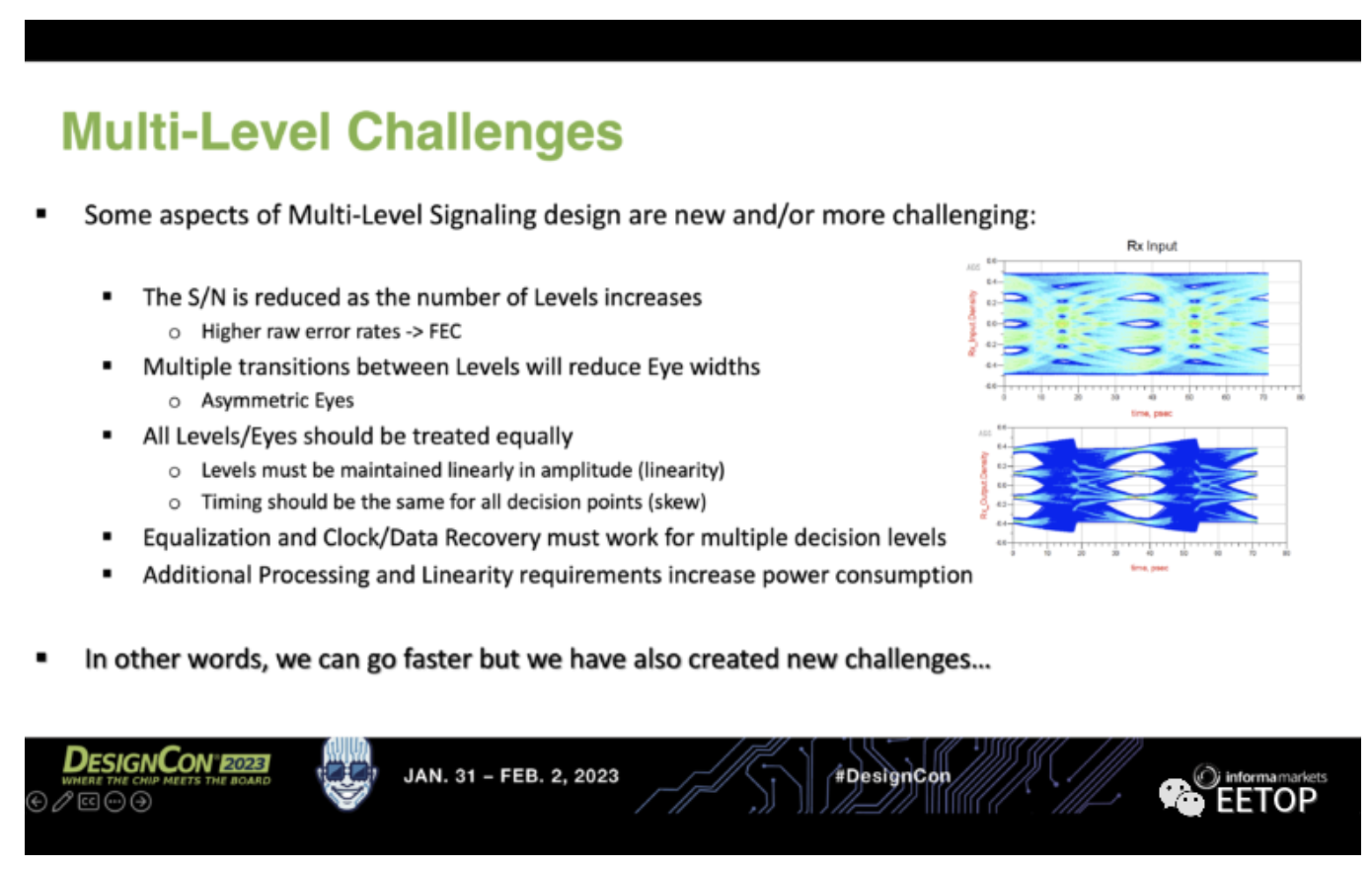

Pegah 在会议开始时强调了多级信令 (MLS) 在从 NRZ 切换到 PAM4 信令以支持 64GT/s 时带来的挑战MLS的采用为继续提高数据通信速度开辟了道路。通过将1个以上的比特映射到一个传输符号中,可以减少所需的带宽/位。但是MLS也带来了许多挑战,需要克服这些挑战才能可靠地实现速度优势。

在MLS下,信噪比会恶化,从而对通道的性能产生负面影响。因此,通道的各个方面都需要密切关注。以提供可靠的 PCIe 6.0 最终用户解决方案。以下是本届会议要点的综述。

PCIe卡和电缆外形尺寸的更新

PCIe卡机电(CEM)外形规格的Rev 6.0将于2023年完成。

CEM卡的物理外形尺寸引入了两个新的电源连接器,电压为48V,可提供600W。

引入了屏蔽平面 /south via的方法,以屏蔽发送信号与接收信号。如果没有屏蔽平面/ /south via,PCIe 6.0通道将会被完全破坏,因为已知的例子是不注意卡的布局甚至破坏了PCIe 5.0通道。

正在定义两种 PCIe 电缆外形规格。这两种新外形都不同于以前的 PCIe 电缆解决方案。内部电缆外形正在基于 EDSFF-TA-1016 电缆系统定义,目标是 PCIe 5.0 和 PCIe 6.0 速度。外部电缆外形尺寸正在根据行业标准 CDFP 进行定义。内置 PCIe 电缆外形尺寸已针对来自多个供应商、安装样式和长度的一系列连接器和电缆进行了表征。

测试方法和工具

PCIe生态系统在为PCIe 6.0定义和开发工具和测试方法时,一直在考虑后续的PCIe 7.0。毕竟,PCIe 7.0规范(128 GT/s)指日可待,它有望在2024-2025年的时间框架内到来。在开发仿真、测试和测量方法以验证连接器和电缆-连接器组件时,要牢记Tx、Rx和通道合规性要求。在PCIe 6.0中引入了前向纠错(FEC),这是PCIe接口标准的第一次引入,以适应通道损耗的影响。

PCIe v6.0 重定时器

上面介绍的所有内容可确保卡、电缆、连接器和组件经过验证以支持 PCIe 6.0。根据终端市场和应用,基于 PCIe 的系统将利用上面列出的硬件部署不同的通道拓扑。因此,每个通道拓扑都会带来其自身的特性,这些特性会影响通道性能。

下图显示了基于 PCIe 的系统中常见的四种不同通道拓扑。

从 PCIe PHY 的角度来看,它需要能够针对所有可能的通道拓扑进行优化。鉴于 PCIe 6.0 规范规定的减少插入损耗预算,如何确保来自根端口的信号到达目标端口而不会失去保真度。

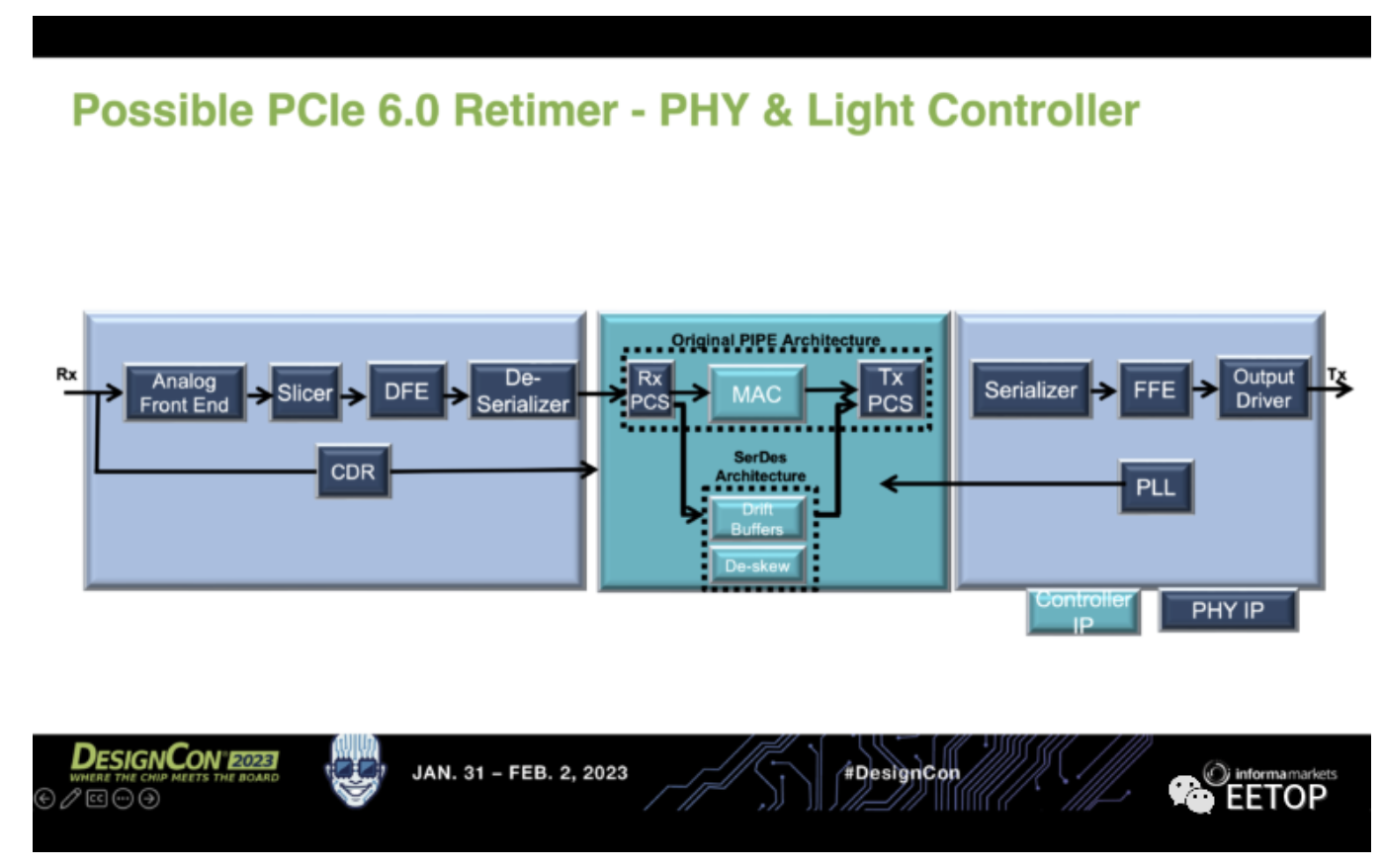

解决方案是引入 PCIe 6.0 重定时器电路。PCIe重定时器使PCIe在系统板、背板、电缆、立管和附加卡上的扩展成为可能,无论其部署的通道拓扑如何。重定时器是一个物理层和协议感知的设备,但对软件是透明的,可以驻留在PCIe根端口和端点之间通道的任何地方。它通过任何通道从主机PCIe根端口完全恢复数据,提取时钟并通过另一个通道将干净的数据重新传输到PCIe端点设备。重定时器解决方案是以定制的PHY和MAC的轻型控制器逻辑的形式实现的。

文章来源:EETOP

推荐阅读

- Wi-R 一种全新的通信方式,让你的身体充当媒介!芯片已推出!

- 科普:DDR

- 用于探测中微子的超低温(液氩)ADC设计

- 在IC设计/验证中怎么应用ChatGPT?

- IC各细分领域公司简介以及薪资调研(CPU篇)

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。