在Arm architecture里,经常提到Context synchronization event(CSE)和Explicit synchronization,Context synchronization events在之前是叫作context synchronization operations。Explicit synchronization是Context synchronization event的结果,也就是CSE发生时,会伴随着Explicit synchronization。从概念上将,Explicit synchronization发生在每个CSE event的第一步,因此,如果CSE event使用之前已更改但在CSE event发生时尚未同步的状态,则保证CSE event使用已同步的状态。另外,任何导致写system registers的system instructions都必须同步,然后才能保证写的结果对该system register的后续direct read可见。

CSE的触发来源有:

One of:

- Performing an ISB operation. An ISB operation is performed when an ISB instruction is executed and does not fail its condition code check.

- Exception entry, if FEAT_ExS is not implemented or the exception is taken to AArch32 or if FEAT_ExS is implemented and the appropriate SCTLR_ELx.EIS bit is set.

- Return from an exception, if FEAT_ExS is not implemented, or the exception is returning from AArch32 or if FEAT_ExS is implemented and the appropriate SCTLR_ELx.EOS bit is set.

- Exit from Debug state.

- Executing a DCPS instruction in Debug state.

- Executing a DRPS instruction in Debug state.

以上这些源头中,4,5,6这三个和debug state相关的。ISB和exception entry events可用于Debug state和Non-debug state。

Context synchronization event的影响有:

重点的几点保证:

- 在CSE之前pending的unmasked interrupt和halting debug event是要先于ISB之后指令做完;

- 在CSE之前的所有direct或indirect写system registers会影响任何在CSE之后的instruction,包括direct read;

- 在CSE之前的所有已完成对TLB/Instruction caches/branch predictor的invalidation操作对CSE之后的指令要可见;

- 在CSE之后的所有指令都不能执行任何功能,要等到CSE完成后才行;

- Arm architecture要求产生CSE的instructions不应该是投机执行的,除非允许performance monitors counter证明这种投机。

现在我们来分析下Instruction Synchronization Barrier(ISB)指令。在Arm architecture是这么定义的:“Instruction Synchronization Barrier flushes the pipeline in the PE and is a context synchronization event.”。从这句话可以看出ISB两个作用:1.flush执行该ISB指令PE的pipeline的指令,也包括core内可能存在的instruction queue/buffer。2.产生1个CSE事件。因此结合最开始分析的CSE,可以得出执行ISB指令后:

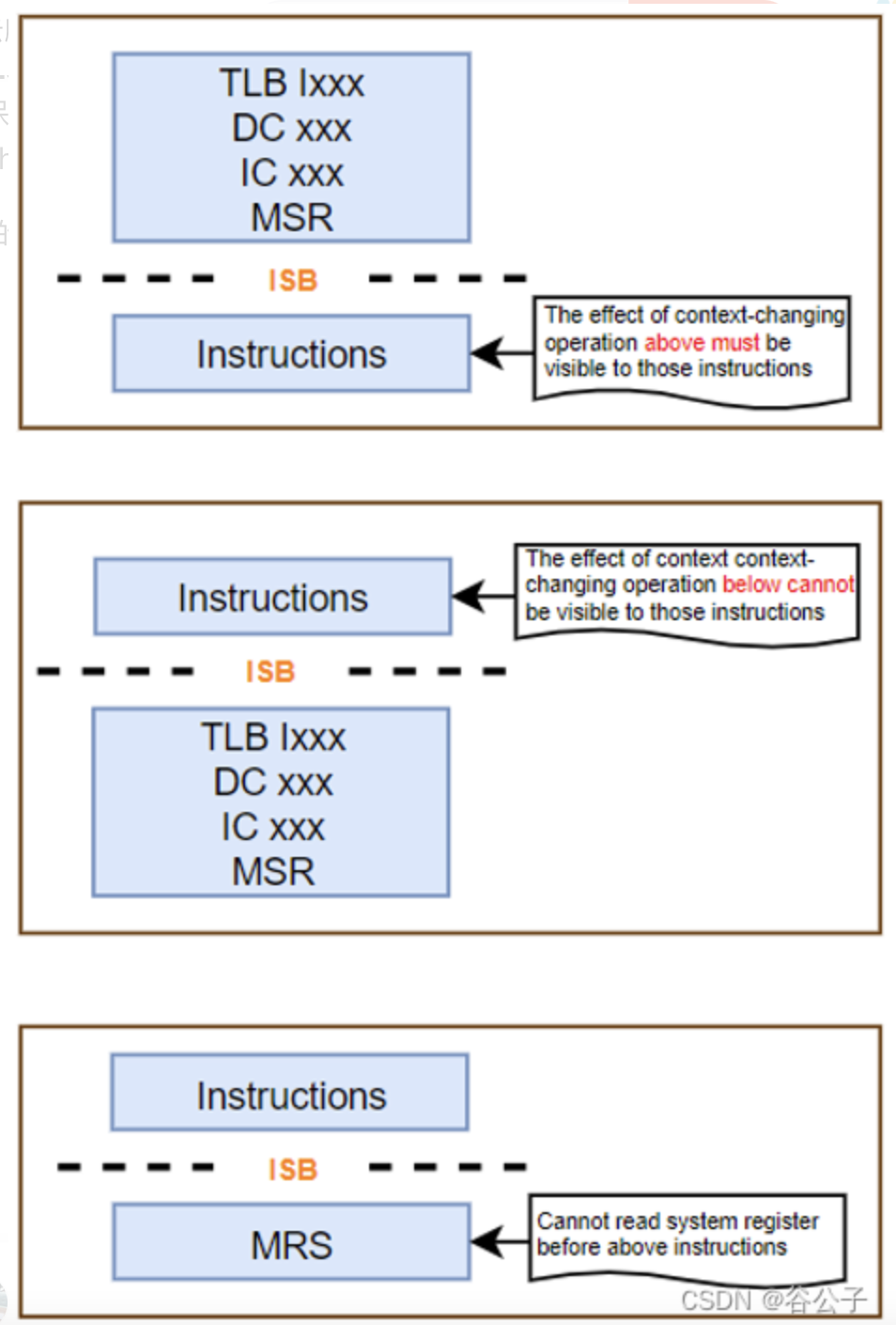

- (flush功劳)可以确保在ISB指令complete后,在program order上处于ISB之后的所有instructions是从cache或memory中重新取出的,而不是core内部可能存在的instruction queue/buffer。

- (CSE功劳)可以确保在ISB之前执行的context-changing operations的效果对ISB指令之后取到的指令是可见。需要插入ISB指令以确保operation的效果对ISB指令之后取到的指令可见的context-changing operation的例子有:Completed cache and TLB maintenance instructions和Changes to System registers。

- (CSE功劳)可以确保在program order上位于ISB指令之后的任何context-changing operations只有在ISB执行完成后才能生效。

- (CSE功劳)可以确保在ISB之后的读system registers指令必须要等ISB结束了,才能读取system register。

"Completed cache and TLB maintenance instructions"指的是completed的才能被ISB保证,如果cache或TLB maintenance instruction还没有completed,那么就算执行ISB也是无法保证这些maintenance instructions的效果对ISB之后的指令可见。因此在执行cache/TLB maintenance instructions之后,通常需要执行DSB来确保它们的completed,这样再执行ISB的时候,就可以确保maintenance instruction被之后指令observer(看到)了。总得instruction sequence应该是这样的:cache/TLB maintenance instructions + DSB + ISB。

"Changes to System registers"指的是在ISB之前所有对system register的更改都必须对ISB之后指令可见,也就是ISB要保证对system register的更改要completed,只有这样才能确保被ISB后续指令可见。因此,这点和上述cache/TLB maintenance instructions的要求还不大一样。

ISB的功能示意图如下:

文章来源:谷公子

推荐阅读

- ARMv8 architecture里的Memory aborts

- Systemverilog覆盖率的合并和计算方式

- PCIe 6.0:在有损HVM通道中使用PAM4实现64GT/s的挑战

- Wi-R 一种全新的通信方式,让你的身体充当媒介!芯片已推出!

- 科普:DDR

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。