A64指令集包括访问system registers编码空间的指令。这些指令有:

- Access to System registers, including the debug registers, that provide system control, and system status information.

- Access to Special-purpose registers such as SPSR_ELx, ELR_ELx, and the equivalent fields of the Process State.

- The cache and TLB maintenance instructions and address translation instructions.

- Barriers and the CLREX instruction.

- Architectural hint instructions.

本文主要想讲讲下第一点和第二点,也就是system registers和special-purpose registers的一些规则。对于这些registers的访问都是使用MSR或MRS来进行的。

// system registers

MSR <System register>, Xt ; Write to System register

MRS Xt, <System register> ; Read from System register

// special-purpose registers

MSR <Special-purpose register>, Xt ; Write to Special-purpose register

MRS Xt, <Special-purpose register> ; Read from Special-purpose registerSystem registers的Reset

Arm architecture里Reset value只应用于具有RW属性的registers和register fields。但是有些特例:

- Some RO registers or fields, including feature ID registers and some status registers or register fields, always return a known value.

- Some RW and RO registers or register fields return status information about the PE. Unless the register description indicates that the value is UNKNOWN on reset, a read of the register immediately after a reset returns valid information.

- Some RW and RO registers and fields are aliases of other registers or fields. In these cases, the reset behavior of the aliased register or field determines the value returned by a read of the register immediately after a reset.

- WO registers that only have an effect on writes do not have meaningful reset values. However, an access to a WO register might affect underlying state, and that state might have a defined reset value.

- IMPLEMENTATION DEFINED registers have IMPLEMENTATION DEFINED reset behavior.

而且ARM architecture里只确保复位后有个稳定的状态,尽量少规定system registers的复位值,大部分的reset value是UNKNOWN的。

System registers synchronization

System registers read

在同1个PE上,对于system registers的read操作与之前instructions在执行上可以是任意的,也就是out of order的关系。除非有以下情况:

Any data dependencies between the instructions, including read-after-read dependencies, are respected. PS:也就是说有dependency关系的话,order关系还是要硬件遵循的。

The reads to the register do not occur earlier than the most recent Context synchronization event to its architectural position in the instruction stream. PS:因此CSE经常用于确保system registers的作用时间点。

System registers write

对System registers的direct write操作有两点需要注意:

- software需要有synchronization,才能确保写system register的效果对后续instruction可见或有影响。这个synchronization其实就是explicit synchronization (CSE产生的)。有些特例情况下不需要synchronization,它们是在硬件上会自动帮忙做好order的:

- All direct writes to the same register, that use the same encoding for that register, are guaranteed to occur in program order relative to each other.

- All direct writes to a register occur in program order with respect to all direct reads to the same register using the same encoding.

- Any System register access that an Arm Architecture Specification or equivalent specification defines as not requiring synchronization.

- When FEAT_BRBE is implemented, execution of BRB INJ does not require explicit synchronization to use the result of direct writes to the Branch record injection data registers in program order before BRB INJ.

- 对system registers的写操作不会影响到program order之前的任何instruction。

总结上述对system registers的读和写操作如下4点:

- 对相同system register操作的instruction在硬件上自然会确保order,它们有data-dependency,比如:RAW,RAR,WAR,WAW。

- 对于system registers的读操作,在没有data dependency或CSE的限制下,可以和其它instructions乱序执行。

- 对于system registers的写操作,在任何情况下都不能影响program order之前的任何instruction。

- CSE可以确保读system register指令在CSE完成后,才能进行读操作。CSE也可以确保写system register指令的效果在CSE完成后,对后续任何instruction都可见。

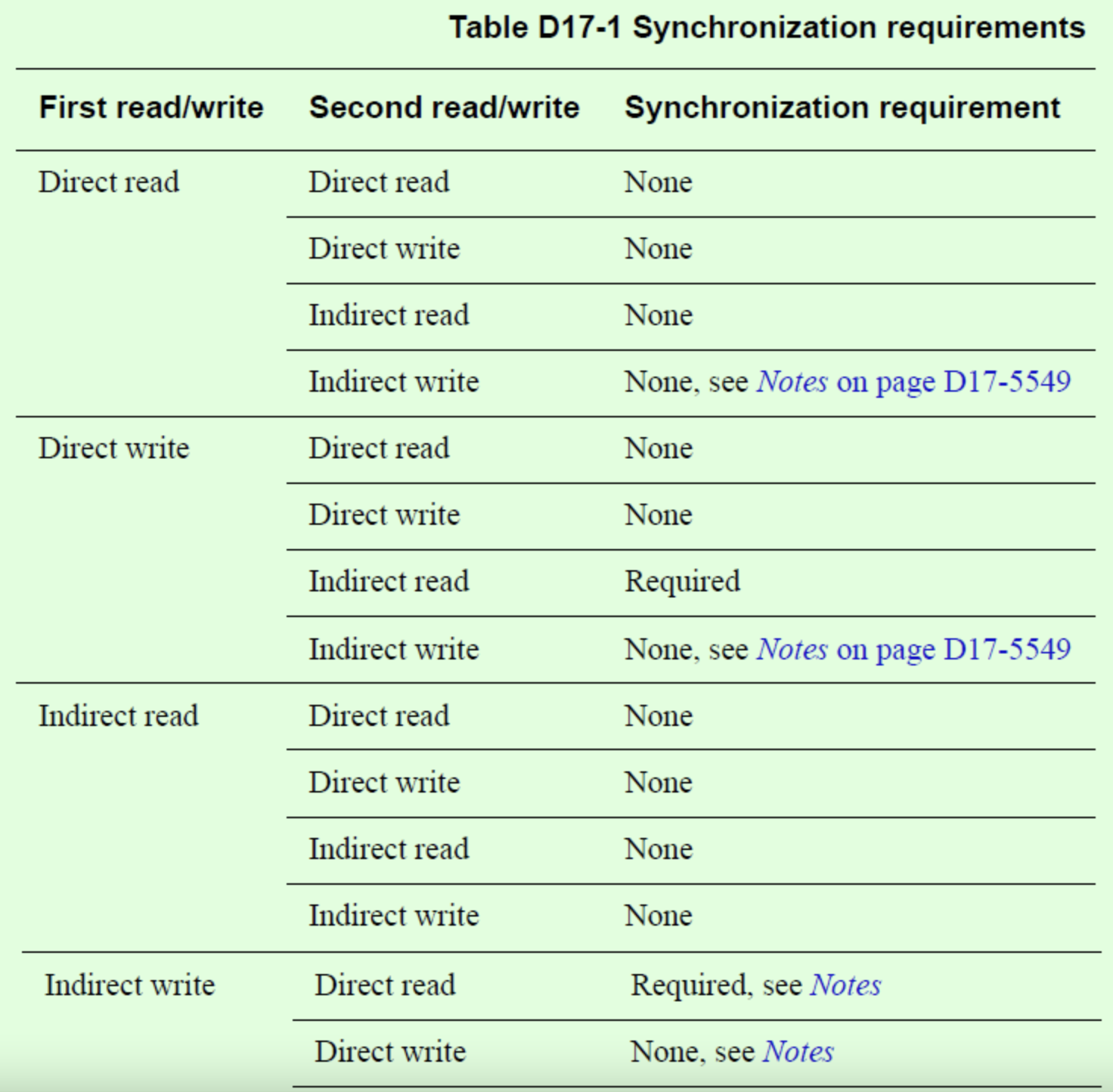

上述讲的system register读和写都是direct的,也就是是MRS和MSR产生的操作。在Arm architecture中还有indirect的,可分为indirect read和indirect write。在Arm architecture中描述了对于两个连续的read或者write访问同一个register来说,是否需要synchronization。其中read或write访问的顺序为:

- Program order, in the event that both the reads or writes are caused by an instruction executed on this PE, other than one caused by a memory access by this PE.

- The order of arrival of asynchronous reads and writes at the PE relative to the execution of instructions that cause reads or writes.

The order of arrival of asynchronous reads and writes at the PE relative to each other.

从表中可以看出只有(direct write->indirect read), (indirect read->direct read), (indirect write->direct read)需要synchronization才能保证order,其余的话,硬件会自动做好order的。

Special-purpose registers

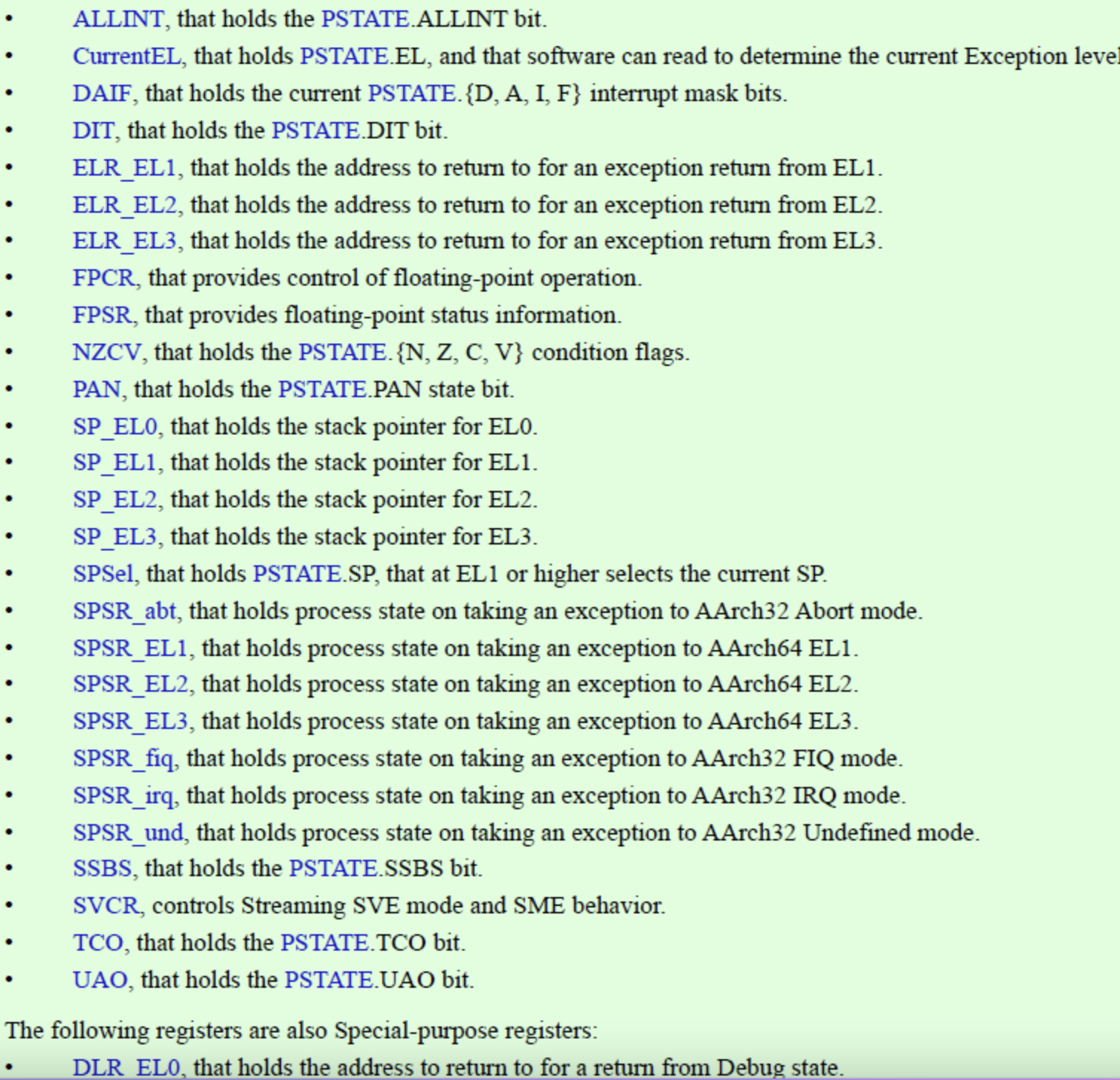

special-purpose registers的一个重要特征是:对special-purpose register的所有direct和indirect的read或者write访问都按照相对于其它instructions的program order来进行,不需要任何explicit synchronization。也就是说不需要任何的ISB,就可以确保对special-purpose registers的读写instructions与其它指令之间保持顺序执行的。

Special-purpose registers有如下这些,其余大部分都是system registers的。

文章来源:谷公子

推荐阅读

- ARM上下文同步事件和指令同步障碍物

- ARMv8 architecture里的Memory aborts

- Systemverilog覆盖率的合并和计算方式

- PCIe 6.0:在有损HVM通道中使用PAM4实现64GT/s的挑战

- Wi-R 一种全新的通信方式,让你的身体充当媒介!芯片已推出!

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。