早上起来看到朋友圈被GPT 4.0 刷屏了。小编登陆open AI 尝试了一把,结果再次刷新小编三观!

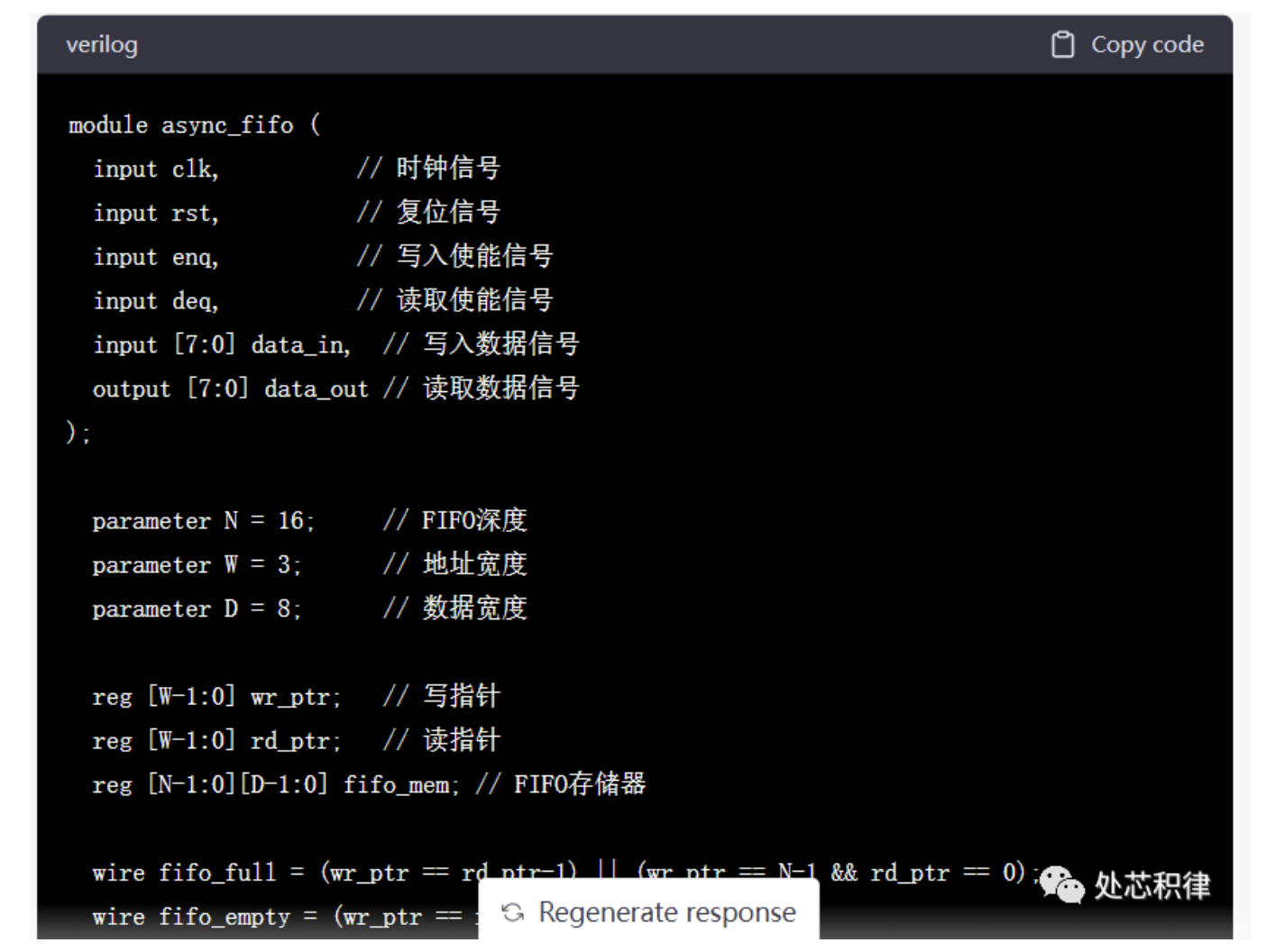

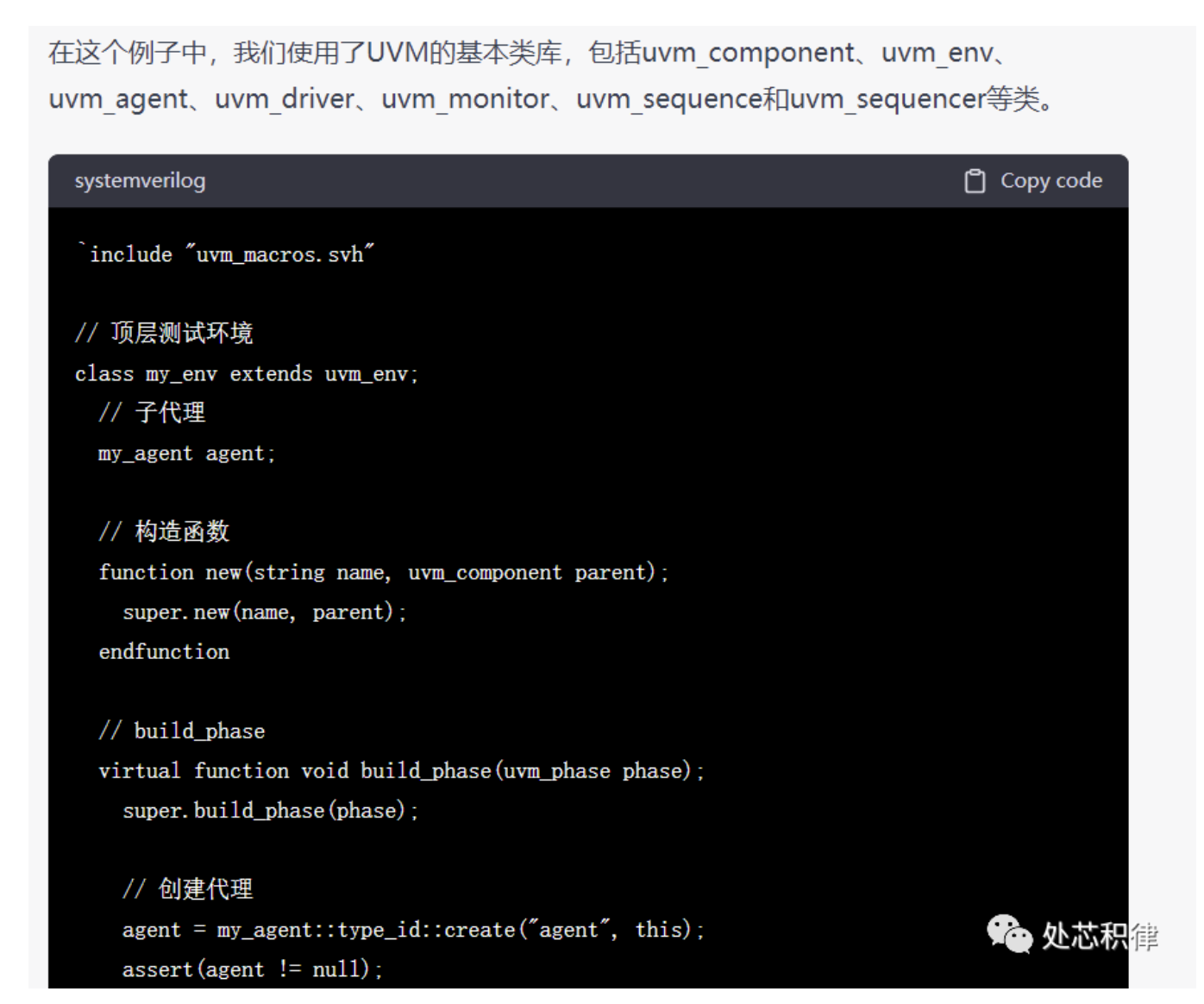

前段时间我们让GPT写一些简单的代码,GPT比较容易实现,比如我们上次文章提到的 异步fifo以及写一些简单的UVM 环境。

异步FIFO的代码

UVM验证环境的代码

但是对于一些复杂的场景,那个时候还不能完成,比如提取testplan等。

这次我们测试一下看看能不能实现一些复杂场景的开发。

写脚本

1. 让GPT写段脚本。从excel 表格直接生成 register model的脚本。

GPT可以实现。

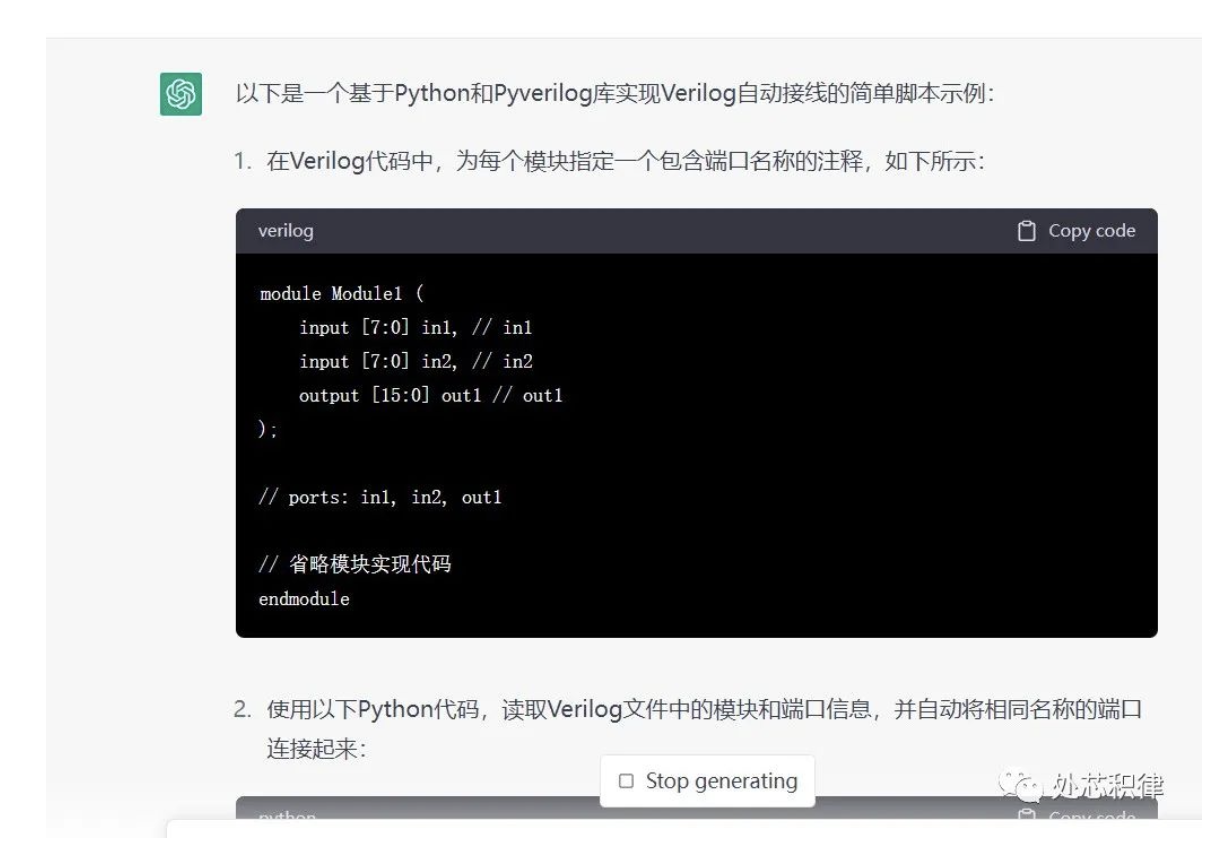

2. 再写个更复杂点的,让GPT提供一套用verilog自动接线的python脚本。

GPT可以实现。

3. 写一套regression 并收集仿真状态的脚本

GPT可以实现。

结论:GPT基本可以胜任写脚本的工作。

写模块

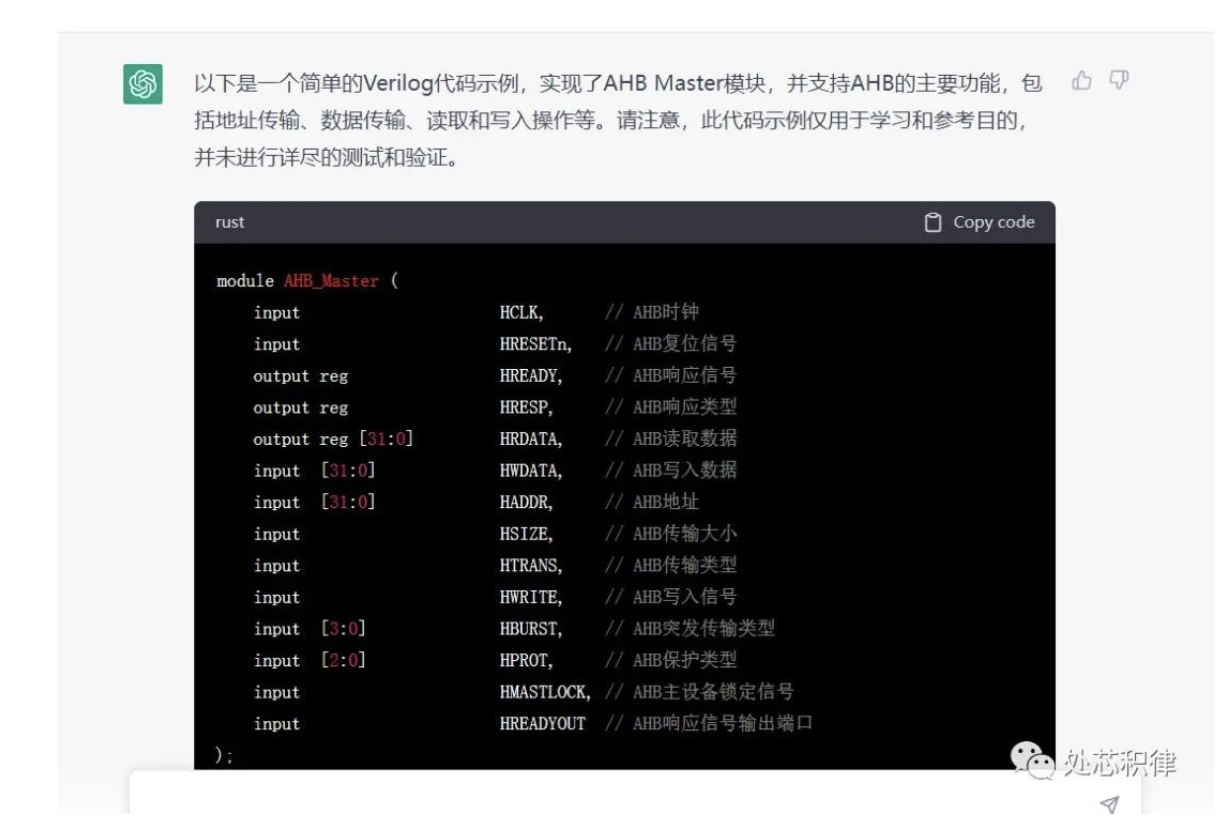

1. 写一个AHB Master 模块

GPT可以实现。

- 写一个AXI Master 模块

GPT可以实现。但是实现的比较简单。

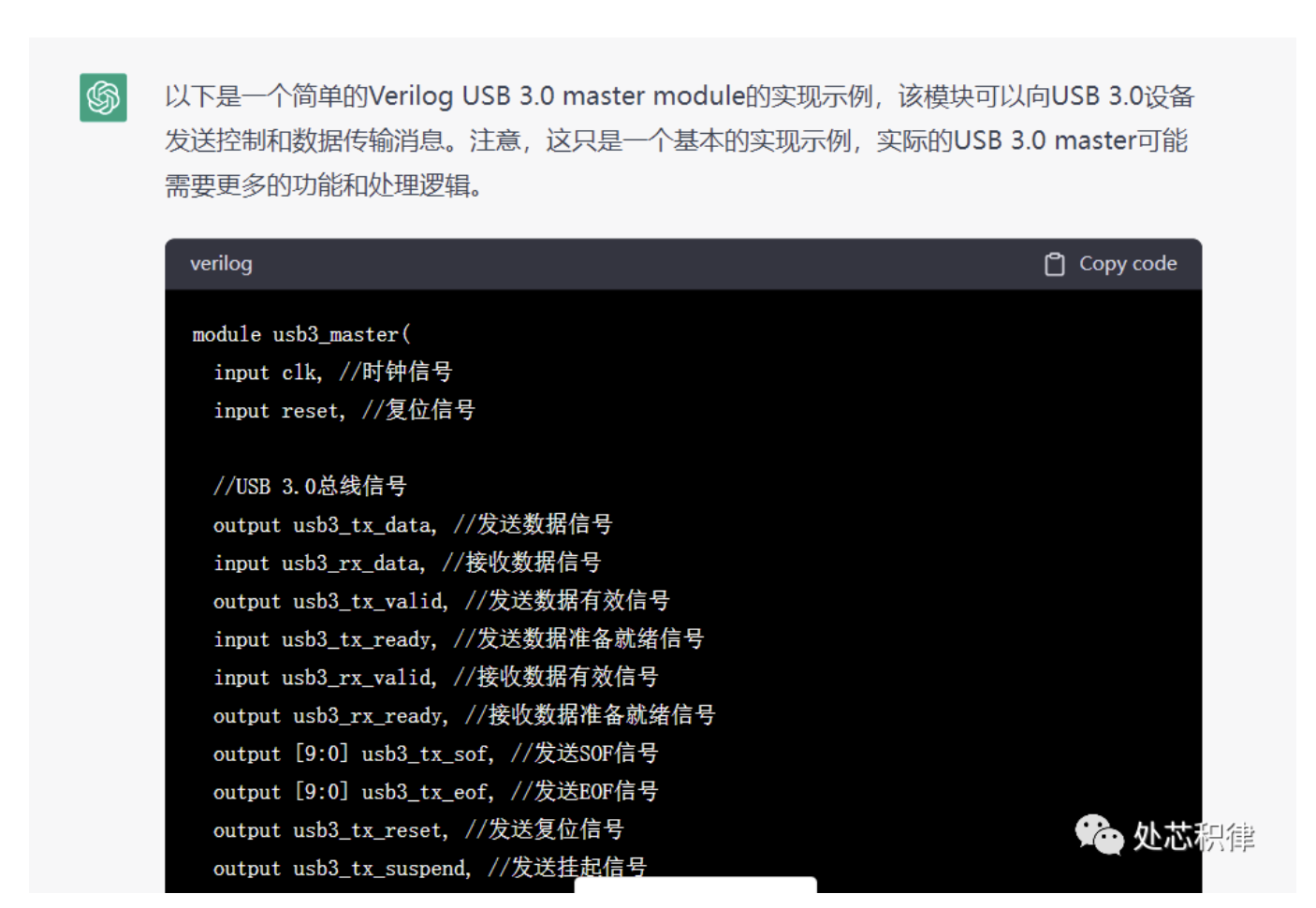

3. 用Verilog 实现一个USB3.0 master 模块

GPT可以实现。但是实现的比较简单。

结论:GPT现在可以胜任部分写设计的工作

写VIP

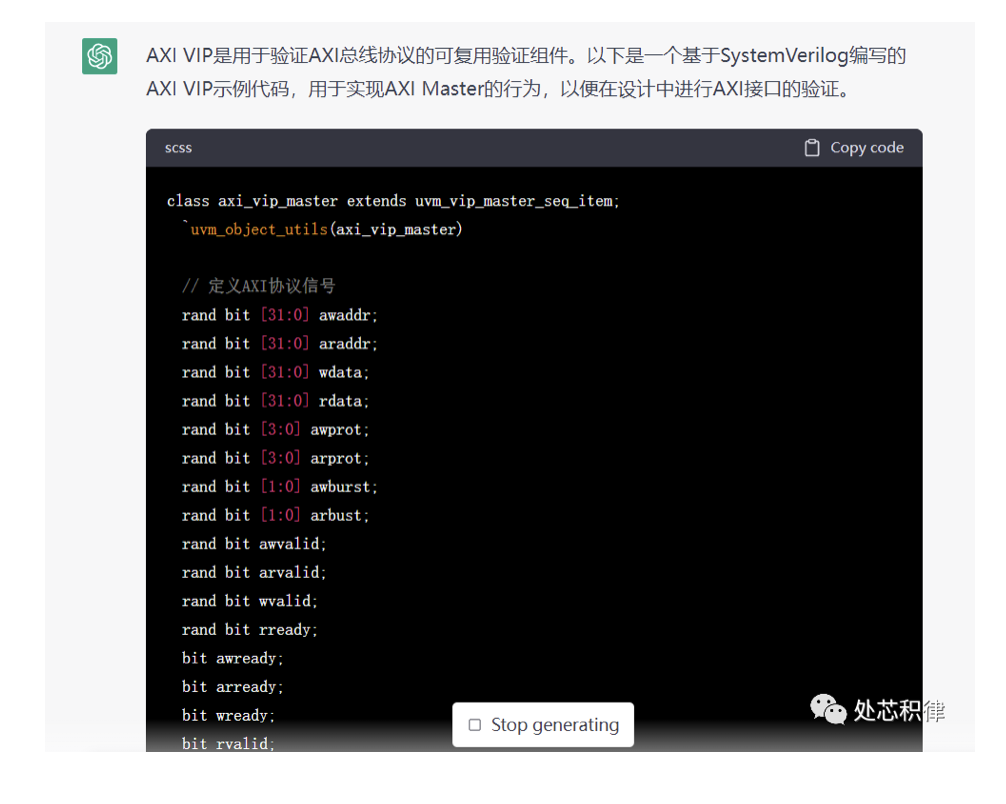

1. 写一个AXI的VIP

GPT可以实现。但是实现的比较简单。

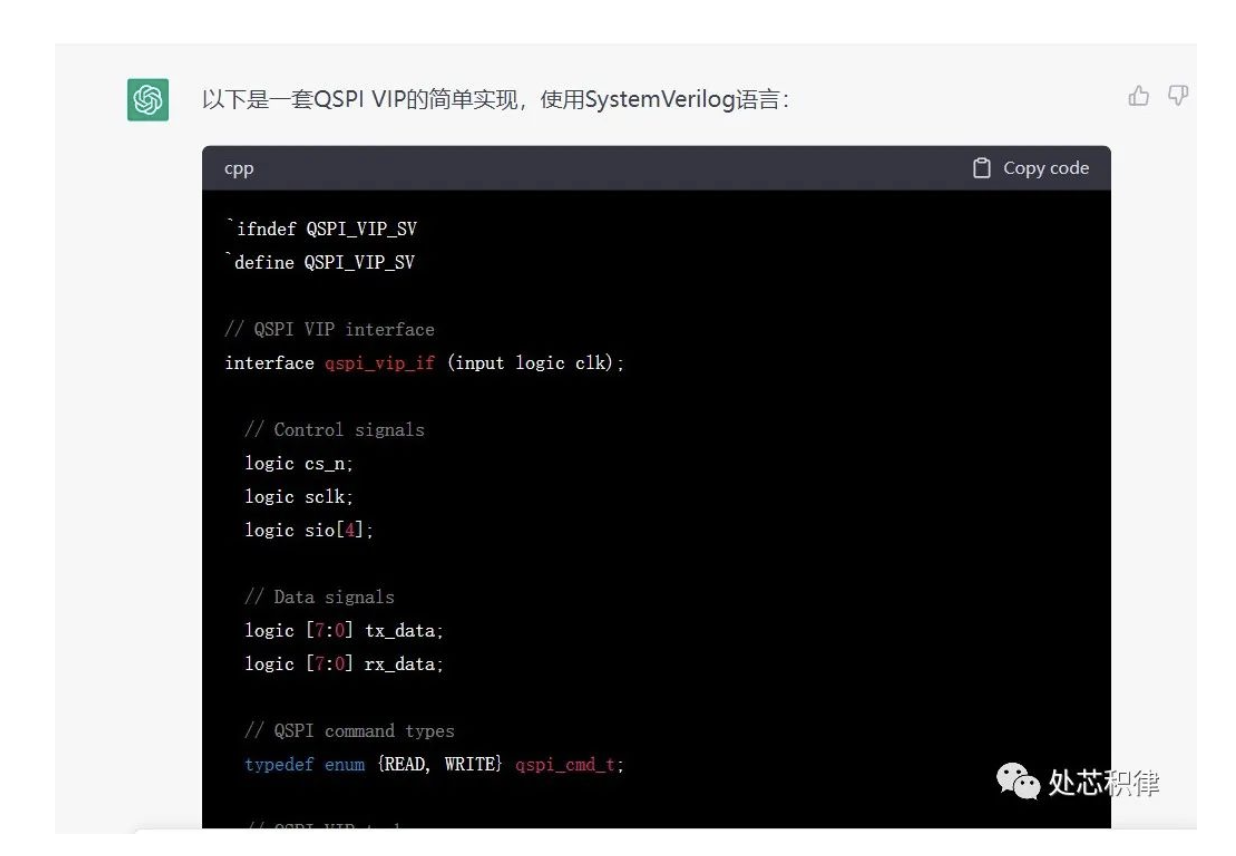

2. 写一个QSPI的VIP

实现起来非常轻松。

结论:GPT现在可以胜任写一些VIP的工作。

提取验证计划

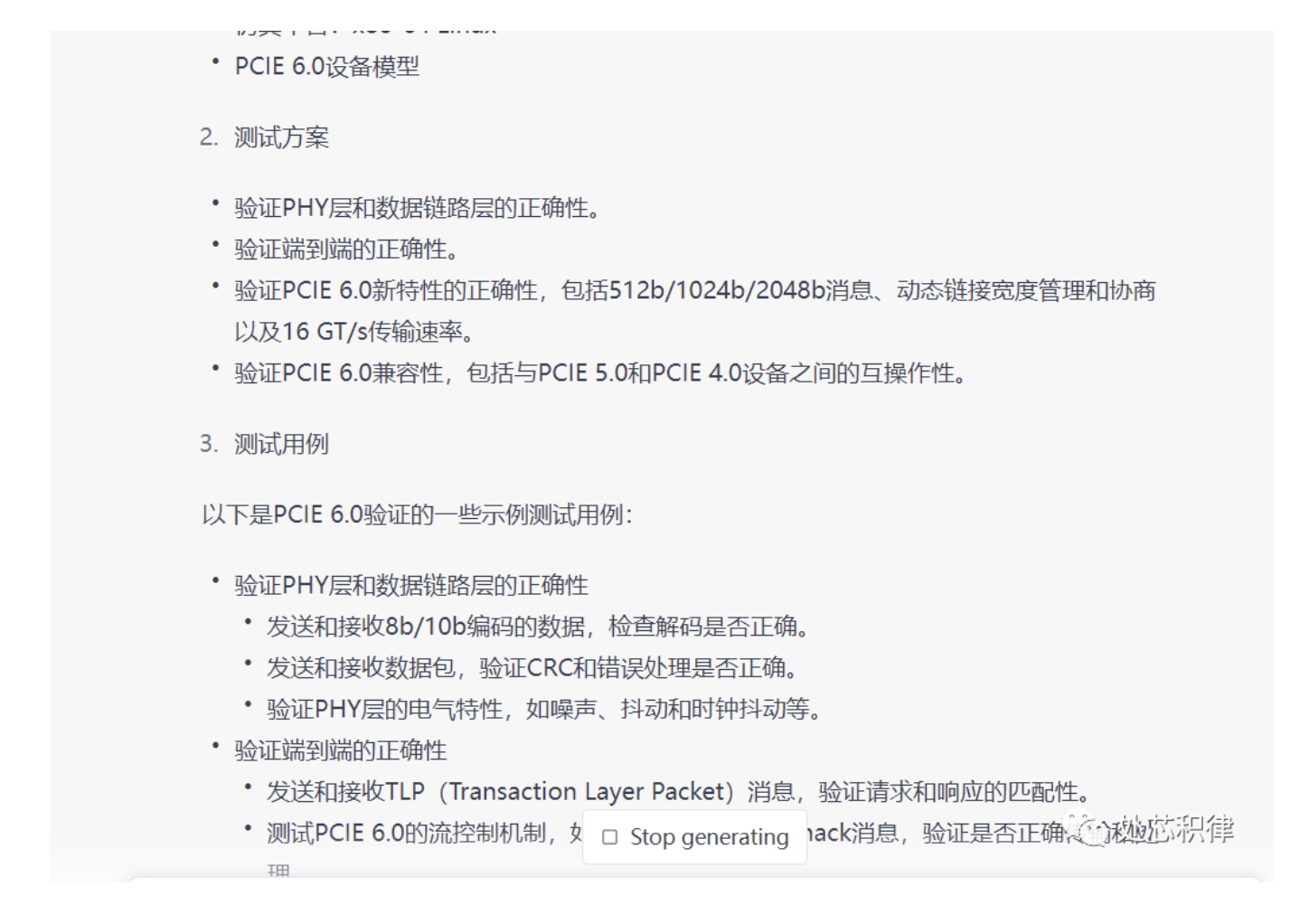

1. 提供一套PCIE 6.0的验证计划

GPT可以提供出来。

有人说这种协议都有,网上搜搜都能找到了,那我们给GPT一段文字,让他提取验证计划。

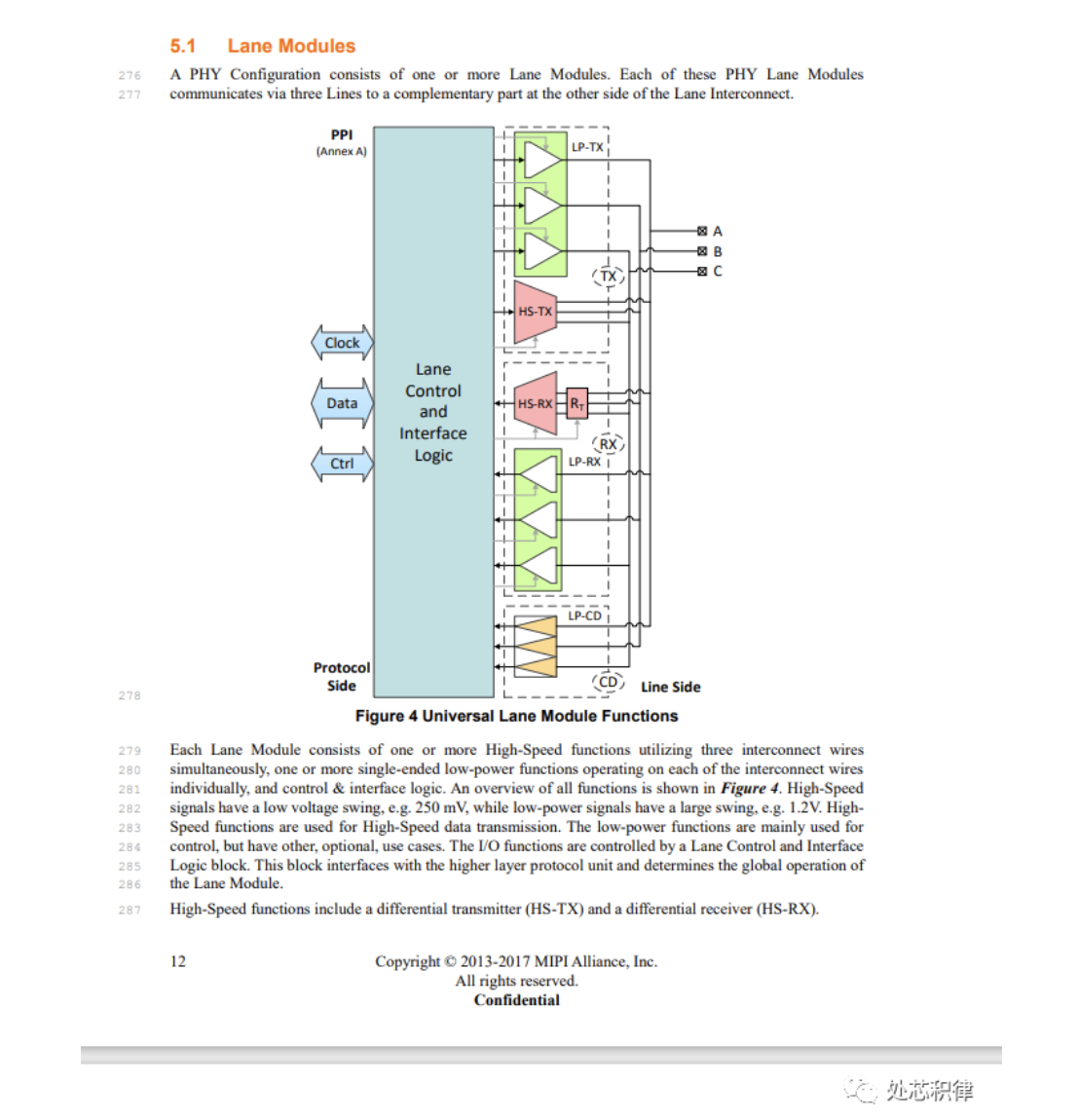

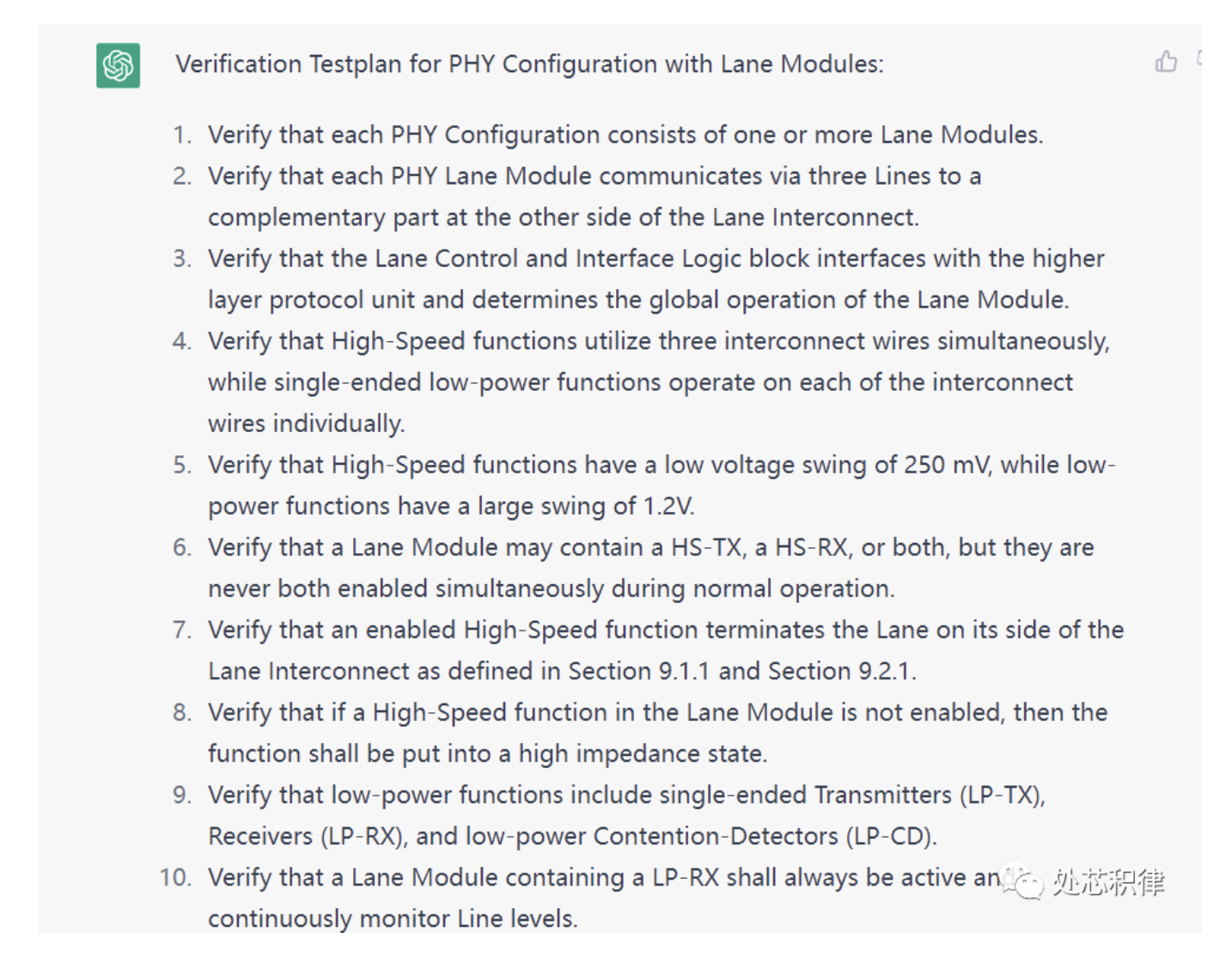

2. 我们摘取了phy spec上的一段话,让GPT根据这段话提供的testplan。

虽然有些地方不是太准确,但总体还可以。

结论:GPT现在可以胜任写一些提取testplan的工作。

总结

当前的GPT在芯片设计和验证中展现出超凡的能力。通过上述的测试,我们发现无论是脚本,环境搭建,模块设计,还是VIP设计,验证计划的提取,GPT都能参与其中。在其他一些芯片的开发流程中,相信GPT也会展示过人的表现。

GPT的进化速度也非常快,可以预见在不久的将来上述的事情会被GPT取代。

这对ICer是好事还是坏事呢?

作者:梨果爱秋天

文章来源:处芯积律

推荐阅读

- 搞芯片不懂cell别乱用!看看Vt cell都是啥?

- ISSCC IC设计论文赏析:关于无线充电、汽车网关SoC

- 智能EDA浪潮即将来袭,ChatGPT如何助力设计芯片

- 用人工智能设计芯片及对IC设计就业市场的影响

- 行业前瞻,神奇的忆阻器

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。