今天这期小编将继续与大家一起学习DFT的相关知识和流程代码,在开始之前,先解决一下上期DFT 学习的章节最后留下的问题—DFT工程师在收敛时序timing的时候经常遇到的hold的问题,即不同时钟 域的两个SDFF(扫描单元的SI端hold违例问题。

首先要明确为什么会出现这样的违例,实际上在后端APR阶段,通常不会对两个不同时钟域用于DFT测试的Sink点进行Skew上的Balance,也就是说不会去做树,同时DFT的时钟的频率又相对较慢, 通常为10~50MHZ,因此两个跨时钟域的SDFF之间的skew可能在时钟prograted后会达到十几甚至几 十纳秒,这个时候就没必要傻乎乎的跑PT后去插Buffer/INV硬修,一般有经验的DFT工程师,都会选择 在前一级的Reg的Q端后接一个相同时钟的Latch来修hold Timing Violation,这种办法虽然会牺牲一 些面积,但是从本质上说其实是通过以下原理去修hold的:1.通过Latch可以借半个周期的margin ;2. 可以改变timing check的时钟发射接收触发前后沿的相对位置以及时序检查方式。实际上这种接Latch 修hold的方式不仅可以用在DFT SCAN的SDFF中,正常修hold做ECO的时候也有使用。

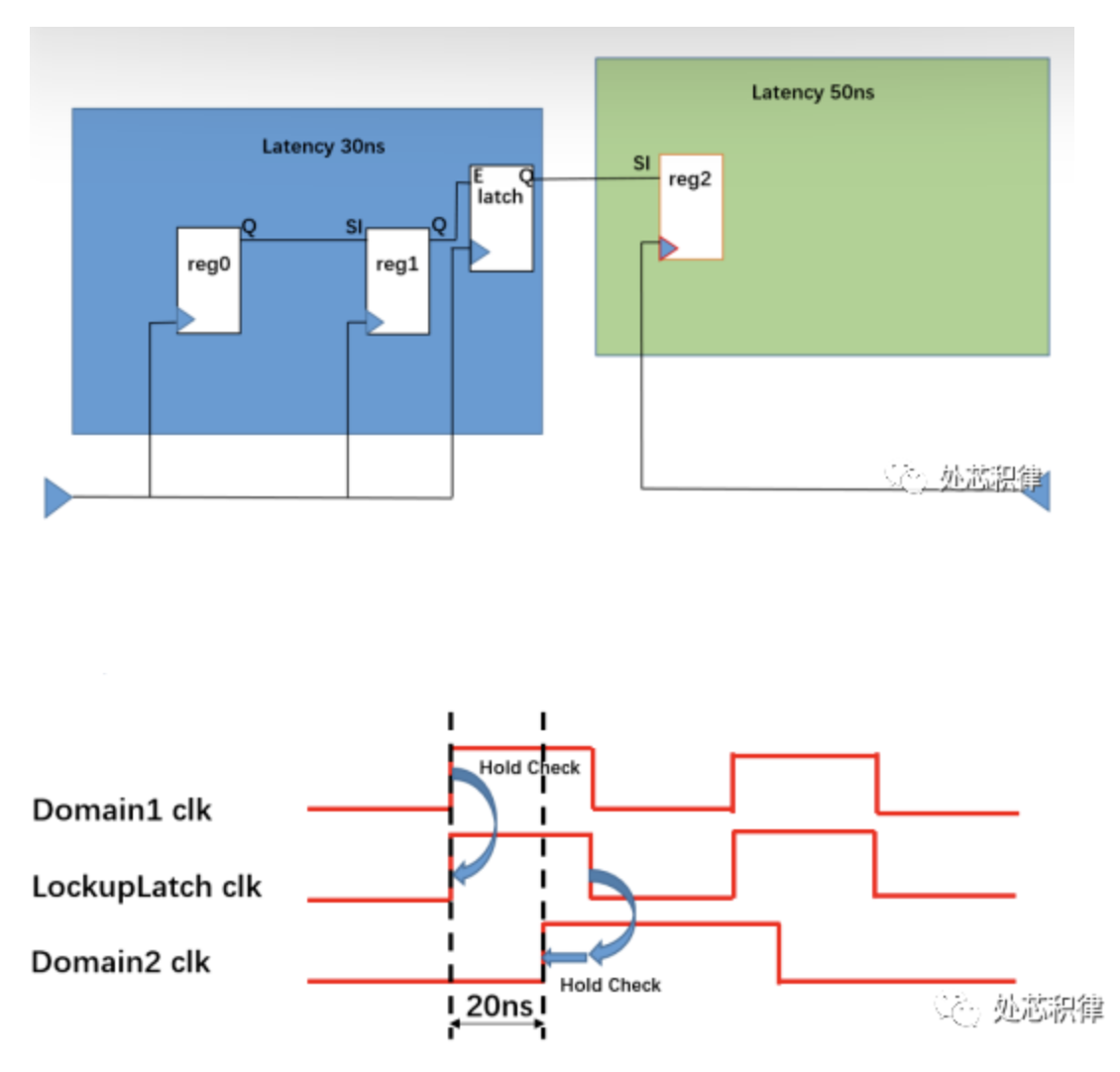

图1 上图为两个跨时钟域的SDFF的Reg2Reg Path ;下图为Reg1 Latch Reg2的时钟信号的有效沿 检查。

从图一的下图不难得出,原本Domain1clock和Domain2clock的Skew比较大,导致launch clk latency加上data path min delay都达不到capture clk delay加上hold time,而lockup latch的加 入,实际上将timing check分成了两部分,一部分是Reg2Latch,一部分是Latch2Reg,对Reg2Latch 这条Path来说,由于是同一个时钟域,hold检查在同一周期的同一时钟沿,在靠的较近的情况下几乎没 有skew,hold很好满足;而对Latch2Reg这条Path来说,Latch可以借半个周期,可以说是近乎天然满 足hold,这样一来跨时钟域的SDFF的时序问题就得到了有效的解决。

解决完上期的遗留问题,让小编来介绍一下DFT工程师在日常工作当中必须掌握的工作技能以及相关知识,其中包括SCAN CHAIN的添加以及配置,MBIST电路的生成以及配置。

首先来介绍一个DFT工程师在日常的工作的工作流程是怎么样的,可以大致分为以下六步骤:

1.实现 测试功能判断,开销判断,熟悉并测试时钟架构;

2.插入BIST自测试电路;

3.DFF替换为扫描单元 SDFF,并将链串起来,串起来后压缩组合逻辑;

4.边界扫描链(用来测试Module),其中包括生成 JTAG电路,扫描网络以及接口,生成JTAG TAP Controller;

5.将期间生成的自动向量收集,将仿真文件 收集跑仿真,综合过formal;

6.debug,也是DFT工程师的日常。

扫描链的配置与压缩

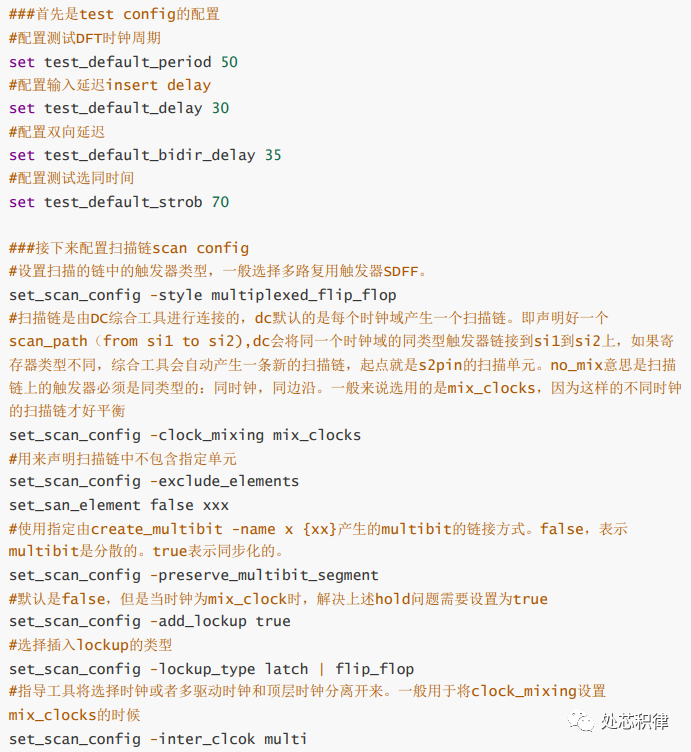

实际上扫描链的配置主要包括test config 以及 scan config,配置完后综合会将扫描网络电路生 成在网表中,一般来说扫描链不止一条。

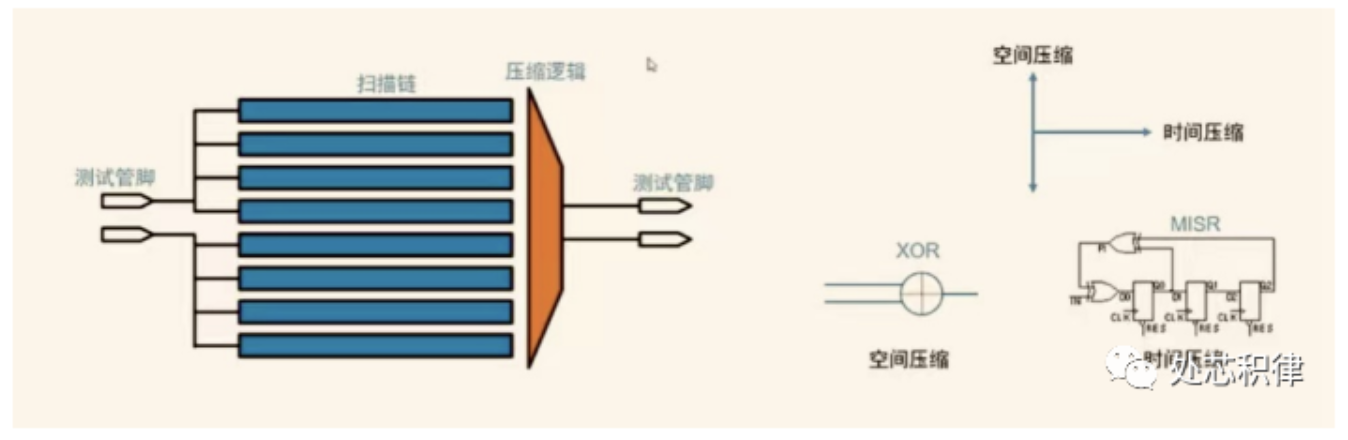

压缩逻辑就是扫描链的最后一个扫描单元DFF/Q端到Scan out Pin的data path,测试pin要尽可能 少,压缩可以到几百倍。

压缩分为空间压缩和时间压缩,时间压缩(MISR)就是增加拍数,进而增加测试向量的时间长 度,来降低扫描数据的容错率,比如2000bit长度的扫描链。

MBIST(Memory-Build-in-self-test自测试)

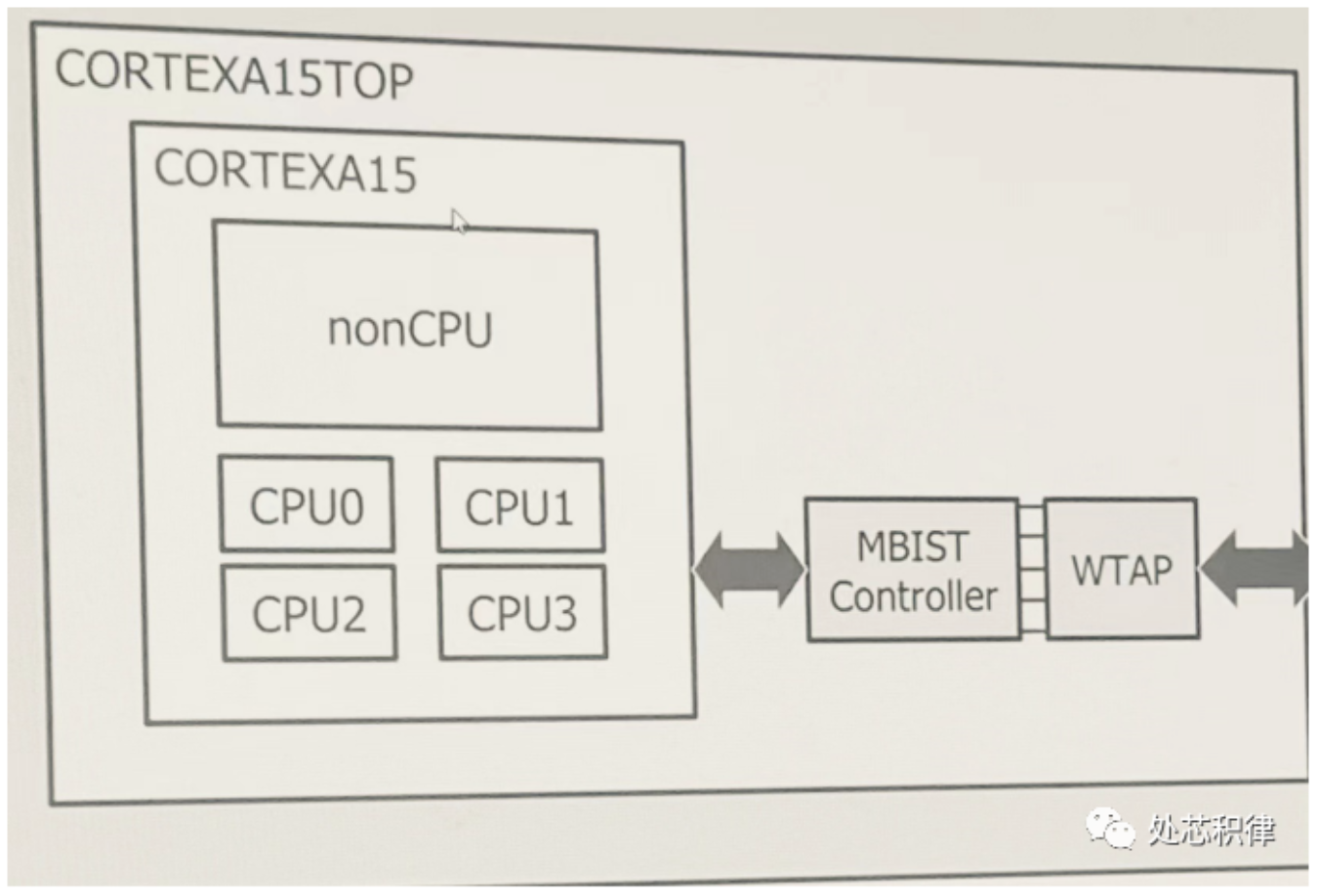

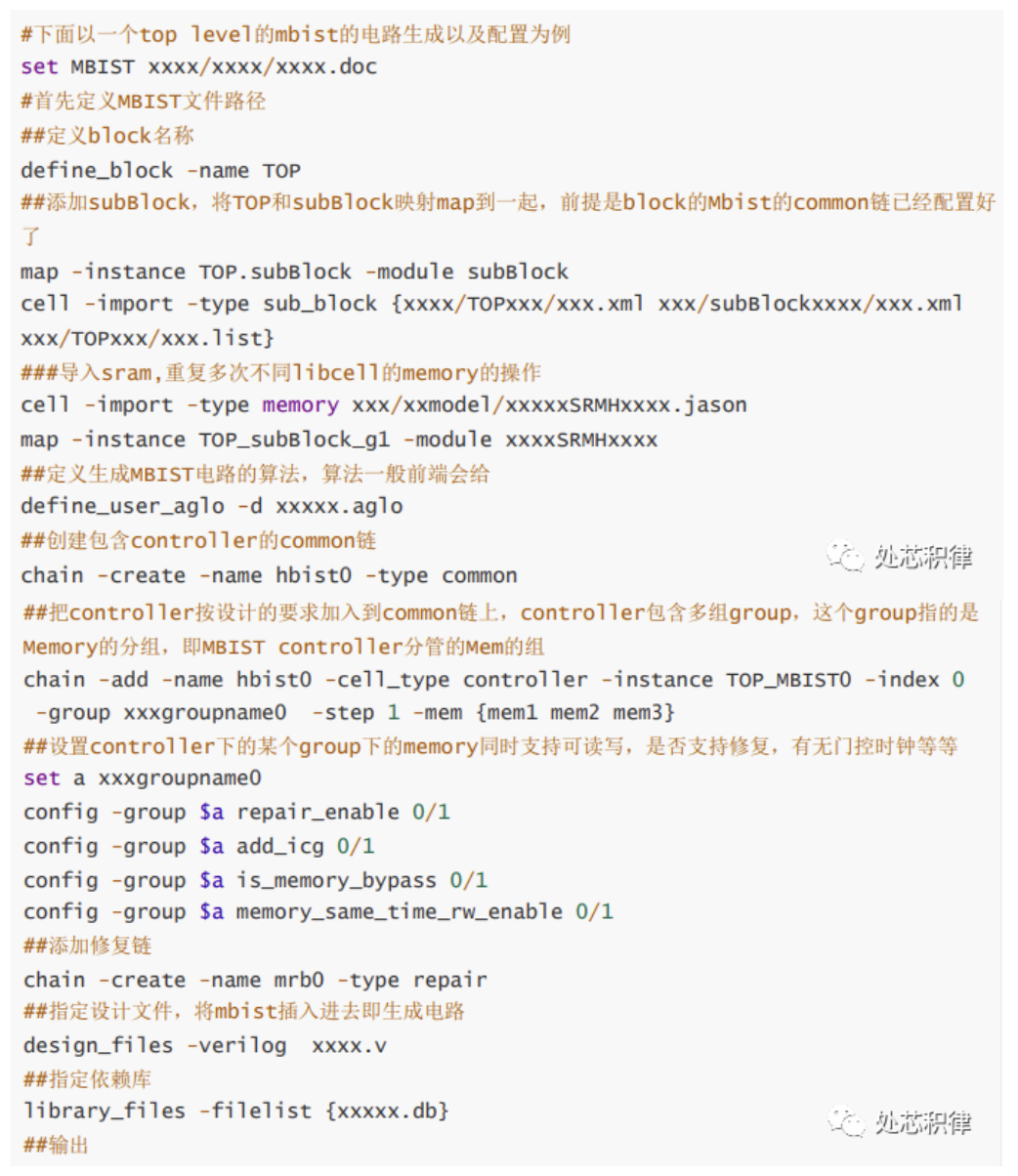

实际上在日常生产当中,MEM是在设计当中最常见的IP,人们也常常担心MEM在芯片内部工作不 正常或者坏掉,这样可以及时将备用的MEM顶替上去,而MBIST是由Controller以及BIST电路组 成,也是由Pin接口到controller等多级fanout,将Controller按group放在common链上,同时还 要考虑顶层TOP和block的之间common链的连接,再对Mbist上包含Mbist Controller的Common 链进行config 配置。

实际上Mbist controller通过一组总线(ShareBus)访问内部四个cpu以及noncpu内部的memory, 以实现mbist测试,这种测试方式可以有效的减少对功能时序以及走线资源的冲击;但是测试时间 较长,ALL Mode模式可以模拟出功能最恶劣的功耗的场景。

好了,到这里这期的DFT的ScanChain以及MBIST测试电路的配置以及生成就介绍完毕了,下一期 小编将会结合IEEE1149.5以及1149.6等标准文件来描述下JTAG以及IJTAG是如何对模块/TOP进行边 界扫描测试的,IJTAG相比JTAG又有哪些优势呢?

我是处芯积律,感谢大家阅读!

作者:处芯积律

文章来源:处芯积律

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。