随着CPU的设计的复杂度的增加,如何分析软件代码在CPU上运行的效率(profiling),代码热点和潜在的优化空间变得更困难。Arm CPU构架的PMU提供了一些软件代码/指令在CPU硬件pipeline中运行信息来帮助代码优化。

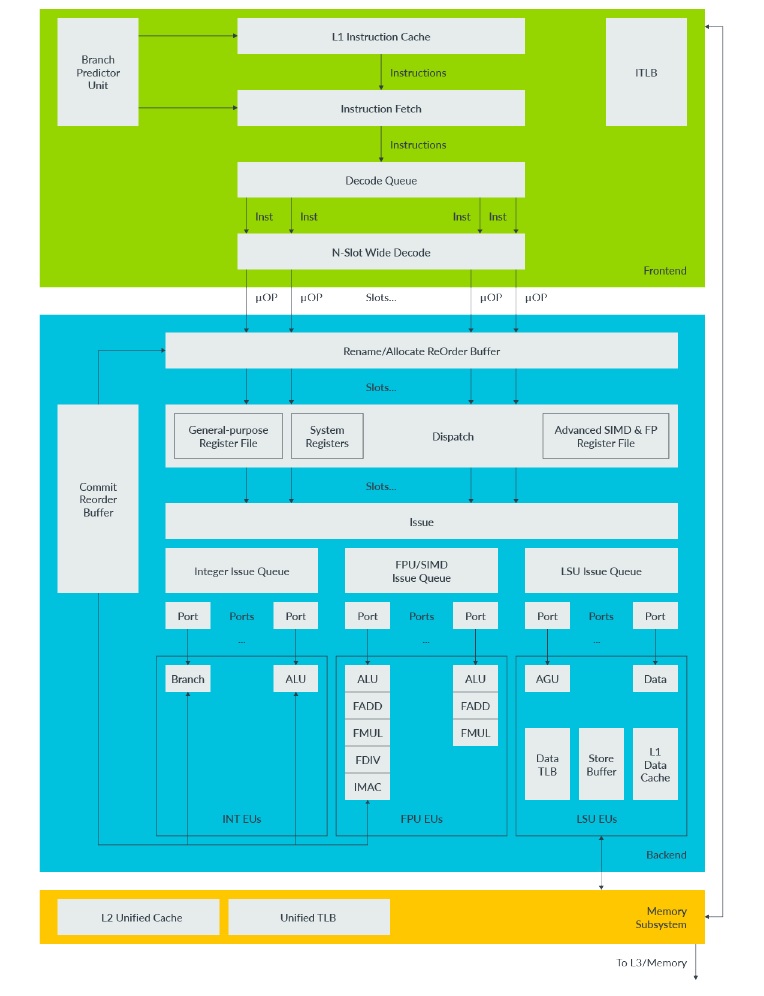

现代CPU pipeline可以大致可以划分为Front End和 Back End以解耦指令Fetch/Decode/Dispatch和指令issue/execution。

例如这个white paper中给出的v1的CPU框图:

有些地方把Fetch/Decode/Renaming/Dispatch划分为Front End, Issue/execution/commit/Retire划分为Back End。

PMU在Armv7的时候就已经存在,只是当时只对PMU的编程接口进行了构架定义,对于PMU event的具体包含哪些事件计数并没有一个详尽的定义(只有比较泛的定义,比如L1 cache refill event,有些CPU包含hardware prefetch导致的refill有些CPU则不包含 )。随着CPU的cache level的增加和pipe line更加复杂。随着CPU种类的增加,arm在PMU event的定义上也一直在更新,以提供含义统一的event描述和更全面的event(比如较新的CPU提供Front End和Back End Stall Cycles的PMU event)。

利用PMU进行性能分析时,一般的步骤为:

在分析的过程中,可以利用的PMU event来分析cache efficiency,TLB efficiency,branch predication efficiency, bus access等。

Arm也提供了一个Topdown PMU分析工具(利用perf tools)来采集和分析PMU数据。这个工具可以在 Telemetry Solution / Telemetry Solution · GitLab (arm.com) https://gitlab.arm.com/teleme... 下载。它是一个python脚本,收集应用程序/系统运行的的PMU event,再通过一些预定好的Metrics计算ratio(如cache miss ratio)等。

它也提供了一些 test cases (/tools/ustress)来演示这个工具的使用。它可以得到如下信息:

因为对PMU event的理解是很micro architecture相关的,正确理解这些数据的意义还是需要参考具体CPU的PMU解释文档(有些数据可能本非字面上的含义)。

下面列出一些非常有用的文档:

Arm Neoverse V1 Performance Analysis Methodology whitepaper

https://armkeil.blob.core.win...

Arm Neoverse N1 Performance Analysis Methodology White paper

https://www.arm.com/-/media/F...

Arm Neoverse N1 PMU Guide

https://developer.arm.com/doc...

Arm Neoverse N2 PMU Guide

https://developer.arm.com/doc...