要讲清楚Orin系列的底层软件开发,就不得不从其高级体系架构上进行分析。从前文中设计的整体架构上不难返现,Orin体系架构设计的标准配套是外置的SMCU(一般推荐用Aurix TC397),以此整体设计的域控架构所包含的软件组件模块如下:

上图是一个高级体系结构图,显示了NVIDIA DRIVE®操作系统版本中NvMCU_SwModules提供的不同功能,以及客户开发的SWC的静态体系结构。

其中位于RTE以下的底层驱动控制部分包括MCU对Orin的电源管理NvMCU_Orin PwrCtrl、MCU对Orin的内部监控NvMCU_IST Mgr、MCU的驱动链配置NvMCU_Boot ChainCfg、MCU的故障转移处理模块MCU_FOH等。位于RTE以上的部分包括平台电源管理模块SW_PltfmPwrMngr所映射的软件系统状态管理SW_SysStateMngr、MCU错误处理MCU_ErrHandler、MCU的风扇管理MCU_SWC_ForFanControl。

以上各个模块中需要重点关注模块如下将从开发的角度进行详述。

NVIDIA Orin引导链配置支持

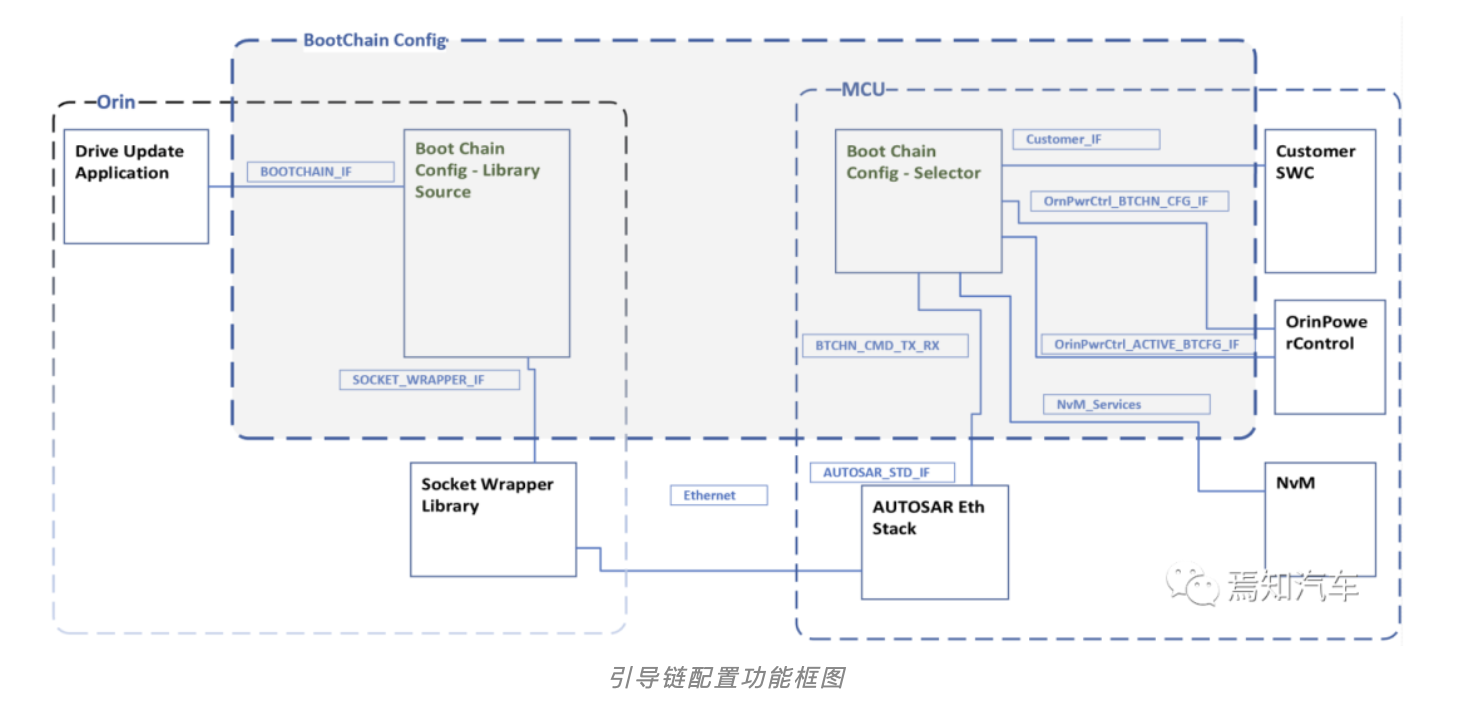

在Orin上运行的NVIDIA DRIVE®Update应用程序的启动需要专门有一些引导链配置项作为支撑,通过维护多个引导链(引导链A、B、C、D)来可靠地管理NVIDIA Orin的软件更新。引导链配置模块有利于基于GPIO的引导链选择,并在选定的引导链中重新启动Orin。它可以被分解为两个子模块引导链配置库源和引导链配置选择器,它们分别在Orin和MCU上运行。

下图概述了系统中引导链配置模块的接口和定位。其目的是实现引导链配置选择、引导链获取、重新启动Orin和MCU,以在选定的引导链中实现功能跳转引导等功能。以上每个功能都需要在MCU上运行驱动链配置选择器的支持才能完成后面的操作。

如上图,在Orin的引导链配置库源Boot Chain Config-Libary Source中可以有效对应的提供API接口给操作系统的套接字通信库SocketWrapperLibary,在MCU端通过标准的Autosar以太网栈接口访问该SocketWrapperLibary,同时MCU端通过驱动链选择器Boot Chain Config-Libary Selector从接口中选择Orin中有效的驱动配置项。

引导链配置选择器依赖于以下模块来执行请求的操作。

- NvM(持久内存):存储引导链配置数据

- 客户SWC:处理重新启动/重置请求

- NVIDIA Orin电源控制:获得活动引导链(A/B/C/D链)

- 这些是引导链配置的Socket资源属性。

整个过程阐述如下:

NVIDIA Orin端上打算使用这些功能的NVIDIA DRIVE更新用户应用程序,并链接到引导链配置库(libmcu_common_if.so)。

引导链配置库(libmcu_common_if.so)制定请求命令,使用Socket Wrapper库通过UDP协议传输和接收命令。并转发到MCU,等待响应命令。当接收到来自MCU的响应命令后,引导链库处理响应并返回给调用方。

在MCU上,首先对UDP数据包进行评估,以检查接收到的数据包是否为引导链请求命令。来自引导链配置选择器的API被调用,从而进一步处理数据包并验证请求命令,对有效请求执行适当的操作,并触发响应命令传输。

片内与片间的通用接口

在NVIDIA DRIVE AGX Orin 平台上,Orin通过以太网使用UDP协议与MCU进行通信,以更新MCU固件及其配置。MCU的配置和固件更新包括:

- 设置/读取网络配置

- 读取MCU固件的当前版本信息

- 读取InfoROM内容(如果硬件支持)

- 需要Flash闪存的MCU固件的兼容性验证

- Flash闪存编程更新和MCU固件生产

- 触发Orin中的低功耗SC7模块

以上所有这些功能都是在通用接口模块下实现的。下图提供了通用接口模块在系统中的定位:

MCU管理NVIDIA DRIVE AGX上SoC的通电、断电、恢复和重置顺序™ 板它支持固件和配置的重新刷新,以及基于GPIO的SoC固件引导链选择。SoC上的用户应用程序,如NVIDIA Drive®Update,与MCU建立有效的通信才可以使用MCU的这些功能。这种通信是通过在SoC上公开的一组通用接口建立的,并通过以太网使用UDP连接到MCU。

通用接口可以提供以下功能:

- 读取InfoROM存储。

- 获取MCU固件的当前版本信息。

- 验证要闪存的MCU固件的兼容性。

- Flash程序更新和生产MCU固件。

- 设置基于GPIO的引导链配置。

- 读取基于GPIO的引导链的当前配置。

- SoC和MCU重启。

- 选择或获取MCU上的网络配置。

- 测试MCU引导链API的处理过程。

- 测试SoC和MCU重启行为。

打算使用这些功能的用户应用程序应链接到公共接口库(libmcu_Common_if.so)。这些功能的可用性取决于内部版本配置,所有功能都可以在标准版本中使用,引导链API仅在安全构建中可用。仅通过VLAN以太网接口支持与MCU的通用接口通信;在初始化时建立VLAN接口。

MCU上的故障处理和监控管理

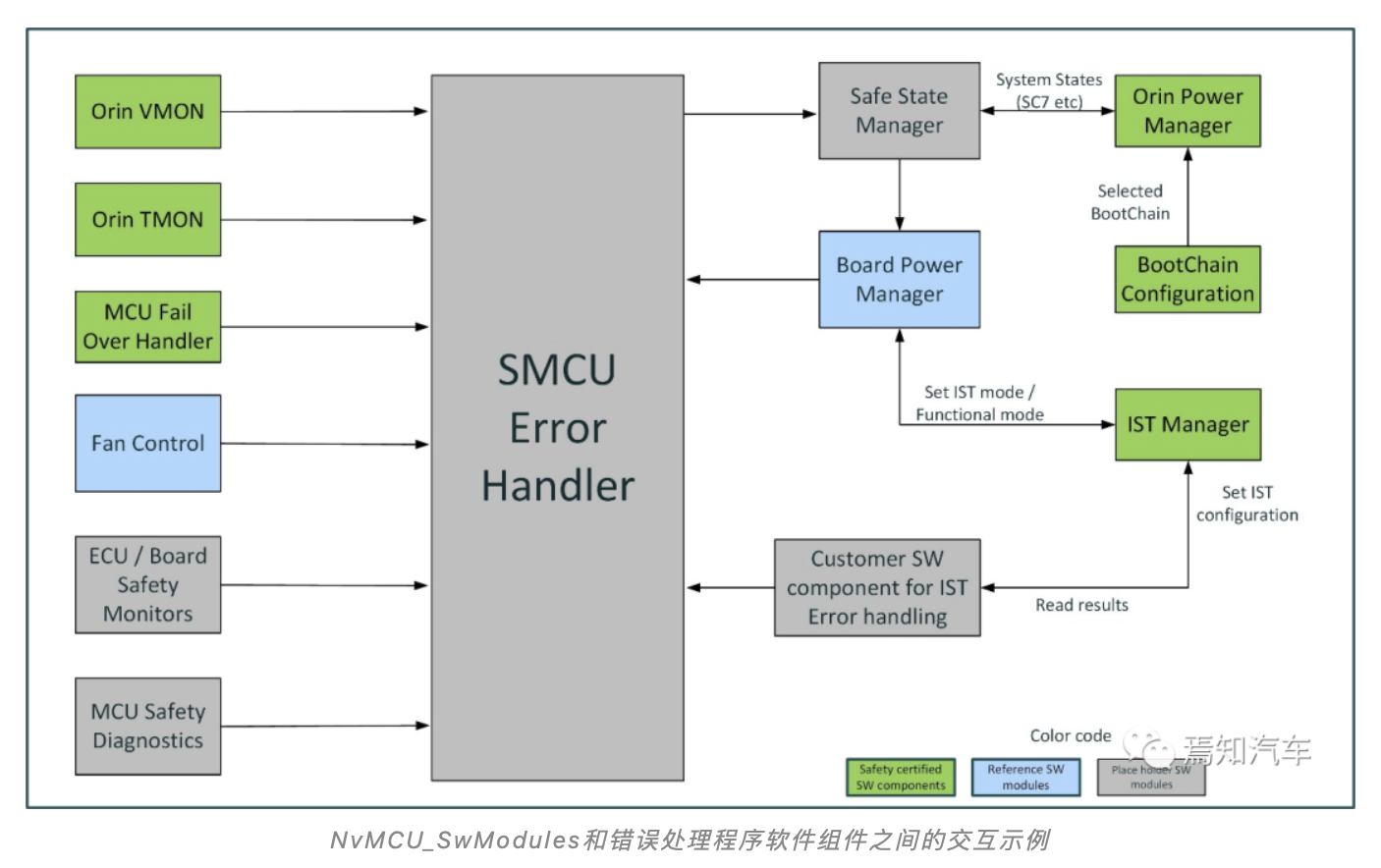

NVIDIA Orin IST管理器提供了一个用于设置IST配置的接口和一个用于读取IST结果的接口。平台电源管理器可以使用这些接口查询是否必须执行Keyon/KeyOff IST,并查询IST是否已完成。此外,管理器还通过打通用户应用程序设置与通信以太网上的IST客户端软件,来实现钥匙打开/关闭Orin IST。在如上引导链驱动过程中,会决定NVIDIA Orin应处于IST模式还是正常模式。通常是通过GPIO断言触发IST,监控NVIDIA Orin上IST的执行,并通过超时检测IST阻塞的场景。IST阻塞是由基于GPT的硬件计时器检测到的,该计时器具有可配置的超时检测逻辑。

下图中显示的绿色方框是经过安全认证的软件组件,蓝色方框是作为参考代码提供的软件组件。灰色方框表示用于评估NvMCU_SwModules软件体系结构的占位符软件组件。开发过程中需要开发参考软件组件和占位符软件模块的完整功能。

以下主题介绍了NvMCU_SwModules和Reference软件组件提供的功能。

NVIDIA DRIVE Orin监视器IST可用于声明断言SOC_ERROR引脚的安全状态,并将检测到的任何错误报告给错误处理程序模块。并通过SPI作为启动器与NVIDIA Orin上的FSI通信,以获取Orin的故障信息。当NVIDIA Orin FSI报告严重错误时,通知MCU错误处理程序模块以启动故障转移处理。MCU会将周期性SPI帧中接收到的错误状态传递给客户应用程序以进行持久存储。MCU还会提供一个接口,用于通知从Orin FSI的系统错误处理程序中接收到的周期性故障状态以及FSI的种子密钥。

common_if_testapp是一个命令行界面,用于验证支持的功能。运行common_if_testapp -h命令会列出受支持的命令并进行简要说明。与-h(help)选项一起列出的附加命令是伪命令,仅用于调试目的。

如下表示了通用接口示例应用程序用法:

#common_if_testapp -mcureset // 重置MCU或整个DRIVE AGX板。

#common_if_testapp -tegrareset x1 // 重置Tegra x1。

#common_if_testapp -set_default_bootchain x1 A //将Tegra x1的默认引导链设置为A。

#common_if_testapp -set_next_bootchain x1 B //为下次重新启动临时设置启动链。

#common_if_testapp -get_default_bootchain x1 //获取x1的Tegra的默认引导链。

#common_if_testapp -get_active_bootchain x1 //获取Tegra x1的活动/当前引导链。

#common_if_testapp -flash_mcu_fw lib/firmware/DRIVE-V6.0.x-P3663-AFW-Aurix-StepB-5.xx.xx.hex //闪存给定的生产固件。

#common_if_testapp -flash_mcu_ufw lib/firmware/DRIVE-V6.x.x-P3663-NV-Aurix-UPDATE-StepB-1.xx.xx.hex //闪存给定的更新固件。

#common_if_testapp -get_fw_version //读取当前运行的固件版本。

#common_if_testapp -get_update_fw_version //读取MCU上闪存的更新固件版本。

#common_if_testapp -get_mcu_hexfile_version lib/firmware/DRIVE-V6.x.x-P3663-NV-Aurix-UPDATE-StepB-1.xx.xx.hex //从十六进制文件的内容中读取其版本。

#common_if_testapp -get_inforom_dump // 从infoROM转储中读取数据。

#common_if_testapp -reboot_mcu_afw //在生产固件模式下重新启动MCU。

#common_if_testapp -reboot_mcu_ufw //在更新固件模式下重新启动MCU。

#common_if_testapp -nw_cfg base //在MCU上选择网络配置。

#common_if_testapp -nw_cfg getStatus //在MCU上获取NW配置。打印MCU网络配置的当前状态。执行SC7进入和退出控制台

在NVIDIA Orin控制台上,可以通过运行common_if_testapp -enter_sc7命令,该命令下可以开始来启动MCU计时器,等待 Orin进入sc7。在NVIDIA Orin控制台上,可以使用以下API函数触发SC7进入:

status = nvdvms_set_vm_state(NVDVMS_SUSPEND);

if (status != NvDvmsSuccess) {

/** Failure case **/

}进入过程是通过监测GPIO -SOC_PWR_REQ来完成的。如果NVIDIA Orin在20秒的超时之前没有进入SC7,MCU将进入错误状态。要从中恢复,需要运行power on或aurix reset命令。要退出,需要在MCU控制台上运行命令exit sc7。

一旦NVIDIA DRIVE Orin™ 进入SC7,引脚SOC_PWR_REQ将被设置为STD_HIGH,MCU将执行SC7进入序列。

从控制台运行安全关机

为了有序关闭Orin芯片, 当触发关机请求时,MCU软件会等待Orin发出的安全关机完成指示(SoC通过GPIO引脚(IST_DONE_N)来实现)。如果在配置的超时(20秒)之前没有接收到指示,MCU软件将继续关闭电源并向用户应用程序报告错误。

启动安全关机过程如下:

在NVIDIA Orin控制台上,运行common_if_testapp -t tegareset命令执行tegareset,或运行common_if _testapp -m curset命令执行Aurix重置。

在NVIDIA Orin控制台上,使用以下API函数触发TCF关闭:

status = nvdvms_set_vm_state(NVDVMS_DEINIT);

if (status != NvDvmsSuccess) {

/** Failure case **/

}MCU上的软件模块NvMCU_BootChainCfg成功接收到请求后,将发送确认信息。该请求将转发给用户应用程序进行进一步仲裁,如果满足先决条件,NvMCU_OrinPwrCtrl将启动对握手GPIO的监控。

一旦设置了握手GPIO,NvMCU_OrinPwrCtrl将关闭Orin模块电源导轨,并按照硬件建议的关机顺序进行操作。

如果在20秒内未设置握手GPIO,NvMCU_OrinPwrCtrl将向用户应用程序报告错误,并继续执行相同的关闭顺序。

总结

本文接续上几个章节内容说明了如何针对英伟达芯片的架构从底层开发角度说明如何从设计链路、底层架构及软件指令角度启动开发。整个阐述过程仍旧是按照之前典型的ORIN+SMCU外置的方式进行架构分析和说明。从详解Orin系列芯片高级软件架构到驱动引导链配置,从片内到片间的底层软件驱动接口配置,再到故障处理运行机制整体解析了如何对NIVIDA芯片进行有效的软件开发,同时考虑上章节中的低功耗模式状态,本文也通过指令设计详细说明了如何进入和退出SC7低功耗。

作者:Jessie

文章来源:焉知汽车

推荐阅读

- 自动驾驶软硬件解耦:理想丰满,现实骨感

- 英伟达系列芯片自动驾驶开发:硬件电源设计

- 低速容错CAN的容错机制介绍

- 智驾系统的设计瓶颈之:电源管理设计中的功能安全和状态机

- 英伟达系列芯片如何用于自动驾驶研发之架构及安全设计(一)

更多汽车电子干货请关注汽车电子与软件专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。