点击上方蓝字关注我们

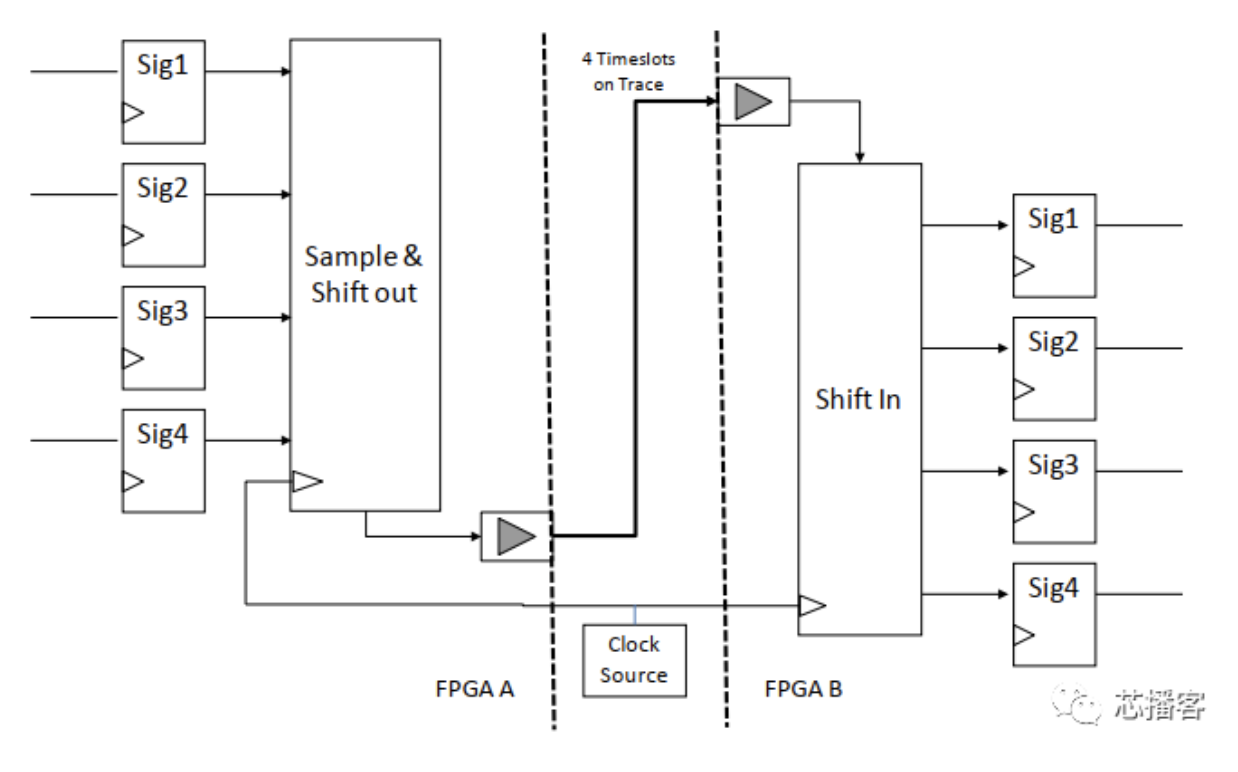

设计中两片FPGA分割边界的数据Sig1、Sig2、Sig3、Sig4……等一大波的信号被并行地加载到传输时钟的上升沿上的移位寄存器中,并用相同的时钟移出。在接收端的FPGA\_B中,移位寄存器对传输时钟上的输入数据进行采样,并与设计并行地提供数据。第一个采样(在这种情况下为sig 4)在移位寄存器输出端从采样时钟边缘可用,但是在该方案的一些版本中可能需要传输时钟的额外边缘,以便在数据被完全移位到目标寄存器之后锁存数据。再次,发送和接收移位器需要启动,然后保持同步。

这种类型的方案非常适合在FPGA间trace迹线上具有比平均传输时间更长的板,因为路径中没有额外的组合延迟,我们可以最大限度地利用传输时钟周期。特别是,如果先前的采样尚未被时钟记录到接收逻辑中,则不可将新数据采样到记录道上。在某些实验室情况下,我们可能会很幸运,但在其他情况下,传输线的轨迹特性或连接中的轻微不连续性可能会使传输不可靠。因此,我们有传输时钟速度的物理上限,如果我们达到了这个上限,那么进一步提高复用率的唯一方法就是降低整个系统的速度。这样做之后,即使使用10:1或更高的多路复用器比率,我们也只需要以更低的时钟速率原型。

作者:Jacky Yu

文章来源:芯播客

推荐阅读

低功耗设计详解(UPF编码篇)

浅谈System Verilog的DPI机制

在芯片研发工作中,你犯过哪些“愚蠢”的错误?

更多FPGA干货请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。